Fターム[5F033NN34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560) | コンタクトホールの大きさ、数 (291)

Fターム[5F033NN34]に分類される特許

281 - 291 / 291

コンタクトホール製造の監視

製造検査のための方法は、半導体基板及び該基板を覆って形成された非導電層を含むウェーハを受け取ることと、それに続いて、該非導電層を貫通して該基板に達するコンタクト開口のエッチングを実行することであって、該コンタクト開口が、該ウェーハ上の検査領域内に予め画定されたテストパターン内に配列されたコンタクト開口から構成される配列を含むこととを含む。電子ビームは、該検査領域を照射するように向けられ、該電子ビームに反応して該基板を流れる試料電流が測定される。該試料電流は、該コンタクト開口の寸法を評価するために分析される。  (もっと読む)

(もっと読む)

半導体装置

【課題】光近接効果に起因するトランジスタのゲート長ばらつきを抑制しうる半導体装置を提供する。

【解決手段】半導体装置は、P型拡散領域,N型拡散領域及び素子分離領域に跨って形成され、拡散領域上に位置するゲート電極部G21a〜G21cと、素子分離領域上に位置するゲート配線部G22a〜G22cとを有する複数のゲートポリシリコン膜G20a〜G20cを備えている。そして、層間絶縁膜を貫通して、ゲート配線部G22a〜G22cに接続されるゲートコンタクトC23a〜C23cと、各ゲートコンタクトC23a〜C23cに接続される配線M21とが設けられている。ゲートコンタクトC23a〜C13cの径Rは、ゲートポリシリコン膜G20のゲート長Lよりも大きい。

(もっと読む)

電源配線構造、該電源配線構造を備えた半導体集積回路、電源配線方法ならびに該電源配線方法を用いる半導体集積回路設計方法

【課題】エレクトロマイグレーションの発生を抑制できる電源配線構造を提供すること。

【解決手段】本電源配線構造は、互いに異なる配線層である第1、第2の電源配線1010,1030を備え、かつ、前記両電源配線1010,1030が互いの交差領域でビア1060により電気的に接続されている電源配線構造であって、前記交差領域から第1の電源配線1010の配線方向1020に第2の電源配線1030が延長されて第3の電源配線1070が構成され、かつ、第1および第3の電源配線1010,1070がビア1060により電気的に接続されている。

(もっと読む)

集積受動電子素子を備えた電子素子およびその製造方法

電子素子(EB)は第1絶縁層(1)を備え、第1絶縁層(1)の上には第1金属層(5)が形成されている。第1絶縁層(1)の中には、導電性構造(2)が集積されている。この導電性構造(2)は、素子(EB)をボンディングおよび/または実装する際に第1絶縁層(1)を機械的に安定させるものであり、受動電子素子として形成されている。  (もっと読む)

(もっと読む)

半導体装置用基板及びその製造方法、電気光学装置用基板、電気光学装置並びに電子機器

【課題】 スタックコンタクトにおける接触抵抗を抑制させる。

【解決手段】 基板と、基板上に設けられた薄膜トランジスタと、該薄膜トランジスタの上層側に設けられた配線と、該配線と薄膜トランジスタの少なくとも半導体層とを層間絶縁する層間絶縁層と、該層間絶縁層に掘られており且つ基板面上で平面的に見て長手状に延びる第1の穴、及び、夫々、第1の穴の底部から層間絶縁層を貫通して半導体層の表面に至り且つ第1の穴の長手方向に沿って配列された複数の第2の穴を含んでおり、配線と半導体層とを層間絶縁層を介して接続するコンタクトホールとを備える。

(もっと読む)

配線構造及びその製造方法

【課題】 高温で保持されても動作不良を起こさない、信頼性の高い多層配線構造を実現する。

【解決手段】 第1配線102Aと第2配線111とは、層間絶縁膜(SiO2 膜104及びFSG膜105)中に形成されたビア110Aを介して接続されている。第2配線111におけるビア110Aの接続部分の近傍にダミービア110Bが接続されている。ダミービア110Bは、実使用時において閉回路の一部分とはならない。

(もっと読む)

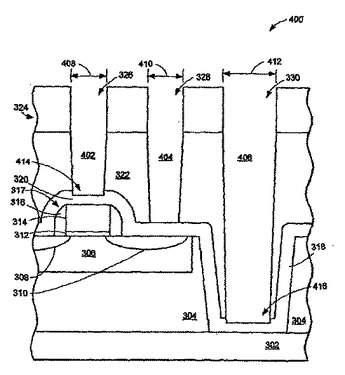

集積回路におけるコンタクトサイズをサイジングすることによって多層コンタクトを製造するための方法

集積回路を形成するための方法(600)は、第1半導体基板(202)上の半導体デバイス(317)表面上の誘電材(322)における第1深さに第1開口部(228)、(338)、(402)をエッチングし、第1半導体基板(202)表面上の誘電材(322)において第2深さに第2開口部(230)、(340)、(404)をエッチングする。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、エッチングラグに起因してほぼ同時に第1及び第2深さにエッチングするためにそれぞれ異なってサイズされる。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、導電材で充填される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

多層配線構造を備えた半導体装置

【課題】本発明の課題は、多層構造の配線層に加わるパッケージの熱収縮による応力を効果的に緩和し、チップの保護膜であるパッシベーション膜のクラックの発生などを防止できる半導体装置を提供することである。

【解決手段】上記課題は、半導体基板11上に層間絶縁膜14を介して下層配線と13上層配線15とが形成される多層配線構造を備えた半導体装置において、層間絶縁膜14の面積が広くとれるように該層間絶縁膜14に開ける開口を小さくすることを特徴とする多層配線構造を備えた半導体装置にて解決される。

(もっと読む)

半導体装置とその製造方法およびモノリシックマイクロ波集積回路

【課題】 強度低下や寸法増大を抑えながら、バイアホールの接地インダクタンスを低減できる半導体装置とその製造方法およびMMICを提供する。

【解決手段】 このマイクロ波帯用増幅器GaAsMMICは、その接地電極8が、3個のバイアホール11からなるバイアホール群12を有し、この3個のバイアホール11は、その内側に充填されたメッキ金属10aが近接されて形成され、その相互作用によって高周波的な電磁界結合が発生して、接地インダクタンスが低減された。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度が強く、かつ、放熱性に優れた半導体装置を提供する。

【解決手段】 シリコン基板10上に形成される配線層のうち、第1層から第3層を、コンタクト部11及びビア14a,14bにタングステン、配線13a〜13cに銅をそれぞれ用いてシングルダマシン工程によって形成し、第4層から第6層を、ビア15a〜15c及び配線13d〜13fに銅を用いてデュアルダマシン工程によって形成し、かつ、第4層から第6層におけるビア15a〜15cの径を第1層から第3層におけるコンタクト部11及びビア14a,14bの径の12.9倍以上とする。

(もっと読む)

281 - 291 / 291

[ Back to top ]