Fターム[5F033NN34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560) | コンタクトホールの大きさ、数 (291)

Fターム[5F033NN34]に分類される特許

161 - 180 / 291

超高密度のキャパシタ及び基板貫通ビアを有する集積基板

システム・イン・パッケージ用の集積基板は、基板貫通ビア及びトレンチキャパシタを備え、少なくとも4つの導電性のキャパシタ電極層を誘電層との交互の配列で含むトレンチ充填物を有する。キャパシタ電極層は、第1又は第2の基板側に設けた2つのキャパシタ端子のそれぞれの1つに、交互に接続される。トレンチキャパシタ及び基板貫通ビアは、半導体基板中に10μmを越える同等の横方向の延びを有するトレンチ開口及びビア開口内にそれぞれ形成される。この構造によれば、基板中にビア開口及びトレンチ開口を同時に製造することができるので、他の利点の中でも特に、集積基板をコスト効率よく製造することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

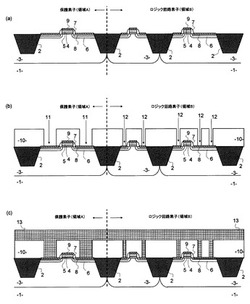

【課題】 集積度が低下することを最大限抑制しつつ、必要に応じて大きい電流容量の確保を可能にしたコンタクトプラグを備えた半導体装置の製造方法を提供する。

【解決手段】 半導体基板1上にソース・ドレイン領域8を形成後、層間絶縁膜10を堆積し、ソース・ドレイン領域8の上面が露出するようにコンタクトホールを開口する。このとき、比較的小電流容量で機能を奏するロジック素子形成領域上面においては最小加工寸法で規定される程度の小さい孔径で開口する一方、大電流容量を必要とする保護素子形成領域上面においては、第1孔径よりも大きい第2孔径で開口する。その後、これらのコンタクトホールを完全に充填するように、コンタクトプラグ材料膜13を層間絶縁膜10の堆積膜厚以上成膜する。その後、コンタクトプラグ材料膜13に対して平坦化処理を行った後、配線層を形成する。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】デュアルダマシン(Dual-Damascene)法を用いた多層Cu配線の形成工程を簡略化する。

【解決手段】層間絶縁膜45上に形成したフォトレジスト膜51をマスクにして層間絶縁膜45をドライエッチングし、層間絶縁膜45の中途部に形成したストッパ膜46の表面でエッチングを停止することによって配線溝52、53を形成する。ここで、ストッパ膜46を光反射率の低いSiCN膜によって構成し、フォトレジスト膜51を露光する際の反射防止膜として機能させることにより、フォトレジスト膜51の下層に反射防止膜を形成する工程が不要となる。

(もっと読む)

被膜形成方法、絶縁膜を有する構造体及びその製造方法並びに電子部品

【課題】孔部の少なくとも内壁面に均一な被膜を形成する方法、この方法を利用した、絶縁膜を有する構造体及びその製造方法並びに電子部品を提供する。

【解決手段】本発明の被膜形成方法は、開口部の面積が25〜10,000μm2であり且つ深さが10〜200μmである孔部を有する基板に、溶剤を塗布する溶剤塗布工程と、樹脂成分及び溶剤を含有し、剪断速度6rpmにおける粘度V1(mPa・s)と、剪断速度60rpmにおける粘度V2(mPa・s)との比(V1/V2)が、1.1以上の樹脂組成物を、該樹脂組成物が上記孔部内の上記溶剤と接触するように、上記基板に塗布する樹脂組成物塗布工程と、塗膜を乾燥する乾燥工程と、を備え、該孔部の内壁面及び底面のうちの少なくとも該内壁面に上記樹脂成分を含む被膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、配線層間に形成される酸化膜により、配線層間の接続抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、第1の配線層3と第2の配線層とを接続する開口領域8〜12を埋設する第1の金属層14〜18上のスピンコート樹脂膜21に開口部22が形成されている。開口部22内では、メッキ用金属層23を構成するCr層とCuメッキ層24とが接続している。この構造により、第1の金属層14〜18上のCr層は、結晶粒子間が広くなり、粗な領域となる。そして、Cr層の粗な領域には、第2の金属層19とCuメッキ層24との合金層が形成され、接続抵抗値が低減される。

(もっと読む)

トランジスタ固有のコンタクト設計によってトランジスタの性能を向上させるための手法

コンタクト構造(230A,230B)のサイズおよび/または密度を局所的に適合させることによって、例えば、個々のトランジスタ(210,210A,210B)内で、あるいは、より広い範囲で、高性能の半導体デバイス(200)の全体的な性能を向上させることができる。このため、コンタクト構造(230A,230B)と局所的なデバイス特性との間の相互関係に配慮することができる。一方で、従来のプロセス戦略と高い互換性を維持することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】パワー素子と他の半導体デバイスとの複合型の半導体装置において、多層配線によって半導体デバイスの電極を最上層まで引き伸ばすに際し、多層配線のうちパワー素子における配線抵抗を小さくしつつ、多層配線の配線層にクラックを生じさせないようにする。

【解決手段】積層配線20のうち第1領域11におけるパワーMOSトランジスタのソース電極32、ドレイン電極31を積層配線20の2層目の配線層22より上層の配線層23〜25において、複数の微細なビアホールを用いずに1つの電極としてそれぞれ形成する。

(もっと読む)

半導体装置

【課題】配線間が抵抗で接続された回路を半導体基板上に有する半導体装置において、前

記抵抗を、半導体基板やこの抵抗に接続されていない配線から電界の影響を受け難いよう

に形成する。

【解決手段】この半導体装置は、第1の配線10と第2の配線20aが抵抗14で接続さ

れた回路を、n基板(半導体基板)1上に有する。第1の配線10と第2の配線20aが

絶縁膜12を挟んで層状に形成され、絶縁膜12に形成されたバイアホール13内に抵抗

14が形成されている。

(もっと読む)

半導体集積回路及び入出力セルの信号端子設計方法

【課題】信号端子を有する入出力セルを備えた半導体集積回路において、前記入出力セルの信号端子が接続用配線ヴィアを介して内部回路に接続される場合に、そのヴィアの原子の移動に起因するオープン不良を有効に防止する。

【解決手段】入力/出力セル2の信号端子3Aは、複数層(例えば4層)の導電層で形成される。その複数層の導電層の隣接する導電層同士は、ヴィアで接続される。前記複数層の導電層のうち、最大径のヴィア6−3で接続される導電層(例えば第4層の導電層)3−4では、その導電層3−4の幅が前記最大径のヴィア6−3を1個だけ配置できる幅に設定される。従って、接続用配線4から入力/出力セル2の入力端子3Aに原子が移動することが抑制され、前記接続用配線4に形成されるヴィア(図示なし)のオープン不良が有効に防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の接続孔を用いて配線間を接続する半導体装置において、信頼性を向上させる。

【解決手段】第1の絶縁膜8上及び第1の配線10a上に形成された第2の絶縁膜11と、第2の絶縁膜11に形成されており、第1の配線10aの上方を通る溝12aと、溝12aの底部に位置していて第1の配線10a上に配置された第1の接続孔及び第2の接続孔12bと、溝12a、並びに第1の接続孔及び第2の接続孔12bに埋め込まれた第2の配線13aとを具備する、第2の配線13aは、第1の配線10aとは同一長さにおける抵抗値が異なり、第2の接続孔は第1の配線10a又は第2の配線13aの幅方向において第1の接続孔と異なる位置に配置されている。

(もっと読む)

半導体装置

【課題】半導体装置に含まれるESD保護トランジスタのESD耐性を向上できるようにする。

【解決手段】半導体装置は、ウェル領域101の上に形成されたゲート電極103と、ウェル領域101におけるゲート電極103のゲート長方向側にそれぞれ形成されたドレイン領域104及びソース領域105と、ドレイン領域104の上で且つゲート電極103のゲート幅方向に互いに間隔をおいて形成された複数のドレインコンタクト106A〜106Cと、ソース領域105の上で且つゲート電極103のゲート幅方向に互いに間隔をおいて形成された複数のソースコンタクト107A〜107Eとを有している。隣り合うドレインコンタクト同士の間隔は、隣り合うソースコンタクト同士の間隔よりも大きい。

(もっと読む)

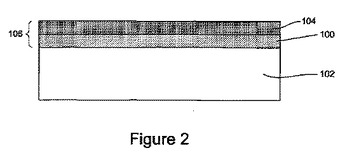

金属シリサイド晶子上にナノ構造物を形成する方法、並びにこの方法により得られる構造物及びデバイス

本発明の種々の実施形態は、非単結晶基板上にナノ構造物を形成する方法、並びにその結果得られるナノ構造物及びナノスケール機能デバイスに関する。本発明の一実施形態では、ナノ構造物を形成する方法は、金属層(100)及びシリコン層(104)を含む多層構造物(106)を形成することを含む。多層構造物(106)は、熱工程にかけられ、それにより金属シリサイド晶子(110)が形成される。金属シリサイド晶子(110)上にはナノ構造物(114)が成長される。本発明の別の実施形態では、構造物は、非単結晶基板(102)及び非単結晶基板(102)上に形成された層(108)を含む。層(108)は、金属シリサイド晶子(110)を含む。金属シリサイド晶子(110)上にいくつかのナノ構造物(114)が形成されてもよい。開示の構造物は、電子デバイス及び/又は光電子デバイスで使用されるいくつかの異なるタイプの機能デバイスを形成するために使用することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】ソースセルとドレインセルが市松模様状に配置された低オン抵抗の横型MOSトランジスタを有してなる半導体装置であって、高密度配線に有利なプラグ技術と両立可能で、制御IC等との複合化に好適な小型の半導体装置を提供する。

【解決手段】ソースセル102,103とドレインセル104,105が、それぞれ、コンタクトプラグ31,32によって、平坦化された第1配線層41,42に接続されてなり、コンタクト31bで示されたソースコンタクトプラグが、コンタクト32aで示されたドレインコンタクトプラグのコンタクト面内における最小幅W2より小さな最小幅W1を有するコンタクト31b1〜31b5で示された小コンタクトプラグの複数個の組み合わせからなる半導体装置110とする。

(もっと読む)

半導体集積回路のボンディングパッド、その製造方法、半導体集積回路、並びに電子機器

【課題】パッド表面の平坦性を確保すると共に、十分な電流の導通が可能であり、また、金属配線層間を接続する開口経路の導通不良が少ない信頼性の高い半導体集積回路のボンディングパッドを提供する。

【解決手段】本発明に係る半導体集積回路のボンティングパッド10は、金属配線層間を接続する開口経路Pが、開口経路の埋め込みに必要な開口幅と、当該開口幅よりも大きい開口幅を有する他の開口幅との少なくとも2つの異なる開口幅を有する開口部分を備え、これら異なる開口幅を有する開口部分が縦横に張り巡らされて構成されている。

(もっと読む)

配線構造及び配線設計方法

【課題】ビア数を減らしても、エレクトロマイグレーション耐性を維持、または向上することのできる配線設計方法を提供する。

【解決手段】異なる層に位置する第1の配線と第2の配線を複数のビアで接続する配線設計方法において、配線幅方向のビアの数であるビア列数を変えたときの配線の寿命の変化率と、配線長方向のビアの数であるビア行数を変えたときの前記配線の寿命の変化率を求める。処理対象となるビアアレイのビア列数を、前記ビア列数に対する前記寿命の変化率と、前記ビア行数に対する前記寿命の変化率とに基づいて決定されるビア行列数増減比Nに従って低減する。そして、前記ビアアレイのビア行数を、少なくとも1行増加する。

(もっと読む)

半導体装置

【課題】低抵抗コンタクトを維持しつつ、より微細化された半導体装置を提供する。

【解決手段】半導体装置は、トランジスタTr1、Tr2と、第1コンタクト13と、第2コンタクト10とを具備する。トランジスタTr1、Tr2は、半導体基板1上に設けられ隣接している。第1コンタクト13は、トランジスタTr1、Tr2間にセルフアライメント構造で設けられ、トランジスタTr1、Tr2の共通のソースに接続され、金属を含んでいる。第2コンタクト10は、トランジスタTr1,Tr2のドレインにそれぞれ接続され、金属を含んでいる。

(もっと読む)

半導体集積回路

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、パワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、複数の第1のバス(140〜142)と、複数の第2のバス(150〜152)と、複数の第1のバス(140〜142)及び複数の第2のバス(150〜152)の各々に1つずつ設けられたコンタクト・パッド(304)とを備える。複数の第1のバス(140〜142)と複数の第2のバス(150〜152)は、外部の接続部材(307)に近い側に位置するものから遠くに位置するものへと順に面積が小さくなるように形成されている。

(もっと読む)

半導体装置

【課題】 NMOSトランジスタとPMOSトランジスタの駆動能力のバラつきを減らす

ことができる半導体装置を提供する。

【解決手段】 半導体基板10上にゲート電極20が形成され、ゲート電極20の両側方

にn型ソース/ドレイン拡散層24、26が形成されるNMOSトランジスタと、半導体

基板10上にゲート電極20が形成され、ゲート電極20の両側方にp型ソース/ドレイ

ン拡散層44、46が形成されるPMOSトランジスタと、NMOSトランジスタ及びP

MOSトランジスタ上に形成される、ゲート電極20下部のチャネル領域に応力を与える

絶縁膜30、50と、n型ソース/ドレイン拡散層24、26上に絶縁膜30を貫通して

形成されるコンタクト34と、p型ソース/ドレイン拡散層44、46上に絶縁膜50を

貫通して形成されるコンタクト54を備える。そして、コンタクト34の寄生抵抗は、コ

ンタクト54の寄生抵抗よりも小さい。

(もっと読む)

半導体集積回路及びその製造方法

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンのうち対応する第1の金属パターンと電気的に接続する複数の第1のバス(140〜142)と、複数の第2の金属パターンのうち対応する第2の金属パターンと電気的に接続する複数の第2のバス(150〜152)と、複数の第1のバス(140〜142)及び複数の第2のバス(150〜152)の各々には、1つのコンタクト・パッド(304)が設けられている。

(もっと読む)

161 - 180 / 291

[ Back to top ]