Fターム[5F033PP00]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896)

Fターム[5F033PP00]の下位に属するFターム

原料ガス (624)

CVD(化学的気相成長法) (3,065)

PVD(物理的気相成長法) (5,261)

成膜の方向性制御 (169)

塗布又は液体からの成膜 (5,037)

エネルギービームを用いるもの (44)

同一膜を2段階以上で成長させるもの (600)

他物質から置換、交換するもの (18)

Fターム[5F033PP00]に分類される特許

61 - 78 / 78

ナノ導電性膜のパターニング方法

【課題】導電性粒子の精密パターニングに使われうるドナー基材を提供すること。

【解決手段】ベース基材と、ナノ導電性粒子及び有機半導体を含む前記ベース基材上の転写層と、を有することを特徴とするナノ導電性膜形成用のドナー基材。

(もっと読む)

薄膜形成方法

【課題】 転写膜の汚染や分解・変質を生じないレーザ転写による薄膜形成方法を実現する。

【解決手段】 本発明のレーザ転写による薄膜形成方法では、レーザ光9を透過するガラス基板1上に、照射されるレーザ光9によりアブレーションされるアブレーション層(第1の有機膜)2、カーボンブラックを混入させてレーザ光9を遮蔽する効果を持たせた有機膜(第2の有機膜)3、及びグルコースオキシターゼを含む薄膜(酵素膜)からなる転写膜4が順次積層された転写基板5を用意する。この転写基板5の転写膜4と、被転写基板であるp型シリコン基板(回路基板)6を、回路基板6上に設けたスペーサ7を介して対向させる。その後、ガラス基板1側からアブレーション層2にレーザ光9を照射することで、転写膜4aを回路基板6側に転写する。

(もっと読む)

材料を表面および基材に選択的に付着させる方法および装置

液、近臨界および/または超臨界流体から材料を選択的かつ制御可能に基材または表面に付着させて、表面または基材に付着される材料の位置および/または厚さを制御する方法が開示される。一つの例示的なプロセスでは、金属を選択的に付着させて基材の形体パターン(たとえば通路)を充填する。プロセスはさらに、たとえばシリコンウェーハ表面へのバリヤ膜の付着のために複合または構造化シリコンウェーハの表面下への材料の付着を制御するために使用することもできる。材料としては、過装入材料、金属、非金属、成層材料、有機材料、ポリマーおよび半導体材料があるが、これらに限定されない。本発明は、半導体チップ製造のような工業プロセスで用途を見いだす。特に、選択的付着は、液、近臨界または超臨界流体から付着される金属によるパターン形体の選択的充填および/またはコーティングにより、半導体チップ製造におけるケイ素面のケミカルメカニカル平坦化のようなプロセスの代替を提供する、またはその必要性を減らすものと想定される。

(もっと読む)

(もっと読む)

金属ナノワイヤ作製法および金属ナノワイヤ

【目的】 本発明は駆動力を与えることでドリフトさせた原子または分子を集約、成長させることによりナノワイヤを形成し金属ナノワイヤを作製する方法および金属ナノワイヤを提供する。

【解決手段】 駆動力を与えることによりドリフトさせた金属原子を物理的な拘束を用いることで集約、成長させる金属ナノワイヤの作製法で、金属薄膜配線が陰極部上面と同一平面レベルに成すように形成され、かつ陰極部と一体化している金属薄膜配線に電子流が陽極側へ平行移動することで、少なくともドリフトが生じるスリット部分に電子流を集約させ、金属薄膜配線の上層にSiO2などの保護膜にある孔より金属薄膜配線と同じ成分を有する金属ナノワイヤを形成することを特徴とする。

(もっと読む)

半導体素子の配線形成方法

【課題】トレンチ内に主金属配線材料の占有体積を十分確保すると同時に、Fアタック問題およびWボルカーノ問題を防止することが可能な半導体素子の配線形成方法を提供する。

【解決手段】所定の構造物が形成された半導体基板に層間絶縁膜を形成する段階と、前記層間絶縁膜に半導体基板の一定の領域を露出させるトレンチを形成する段階と、前記トレンチを含んだ全表面上に接着層と第1バリア金属膜を順次形成する段階と、前記トレンチの下部に第2バリア金属膜を形成する段階と、前記トレンチ内に配線を形成する段階とを含んでなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造に係る期間の短縮及びコストの低減を図ると共に、製品としての信頼性の向上に寄与することができる「半導体装置及びその製造方法」を提供すること。

【解決手段】 機能素子が作り込まれた半導体基板11の一方の面に、絶縁層12を介して導体層13を形成した後、半導体基板11の所定の箇所にスルーホールTH1を形成する。さらに、半導体基板の他方の面に支持シートを張り付け、導体層13と支持シート上とをワイヤ14により接続し、導体層13、ワイヤ14及びスルーホールTH1が形成されている部分を樹脂16で封止した後、支持シートを除去する。さらに、半導体基板11の他方の面から露出しているワイヤ14の端部14a上に導体層15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 表面に凹凸パターンを有する基板上に均一な膜を所定の膜厚で成膜する方法を提供することを目的とする。

【解決手段】 表面に凹凸パターンを有する基板上に第1の材料からなる第1の膜厚の薄膜を堆積する工程を備えた半導体装置の製造方法であって、表面に凹凸パターンを有しないモニタ基板上に前記第1の材料からなる薄膜を形成してその薄膜の膜厚を測定することにより前記第1の膜厚の薄膜を堆積する第1の条件を算出し、前記凹凸パターンを有する基板上に、前記第1の条件よりも厚い薄膜が堆積される第2の条件で前記第1の材料を堆積することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

基板及びその製造方法

【課題】 本発明は、基材を貫通する貫通ビアと、貫通ビアと接続される配線とを備えた基板及びその製造方法に関し、配線が接続される貫通ビアの電気的な接続信頼性を向上することのできる基板及びその製造方法を提供することを課題とする。

【解決手段】 貫通部55と、貫通部の一方の端部に設けられ、貫通部の直径R1よりも幅広の形状とされた配線接続部56と、貫通部の他方の端部に設けられ、貫通部の直径R1よりも幅広の形状とされた接続パッド57とにより貫通ビア54を構成し、配線接続部56に外部接続端子69を有した配線68を接続する。

(もっと読む)

層間配線に多層カーボンナノチューブを用いる配線構造及びその製造方法

【課題】 2以上の導線層の層間配線に多層カーボンナノチューブ(CNT)が使用される配線構造の低抵抗化を図ることの可能な配線構造を得ること。

【解決手段】 配線構造では、2以上の導電層の層間配線に多層CNTが使用される。前記多層CNTに含まれるグラフェンシートにより形成され、前記多層CNTの成長基点から遠い側の端部に同心状に形成される複数の環状の切り口が、導電層にそれぞれ接触する。CNTのキャップ層の部分を介さずに、導電層とグラフェンシートが接するので、それらの間の接触抵抗は従来よりも小さくなる。

(もっと読む)

成膜方法

【課題】 超臨界状態の媒体を用いた、微細パターンへの成膜方法において、従来に比べて微細パターンへのカバレッジと埋め込み特性を良好とし、さらに微細なパターンへの成膜を可能とする。

【解決手段】 被処理基板上に、超臨界状態の媒体にプリカーサを溶解した処理媒体を供給して成膜を行う成膜方法であって、前記被処理基板の温度を、成膜が生じる温度の下限である成膜下限温度未満である第1の温度とし、当該被処理基板上に前記処理媒体を供給する第1の工程と、前記被処理基板の温度を前記第1の温度から前記成膜下限温度以上である第2の温度に上昇させることで、当該被処理基板上に成膜を行う第2の工程と、を有することを特徴とする成膜方法。

(もっと読む)

貫通電極の形成方法

【課題】半導体基板の厚み方向に貫通する貫通電極の形成方法において、工程数の削減と工程管理の容易化を図る。

【解決手段】貫通電極の形成方法において、半導体基板10の一方の面にエッチングマスク12を他方の面にエッチングストップ層11を形成する第1工程、エッチングマスク12に設けた開口13から露出した基板10の領域をエッチングストップ層11までエッチングして凹部14を形成する第2工程、凹部14の内面と基板10の一方の面に絶縁膜11aを成膜した後に凹部14に導電体15を形成する第3工程、基板10の一方の面に導電体15と電気的接続した第1配線導体16aを形成した後に凹部14の底面を構成するエッチングストップ層11に開口18を形成して導電体15を露出させる第4工程、及び開口18から露出した導電体15と電気的接続した第2配線導体17aを形成する第5工程を含む貫通電極の形成方法。

(もっと読む)

低圧冷間溶接によるデバイス製造方法

パターン形成されたスタンプ、好ましくは柔らかいエラストマースタンプから基板に金属および/または有機層を転写する方法が提供される。 このパターン形成された金属または有機層は例えば広範囲の電子デバイスで使用することができる。 この方法は、有機電子構成部品のナノスケールパターン形成に特に適している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一面側に形成された半導体素子の電極端子と、この半導体基板の他面側に形成された外部接続端子用のパッドとを電気的に接続する距離を可及的に短距離にできる半導体装置を提供することにある。

【解決手段】半導体素子12が一面側に造り込まれた半導体基板10の半導体素子形成面側には、半導体素子12の電極端子12aから半導体基板10と電気的に絶縁されて延出されたパターン14と、半導体素子12及びパターン14を覆う絶縁層16とが形成され、 半導体基板10の他面側には、パターン14と電気的に接続された外部接続端子用のパッド32が形成された半導体装置であって、該半導体基板10の他面側に開口され且つ底面にパターン14の半導体素子近傍の半導体基板側面が露出する凹部は、その側壁面を覆う絶縁層22と、パターン14の半導体基板側面に一端部が接続されていると共に、他端部が前記凹部の開口部を覆うように形成されたパッド32に接続された金属から成る柱状導体部30とによって充填されていることを特徴とする。

(もっと読む)

レジスト除去方法及び半導体装置の製造方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 ビアホール用開口3を有するレジストマスク4をエッチングマスクにして、第1キャップ層2c、第1低誘電率膜2bを順次に反応性イオンエッチング(RIE)でドライエッチングしビアホール5を形成する。そして、レジストマスク4の除去では、はじめに、上記RIEでレジストマスク4表面部に形成された変質層4aに対して、ホットプレートにより空気雰囲気、300℃温度、3分程度の熱処理を施すことで、変質層4aを少なくともその一部が酸素と反応した改質層4bに変換させる。その後に、この改質層4bおよびレジストマスク4に水素ラジカルを照射して残渣のないレジスト除去を行う。

(もっと読む)

半導体素子の金属配線形成方法

【課題】既存の金属配線パターンマスクを用いてダマシン工程を実施しながら層間絶縁膜の幅を最大限確保し、金属配線間の間隔を広めて相互干渉を防止することにより、半導体素子の誤動作を防止することが可能な半導体素子の金属配線形成方法を提供する。

【解決手段】絶縁膜11〜14の形成された半導体基板を提供する段階と、金属配線パターンマスクを用いたエッチング工程によって前記絶縁膜をパターニングして溝を形成するが、前記エッチング工程の際に発生するポリマーの量を制御し、パターニングされる前記絶縁膜の上部コーナー部位にラウンディング(rounding)16を形成する段階と、前記溝が埋め込まれるように金属配線を形成する段階と、このラウンディング部が除去されるようにCMP工程により全体構造上部を平坦化する段階を含む。

(もっと読む)

半導体装置の製造方法

【目的】 不純物の残留を抑制し、バリアメタルを高純度に成膜することを目的とする。

【構成】 基体上にTa[N((CH3)2]5を供給するTa[N((CH3)2]5供給工程(S102)と、前記Ta[N((CH3)2]5におけるTaとは異なるCを除去するH2供給工程(S106)と、前記Cが除去された前記Ta[N((CH3)2]5の吸着分子に基づいて前記TaN膜を生成するNH3供給工程(S108)と、を備え、前記Ta[N((CH3)2]5工程とH2供給工程とNH3供給工程とを繰り返すことで、前記基体上にTaN膜を堆積させることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体装置及びその製造方法

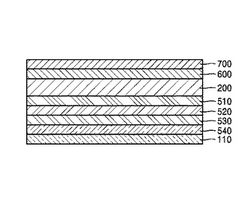

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

61 - 78 / 78

[ Back to top ]