Fターム[5F033PP27]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 塗布又は液体からの成膜 (5,037) | 電解メッキ (2,541)

Fターム[5F033PP27]に分類される特許

2,001 - 2,020 / 2,541

配線基板の作製方法及び半導体装置の作製方法

【課題】多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストに配線基板及び半導体装置を作製する方法を提案する。さらに、低コストで環境への悪影響が少ない配線基板の作製方法及び該配線基板を利用した半導体装置の作製方法を提案する。

【解決手段】第1の基板上に導電性材料からなるパターンを形成し、前記パターン上に電解めっき処理により導電膜を形成し、前記パターンと前記導電膜とを分離し、第2の基板上に薄膜トランジスタを有するICチップを形成し、前記導電膜とICチップとを電気的に接続する。

(もっと読む)

半導体装置

【課題】銅配線を覆って設けられるバリアメタル膜のバリア性能が向上されており、低比誘電率層間絶縁膜から放出されるガスによりバリアメタル膜が酸化されても、銅配線の信頼性や性能、および品質等が低下するおそれの殆ど無い半導体装置を提供する。

【解決手段】比誘電率が3以下である絶縁膜3が基板1上に少なくとも1層設けられている。少なくとも一部がこの絶縁膜3内に形成されている凹部10の内面を覆って第1のバリアメタル膜6が設けられている。この第1のバリアメタル膜6の表面を覆って凹部10内に第2のバリアメタル膜7が設けられている。この第2のバリアメタル膜7の表面を覆って凹部10内に第3のバリアメタル膜8が設けられている。この第3のバリアメタル膜8の表面を覆って凹部10内にCu膜11が埋め込まれて設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】実装時における接続信頼性を向上させることができるとともに、高い歩留まりにて製造できる半導体装置およびその製造方法を提供することを目的とする。

【解決手段】半導体ウェーハ1上に、電極パッド2を形成する。次いで、半導体ウェーハ1上に、第1、第2の保護膜4、5を形成する。そして、第1、第2の保護膜4、5を除去して、薄膜化し、電極パッド2上に開口部6を形成する。次いで、開口部6において、電極パッド2の表面上に残存する第1の保護膜4を選択的に除去し、電極パッド2の表面を露出させるとともに、電極パッド2の表面上に、第1の保護膜4の一部からなり、開口部6の段差よりも小さい段差を有する段差部12を形成する。次いで、開口部6に、電極パッド2と接触するように、バリアメタル膜8を形成する。そして、電極パッド2上の開口部6内であって、段差部12の表面上に形成されたバリアメタル膜8上に、バンプ9を形成する。

(もっと読む)

表面疎水化方法、表面疎水化用組成物、ならびに半導体装置およびその製造方法

【課題】 層の表面をより簡便にかつ効果的に疎水化することができ、かつ、層のより深い領域を疎水化することができる表面疎水化方法、表面疎水化用組成物、ならびに半導体装置およびその製造方法を提供する。

【解決手段】 本発明の表面疎水化方法は、(A1)第1の反応性シラン化合物および(B1)有機溶媒を含む第1の表面疎水化用組成物を前記層の表面に接触させる工程、および(A2)第2の反応性シラン化合物および(B2)有機溶媒を含む第2の表面疎水化用組成物を前記層の表面に接触させる工程を含む。前記(A2)第2の反応性シラン化合物1分子あたりの反応性基の数は、前記(A1)第1の反応性シラン化合物1分子あたりの反応性基の数より少ない。

(もっと読む)

超小型電子技術における電極パッド

ある実施の形態に係る集積回路(30)は、基板(38)と、基板の上に設けられた回路素子(34)と、電極パッド(72)と、を含み、回路素子が基板と電極パッドとの間に配置されるように、電極パッドが回路素子の上に配置され、かつ垂直軸に沿って回路素子と一直線上に並べられるという特徴を持つ。 (もっと読む)

半導体装置およびその製造方法

【課題】厚さの異なる複数本の配線を同じ層に効率良くかつ容易に設けることができる半導体装置の製造方法を提供する。

【解決手段】第1の幅を有する第1の凹部3、および第1の幅の1/x(xは1より大きい正の数)の大きさである第2の幅を有するとともに第1の凹部3と同じ深さを有する第2の凹部4を、基板1上の第1の絶縁膜2に形成する。第1の凹部3および第2の凹部4が形成された第1の絶縁膜2の表面を覆って第2の絶縁膜5をその膜厚が第1の幅の1/2xの大きさになるまで設ける。第1の凹部3の側部に第2の絶縁膜5を残しつつ第1の凹部3の底部が露出するまで第1の絶縁膜2の表面上に設けられた第2の絶縁膜5を主にその膜厚方向に沿って異方的に除去する。第1の凹部3および第2の凹部4のそれぞれの内部に導電体6を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面にキャップメタル膜が形成された銅配線を含む半導体装置において、ビア接続の歩留まりや抵抗の均一性を良好にする。

【解決手段】 本発明の半導体装置の製造方法は、半導体基板上に形成された絶縁膜に、配線溝を形成する工程(S100)と、絶縁膜上全面に、バリアメタル膜を形成する工程(S102)と、バリアメタル膜上全面に、配線溝内を埋め込むように銅膜を形成する工程(S104)と、絶縁膜表面に、バリアメタル膜が残る条件で、配線溝部外の銅膜を研磨により除去する工程(S106)と、銅膜を研磨により除去する工程の後に、配線溝部内に形成された銅膜上に、選択的にキャップメタル膜を形成する工程(S108)と、キャップメタル膜を研磨により平坦化する工程(S110)とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】

バンプ形成前の迅速な電気的特性の測定を可能とし、この測定結果をフィードバックすることで開発期間の短縮を図ることを可能とする半導体装置の製造方法及び半導体装置を提供する。

【解決手段】

メタル配線1上に堆積させた保護膜2に、開口底部が前記メタル配線1の表面に達し、プロービング用針の先端部が侵入しない寸法を有する、複数の開口部3を形成し、この開口部3を介して前記メタル配線1と電気的に導通するように堆積させたバリアメタル膜をパターニングすることで、前記保護膜2の前記複数の開口部3が形成された領域上にプロービング用パッド4を形成し、このプロービング用パッド4に前記プロービング用針の先端面を接触させることで、形成された回路の電気的特性の測定を可能とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体ウェハ状態で、工程中に金属配線の電気的な検査を行い、金属配線の不良を精度良く検出すると共に、金属配線の不良が発生した場合は、迅速かつ的確に不良原因が特定され、工程へフィードバックさせることが可能となる半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体基板上10の金属配線13及び外部端子接続用電極15が形成されていない領域に、金属配線13のオープン、ショート、リーク不良、素子電極11と金属配線13との接続不良を電気的に検出する検査用金属配線14及び検査用電極16を有し、半導体ウェハ状態での電気的な検査によって、工程中に精度良く上記不良を検出することが可能となる。又、電気的な検査を実施することで、不良原因を迅速にかつ的確に確認し、工程に早期フィードバックが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】保護絶縁膜で配線溝および接続孔の内面に露出する多孔質の低誘電率膜を被覆することで、導通不良、耐圧不良、信頼性不良等の不具合を抑制して、高性能かつ高歩留まり、高信頼性の多層配線を提供することを可能とする。

【解決手段】多孔質の低誘電率膜21を有する層間絶縁膜と、層間絶縁膜に形成された配線溝23とこの配線溝23に接続する接続孔24と、配線溝23の内面と接続孔24の側壁に露出した多孔質の低誘電率膜21を被覆するように接続孔24底部を除く接続孔24の内面および配線溝23の内面に形成された保護絶縁膜25と、配線溝23の内面および接続孔24の内面に保護絶縁膜25を介して形成されたバリアメタル膜26と、配線溝23の内部および接続孔24の内部に保護絶縁膜25、バリアメタル膜26を介して形成された配線材料膜28とを備えたものである。

(もっと読む)

集積回路装置の製造方法

【課題】 本発明の目的は、リソグラフィー技術の限界を破ることのできる、微細な細線構造を備えた集積回路装置、特に集積記憶装置の製造方法を提供することにある。

【解決手段】 基板上に、絶縁体で分離された複数の素子を、第一の方向において50nm以下のピッチで配置し、第二の方向では前記ピッチの1.2倍以上かつ2倍以下のピッチで配置し、前記複数の素子が接続する下配線を用いて複数の素子に電位を付与して、素子表面に電解メッキ法により金属ドットを成長させて、第二の方向に並ぶ複数の素子に接続する金属配線を形成する工程を備えることを特徴とする集積回路装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 拡散防止機能を高めることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に形成された酸素を含有する絶縁体の表面上に、銅以外に少なくとも2種類の金属元素を含む銅合金皮膜を形成する。(b)銅合金皮膜上に、純銅または銅合金からなる金属膜を形成する。(c)工程aまたは工程bの後に、絶縁体中の酸素と銅合金皮膜中の金属元素とが反応して絶縁体の表面に金属酸化物膜が形成される条件で熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線形成時のボイドの発生を抑制し、バリアメタル層とCu層の密着性低下を抑制できる半導体装置の製造方法とこの方法で製造された半導体装置を提供する。

【解決手段】基板10に配線を形成する半導体装置の製造方法であって、まず、基板10にTa系バリアメタル材料とCu及び/またはAgとの合金からなるバリアメタル層16を形成する。次に、バリアメタル層16の上層にバリアメタル層16を電極とする電解メッキによりCuを含む金属層17を形成し、バリアメタル層16及び金属層17を配線パターンに加工する。

(もっと読む)

半導体装置の製造方法

【課題】銅の溝配線の上面バリア膜を形成するための触媒金属の置換めっきに起因する銅配線のエッチング損傷を容易に防止できる半導体装置の製造方法を提供する。

【解決手段】銅を含む配線上に銅拡散防止機能を有するバリア膜を有する半導体装置の製造方法であって、まず、基板に配線溝TR1を形成し、配線溝の内壁面にバリアメタル層16を堆積した後、上面バリア膜形成のための置換めっき用触媒金属17aを含むシード層を形成する。次に配線溝を埋め込んで全面に銅を含む金属層18を形成し、触媒金属を金属層中に熱拡散させ、触媒金属と合金化した金属層19とする。配線溝の外部における金属層19を除去して配線パターンに加工し、合金化された金属からなる配線を形成する。この後、配線の表面に銅拡散防止機能を有する上面バリア膜を置換めっきにより形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 比誘電率の低い絶縁膜を備え、かつ、電気的性能の劣化および信頼性の劣化を抑制することが可能な、多層配線構造の半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板と、前記半導体基板上に形成された絶縁膜と、前記絶縁膜内に形成された配線とを有し、前記絶縁膜は、前記配線の直下に位置する第1の絶縁膜と、その他の部分に位置する第2の絶縁膜から構成され、前記第1の絶縁膜は、前記第2の絶縁膜との境界面に位置する表層の炭素濃度が前記第1の絶縁膜の内部の炭素濃度よりも高いことを特徴とする半導体装置を提供する。

(もっと読む)

半導体製造方法

【課題】 ダマシン配線プロセスにおける層間膜剥れや配線溝外のCu膜残存を抑えることが可能な半導体製造方法を提供する。

【解決手段】 半導体基板上に、第1の層間膜を形成する工程と、前記第1の層間膜の外周部を除去する第1のエッジカットを行なう工程と、前記第1の層間膜上に、第1のエッジカット位置より外側で第2のエッジカットを施した配線パターンを形成する工程と、前記配線パターンにより、前記第1の層間膜に配線溝を形成するとともに、エッジカットを行なう工程と、前記配線溝が形成された前記第1の層間膜上に、前記第1のエッジカット位置と第2のエッジカット位置の間に第3のエッジカットを施した配線層を形成する工程を備える。

(もっと読む)

半導体装置の製造方法

【課題】 本発明の目的は、導電層の密着性の向上及びマイグレーションの防止を図ることにある。

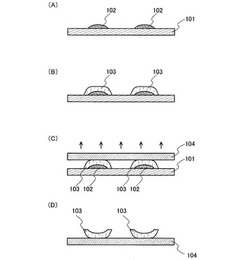

【解決手段】 半導体装置の製造方法は、(a)電極パッド16及びパッシベーション膜18を有する半導体基板10の上方に樹脂層30を形成する工程と、(b)樹脂層30を樹脂層30の突起方向に外力を加えながらキュアすることにより、樹脂突起40を形成する工程と、(c)電極パッド16と電気的に接続する導電層50を、樹脂突起40の上方に至るように形成する工程と、を含む。

(もっと読む)

電子基板とその製造方法及び電気光学装置並びに電子機器

【課題】 高精度の抵抗部を容易に形成する。

【解決手段】 基板P上に配線パターン20、21が設けられる。配線パターン20、21の一部の配線諸元を、他の部分と異ならせて設けられた抵抗素子Rを有する。

(もっと読む)

電子基板の製造方法及び電気光学装置の製造方法並びに電子機器の製造方法

【課題】製造コストを抑えつつ、高精度の電子素子を形成できる電子基板の製造方法および電気工学装置の製造方法並びに電子機器の製造方法を提供する。

【解決手段】配線パターンを有する基板Pに対してマスク22を貼着する工程と、マスク22の開口部22aを介して配線パターンの一部を除去して抵抗素子を形成する工程とを備える。マスク22は、基板Pに貼着される第1フィルム材22Aと、第1フィルム材22Aに剥離可能に貼り合わされる第2フィルム材22Bとを有する。マスク22の所定領域に開口部22aを形成し、開口部22aが形成されたマスク22を負圧環境下で基板Pに貼着する。

(もっと読む)

半導体装置の製造方法

【課題】 本発明の目的は、導電層の密着性の向上及びマイグレーションの防止を図ることにある。

【解決手段】 半導体装置の製造方法は、(a)電極パッド16及びパッシベーション膜18を有する半導体基板10の上方に、エネルギー硬化型の樹脂層20を形成する工程と、(b)第1のエネルギー供給処理により、樹脂層20を硬化収縮させることなく融解させる工程と、(c)第2のエネルギー供給処理により、融解後の樹脂層30を硬化収縮させて樹脂突起40を形成する工程と、(d)電極パッド16と電気的に接続し、かつ樹脂突起40の上方を通る導電層50を形成する工程と、を含む。

(もっと読む)

2,001 - 2,020 / 2,541

[ Back to top ]