Fターム[5F033QQ15]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | エッチングガス (483)

Fターム[5F033QQ15]に分類される特許

141 - 160 / 483

半導体加工方法

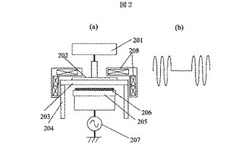

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールを形成する時に、コンタクトホールに加工不具合を生じさせることなく、ホール底の下地基板が削れることを抑制することを目的とする。

【解決手段】コンタクトホール11形成後、コンタクトホール11底面に露出したSiOC膜7を変質層12に変化させることにより、変質層12と半導体基板1の選択比大きくすることができ、選択的に変質層12をエッチング除去できるため、下地基板掘れ量を抑制し、重ね合わせずれなどが発生したときにも、基板リークの発生を抑制したコンタクトを形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】導電性プラグの上に低誘電率絶縁膜を堆積させる場合、低誘電率絶縁膜の膜厚均一性の悪化による配線のオープン不良もしくはショート不良の発生を抑え、また低誘電率絶縁膜の機械強度や密着性の低下による信頼性の低下を抑えることを目的とする。

【解決手段】半導体装置の製造方法は、半導体基板の上に、第1の絶縁膜を形成する工程(a)と、工程(a)の後に、第1の絶縁膜を貫通する導電性プラグを形成する工程(b)と、工程(b)の後に、導電性プラグの上面に保護膜を形成する工程(c)と、工程(c)の後に、第1の絶縁膜の上および保護膜の上に第2の絶縁膜を形成する工程(d)と、工程(d)の後に、保護膜の上面に達するように第2の絶縁膜を貫通する配線溝を形成する工程(e)と、工程(e)の後に、保護膜を除去する工程(f)と、工程(f)の後に、配線溝内に配線を形成する工程(g)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】パッド領域上での堆積物の生成を抑制することのできる、半導体装置の製造方法を提供する。

【解決手段】パッド領域を有する配線層群を形成するステップと、前記配線層群が被覆されるように、絶縁性のカバー層を形成するステップと、前記パッド領域が露出するように、前記カバー層をプラズマエッチングにより除去するステップとを具備し、前記パッド領域は、アルミニウムにより形成され、前記プラズマエッチングにより除去するステップは、炭素ラジカル及びフッ素ラジカルを発生させるCF系ガスを用いて、前記パッド領域を露出させるステップと、前記露出させるステップの後に、塩素ラジカル又は塩素イオンを発生させるCl2系ガスを用いて、前記パッド領域の表面に生成した堆積物を除去するステップとを備える。

(もっと読む)

パターン形成キャップを用いるエアギャップ形成と一体化

【課題】 膜をパターン形成する方法及びこれらの得られた構造を提供する。

【解決手段】 実施形態において、基板、例えば、ダマシン層の上にアモルファス炭素マスクを形成する。アモルファス炭素マスクの上にスペーサ層を堆積させ、スペーサ層をエッチングして、スペーサを形成するとともにアモルファス炭素マスクをさらす。アモルファス炭素マスクを選択的にスペーサまで除去して、基板層をさらす。ギャップ充填層がスペーサの周りに堆積されて、基板層を覆うがスペーサをさらす。スペーサを除去して、選択的に基板の上にギャップ充填マスクを形成する。ギャップ充填マスクのパターンは、一実施態様においては、ダマシン層に転写されて、IMDの少なくとも一部を除去するとともにエアギャップを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ビアホールの形成に関連する歩留まりの低下を抑制し、また、スループットを向上することができる半導体装置の製造方法を提供する。

【解決手段】絶縁性基板1上にGaN層2及びn型AlGaN層3を形成し、その後、ゲート電極4g、ソース電極4s及びドレイン電極4dを形成する。次に、ソース電極4s、GaN層2及びn型AlGaN層3に、少なくとも絶縁性基板1の表面まで到達する開口部6を形成する。次いで、開口部6内にNi層8を形成する。その後、Ni層8をエッチングストッパとするドライエッチングを高速で行うことにより、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを、冷却等によりその側壁に化合物膜19を堆積させながら形成する。そして、ビアホール1s内から絶縁性基板1の裏面にわたってビア配線16を形成する。

(もっと読む)

半導体装置の製造方法

【課題】pMOS領域のストレッサー膜の除去と、pMOS領域とnMOS領域との境界部のnMOS側への後退の抑制とを両立できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、(a)半導体基板1の上面にストレッサー13を形成する工程と、(b)ストレッサー膜13のnMOS領域上にレジスト膜15を選択的に形成する工程と、(c)レジスト膜15をマスクとして、pMOS領域のストレッサー膜13を所定の厚さだけエッチング除去し、nMOS領域のストレッサー膜13をpMOS領域のストレッサー膜13aから分離するする工程と、(d)前記エッチング除去によりnMOS領域とpMOS領域との境界部Sから露出したストレッサー膜13bを、保護膜17aにより被覆する工程と、(e)pMOS領域に残存するストレッサー膜13aをエッチング除去する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネルにおけるキャリアの移動度を向上させつつ、工程数の増加、品質の劣化およびチップサイズの増大を防ぐことができる半導体装置の製造方法を提供する。

【解決手段】Si基板1上に、PMOSトランジスタ2のチャネルに対し圧縮応力を導入する圧縮窒化膜13を形成する。次に、フッ素系ガスとO2ガスを混合した第1の混合ガスを用いて、NMOS領域5に形成された圧縮窒化膜13をエッチングする。次に、PMOS領域4では圧縮窒化膜13上に、NMOS領域5ではSi基板1上に、NMOSトランジスタ3のチャネルに対し引張り応力を導入する引張り窒化膜15を形成する。フッ素系ガスとO2ガスを混合した第2の混合ガスを用いて、PMOS領域4に形成された引張り窒化膜15を圧縮窒化膜13に対して選択的にエッチングする。この際に、第2の混合ガスのO2分圧を第1のガスのO2分圧よりも低くする。

(もっと読む)

金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFT

【課題】生産性が向上し、かつ寸法精度が良い金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFTを提供すること。

【解決手段】本発明にかかる金属配線の製造方法では、まず、主成分金属に、主成分金属より酸化物の生成エネルギーが低い添加金属が添加された第2の金属膜30を成膜する。そして、第2の金属膜30を酸化させて金属酸化物を形成し、第2の金属膜30の表面に酸化層32を形成する。次に、酸化層32上にフォトレジスト31を形成して、第1のドライエッチング条件により、酸化層32をエッチングする。そして、第1のドライエッチング条件の場合と比較して、主成分金属の金属酸化物に対する選択比が高い第2のドライエッチング条件により、下層の第2の金属膜30をエッチングする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高アスペクト比の孔または溝を穿孔する。

【解決手段】酸化シリコンからなる絶縁膜1に対して、C5F8、O2およびArのエッチングガスを用いプラズマエッチング処理を施し、絶縁膜1を選択的にエッチングすることにより、絶縁膜1に孔3を穿孔する際に、最初は、ポリマー層のデポジション性が弱い条件でエッチング処理を行い、続いてポリマー層のデポジション性が強い条件に切り換えてエッチング処理を行うようにした。

(もっと読む)

エッチングマスク形成方法、エッチング方法、および半導体デバイスの製造方法

【課題】プロセス数の低減が可能であり、プロセスの単純化が容易なエッチングマスク形成方法を提供する。

【解決手段】エッチングの対象となる対象層10上に、対象層10をエッチングするためのエッチングマスクを形成するマスク膜12を形成し、マスク膜12に転写されるべき第1のパターンを有する第1のマスク層16a,20をマスク膜12上に形成し、マスク膜12に転写されるべき第2のパターンを有する第2のマスク層22a,24を第1のマスク層上に形成し、第2のマスク層の第2のパターンを第1のマスク層に転写して、第1のパターンおよび第2のパターンを有する第3のマスク層を形成する第3のマスク層形成工程と、第3のマスク層を用いてマスク膜をエッチングして、対象層のエッチングに使用されるエッチングマスクを形成するエッチングマスク形成工程と、を含むエッチングマスク形成方法が提供される。

(もっと読む)

半導体素子、および半導体素子の製造方法

【課題】従来の半導体素子の製造方法では、半導体基板2の厚み方向のエッチングがエッチング工程とデポジション工程とを交互に繰り返して進行させられるために、規則的なくぼみが貫通孔1の側壁面に横方向の筋として発生してしまう。その結果、CVD法などにより貫通孔1の側壁面に堆積される前述の絶縁膜の、膜厚の均一性や側壁面に対する密着性が、凹凸構造3aのために悪くなってしまう。そして、その絶縁膜上に形成されるシード層の膜厚の均一性も悪くなってしまうために、続いて貫通孔1にめっき法により導電性物質を充填させることで形成される貫通電極の信頼性が低くなる現象が見られる。

【解決手段】半導体基板2と、半導体基板2に配置された回路素子と、半導体基板2に形成された、筋状の凹凸構造3をその側壁面に有する貫通孔1と、を備え、筋状の凹凸構造3の筋の方向は、半導体基板2の厚み方向である、半導体素子。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極同士の間隔が狭い場合においても、基板に損傷を与えることなく微細なコンタクトホールを安定して形成することが可能な半導体装置及びその製造方法を実現できるようにする。

【解決手段】半導体装置は、基板11の上に互いに間隔をおいて形成されたゲート電極13と、基板11の上に、ゲート電極13同士の間の領域を埋め且つゲート電極13を覆うように形成された第1の絶縁膜16と、第1の絶縁膜16の上に下側から順次形成された第2の絶縁膜17及び第3の絶縁膜18と、第1の絶縁膜16、第2の絶縁膜17及び第3の絶縁膜18を貫通し、ソース・ドレイン領域15と電気的に接続されたコンタクトプラグ22とを備えている。第1の絶縁膜16は、水素原子を含み且つフッ素原子を含まないガスによりドライエッチング可能な材料からなる。

(もっと読む)

半導体素子の金属配線及びその形成方法

【課題】埋め込み金属配線の形成時に、イン-サイチュウ(in-situ)で平坦化を行うことができ、層間絶縁膜形成の回数を減らし、製造工程にかかる時間及び費用を減らすことができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上の第1の層間絶縁膜102にコンタクトプラグ104を形成する。第1の層間絶縁膜及びコンタクトプラグの上部にエッチング停止膜106a及びハードマスクパターンを形成する。ハードマスクパターンに沿ってエッチング停止膜をパターニングし、露出された第1の層間絶縁膜及びコンタクトプラグをエッチングしてコンタクトプラグの上部の第1の層間絶縁膜にトレンチを形成する。金属膜を形成後、エッチング停止膜までシリカ研磨剤とセリア研磨剤を混合したスラリーを用いて平坦化を行い、金属配線114aを形成する。エッチング停止膜を除去し、第2の層間絶縁膜116を形成する。

(もっと読む)

エッチング方法及び半導体デバイスの製造方法

【課題】シリコン酸化膜に対するポリシリコン膜の選択比を大きくすることができ、且つシリコン基材におけるリセスの発生を抑制することができるエッチング方法を提供する。

【解決手段】シリコン基材35上にゲート酸化膜36、ポリシリコン膜37及び開口部39を有するハードマスク膜38が順に形成され、開口部39に対応するポリシリコン膜37のトレンチ40内には自然酸化膜41が形成されているウエハWにおいて、自然酸化膜41をポリシリコン膜37がトレンチ40の底部に露出するまでエッチングし、雰囲気の圧力を13.3Paに設定し、処理空間S2へO2ガス、HBrガス及びArガスを供給し、バイアス電圧の周波数を13.56MHzに設定してHBrガスから発生したプラズマによってポリシリコン膜37をエッチングして完全に除去する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、製造コストの上昇を抑えつつ、歩留まりを向上させること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1に形成される素子分離絶縁膜6と、シリコン基板1の上、及び素子分離絶縁膜6の上に形成され、素子分離絶縁膜6の上に側面13eを有する導電パターン13aと、素子分離絶縁膜6の上、導電パターン13aの上、及び導電パターン13aの側面13eに形成される絶縁膜16とを有し、導電パターン13aの側面13eにノッチ13wが形成された半導体装置による。

(もっと読む)

多層半導体ウエハの処理

パターン形成されたシリコンウエハに加工しあるいは特徴を形成する方法および装置であって、パルス幅が1psから1000psの間の第1のパルス状レーザビーム(4)を用いてウエハ上の表面層の一部を除去し、波長が200nmから1100nmの間の第2のパルス状レーザビーム(5)を用いて表面層の下にあるバルクシリコン(1)の一部をウエハから除去することを含む。再付着したシリコンはエッチングによってウエハから除去することができる。 (もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

141 - 160 / 483

[ Back to top ]