Fターム[5F033QQ20]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ウェットエッチング (1,982) | エッチング液 (265)

Fターム[5F033QQ20]に分類される特許

261 - 265 / 265

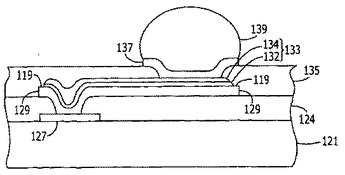

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

ボンドパッドの形成方法

パッシベーション層(68)及びポリイミド層(72)の下層には、ボンドパッド層(62)を覆うように最上層(64)が形成される。パッシベーション層(68)及びポリイミド層(72)の内部には、開口部(70,74)の形成時にボンドパッド層(62)を保護する最上層(64)を露出させるように、開口部(70,74)が形成される。一実施形態において、露出した最上層(64)は、過酸化水素及び水酸化アンモニウム等のアミンを用いて選択的にエッチングされる。この化学系は、ボンドパッド層(62)に攻撃を加えないため、ボンドパッド層の薄化が回避される。従って、ボンドパッドの信頼性が維持される。  (もっと読む)

(もっと読む)

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

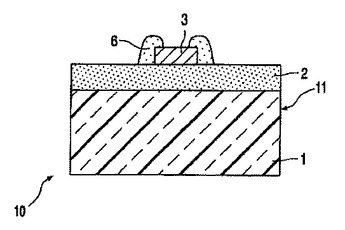

半導体デバイスを製造する方法およびその方法で使用するための装置

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

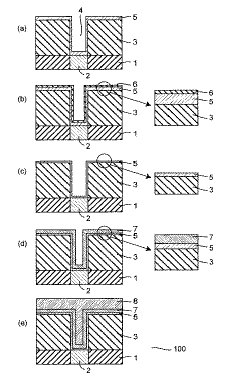

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

261 - 265 / 265

[ Back to top ]