Fターム[5F033QQ43]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | リフトオフ (276) | リフトオフ材 (96) | フォトレジスト以外 (19)

Fターム[5F033QQ43]に分類される特許

1 - 19 / 19

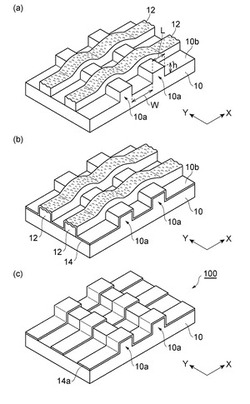

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 選択性トップバリアを用いた配線におけるリークを抑制することができ、配線の信頼性の向上をはかる。

【解決手段】 埋め込み配線を有する半導体装置の製造方法であって、配線間絶縁膜102上に該絶縁膜102とは材料の異なる犠牲膜103を形成した後、犠牲膜103及び配線間絶縁膜102を選択的にエッチングして配線用溝105を形成し、次いで配線用溝105内にCuを主成分とする導電膜107を埋め込み形成し、次いで導電膜107の上面に選択的にトップバリア層108を形成し、次いで犠牲膜103を除去することによりメタル残渣108aを除去する。

(もっと読む)

導電部材の形成方法、電子デバイスの製造方法、および、電子デバイス

【課題】基板に与える損傷を抑制できる導電部材の形成方法を提供する。アンダーカットの発生を抑制できる導電部材の形成方法を提供する。

【解決手段】基板を準備する段階と、基板の少なくとも一部を覆うリフトオフ層を形成する段階と、リフトオフ層に、基板の表面の一部を露出させる第1開口部を形成する段階と、リフトオフ層と第1開口部に露出した基板の表面とを覆うシード層を形成する段階と、シード層の表面に、レジスト層を形成する段階と、レジスト層に、少なくとも一部が第1開口部と重なり、かつ、シード層の一部を露出させる第2開口部を形成する段階と、第2開口部の内部に、導電部材を形成する段階と、レジスト層の少なくとも一部を除去する段階と、リフトオフ層をリフトオフ法により除去して、レジスト層とリフトオフ層との間のシード層を除去する段階とを備える。

(もっと読む)

マイクロパターンの製造方法

【課題】基板上にマイクロパターンを高精度にかつ容易に形成することを可能とするマイクロパターンの製造方法を得る。

【解決手段】 マイクロパターンが上面6aに形成される基板6と、前記マイクロパターンに対して反転されたパターン形状を有するフィルム状パターニング材1Aとを用意する工程と、前記フィルム状パターニング材1Aを前記基板6の上面に積層する工程と、前記フィルム状パターニング材1Aが積層された基板6の上面に被パターニング材料7を塗布する工程と、前記基板6の上面6aから前記フィルム状パターニング材1Aを除去して、前記フィルム状パターニング材1Aと反転されたマイクロパターンとなるように前記被パターニング材料7をパターニングし、それによって、被パターニング材料7からなるマイクロパターン7Aを形成する工程とを備える。

(もっと読む)

パターン形成方法

【課題】本発明の課題は、膜応力の発生により、リフトオフ層としてのレジスト層が下地絶縁膜から剥離し、その露呈部分に不要な金属膜が付着してもショート不良になることを防止できるパターン形成方法を提供する。

【解決手段】本発明のパターン形成方法は、ソース電極20上にPSGからなる下地絶縁膜23を形成し、その上に、金属膜パターン(TiNiAg)と異なるエッチング選択比を有する金属としてのAlからなる第2の金属層102を形成し、その上にリフトオフ層となるレジスト層24を形成し、レジスト層24に所定パターンの開口24aを形成し、これをマスクとして、第2の金属層102および下地絶縁膜23を順次、ウェットエッチングして開口102aおよび開口23aを形成し、その上から金属膜25を被着後、レジスト層を溶解させ、その上の不要な金属膜を除去した後、第2の金属層102をエッチング除去する。

(もっと読む)

電気光学装置製造方法

【課題】電気光学装置の端子部において界面抵抗の増加を抑制することである。

【解決手段】電気光学装置である液晶表示装置の下基板の画素部14において、画素用接続配線24、画素用透明導電膜28の導電積層膜が形成され、端子部20において、端子用接続配線124、端子用透明導電膜128の導電積層膜が形成される。ここで、画素用接続配線24と端子用接続配線124とは同一工程で形成され、下層側から上層側に向かって、チタン/アルミニウム/チタンがこの順に積層されて構成される。その後に平坦化膜64と保護絶縁膜62の開口部処理が行われ、表面エッチング液によって最上層のチタンの表面生成物が除去される。そして、画素用透明導電膜28と端子用透明導電膜128とが同一工程で形成される。

(もっと読む)

カーボンナノチューブに基づく層間配線要素

【課題】カーボンナノチューブと層間配線される導体との間に良好な電気的接触を付与するカーボンナノチューブに基づく層間配線要素を提供する。

【解決手段】マイクロエレクトロニクス回路の少なくとも2つの導体を層間配線するために設計された要素であって、下側導体と称する初期導体210と、前記初期導体に配置された誘電層230と、前記誘電層上の上側導体と称する第2の導体220と、一方で下側導体上に、そして他方で上側導体上に現れる誘電層における空洞240とを含む、要素に関連する。上側導体220は下側導体210の上方にブリッジを形成しており、空洞240はそれが上側導体上に現れる水平面で後者の両側に2つのベント243を形成している。

(もっと読む)

半導体装置の作製方法

【課題】レジストを使用することなく、薄膜加工を簡単な工程で精度良く行う方法を提案する。また、低コストで半導体装置を作製する方法を提案する。

【解決手段】基板上に第1の層を形成し、第1の層上に剥離層を形成し、剥離層側から剥離層に選択的にレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去し、残存した剥離層をマスクとして第1の層を選択的にエッチングする。また、基板上に剥離層を形成し、少なくとも剥離層に選択的に第1のレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去する。次に、残存した剥離層上に第1の層を形成し、残存した剥離層に第2のレーザビームを照射して残存した剥離層の付着力を低減させ、残存した剥離層及び当該剥離層に接する第1の層を除去する。

(もっと読む)

MIMキャパシタを含む半導体集積回路素子およびその製造方法

【課題】キャパシタンス値が所定値以上に高く、VCCが所定値以下に維持されるMIMキャパシタを含む半導体集積回路装置を提供する。

【解決手段】活性領域を含む半導体基板、基板の上面の一部に形成され、絶縁領域を定義する絶縁物、共通のコンダクタ層からパターニングされ基板上に形成され、絶縁物上に形成された第1パターン部と、活性領域上に形成され活性領域内に形成されたトランジスタのゲートを含む第2パターン部を含むコンダクタ層パターン、前記第2パターン部は前記活性領域内に形成されたトランジスタのゲートを含み、コンダクタ層パターンの前記第1パターン部上に形成された下部電極、下部電極上に形成された誘電層パターン、および誘電層パターン上に形成された上部電極を含む絶縁領域内のキャパシタを含む半導体集積回路素子とその製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】金属膜をウェハ表面に成膜する際に周辺エッジ部および裏面に回り込み、次工程の装置の搬送アームが金属膜に接触することにより装置が二次汚染されることを防止する。

【解決手段】半導体基板11の表裏面に犠牲膜13を成膜し、裏面と周辺エッジ部のみ犠牲膜を残す。半導体基板の表面に金属膜15を成膜した後、半導体基板の裏面から薬液を吐出し、犠牲膜を全てエッチングする。このときリフトオフ効果により、金属膜における半導体基板のエッジ部上と裏面側にまで回りこんで形成された部分を除去する。これにより、不要な金属膜がエッジ部に残存して装置間の金属汚染が拡大することを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線構造をパターン形成した際に発生した不要な残存物を容易且つ確実に除去し、信頼性の高い半導体装置を実現する。

【解決手段】配線膜1上に、Al2O3(アルミナ)、SiON、Al窒素酸化物、Ta酸化物、及びTi酸化物よりなる群から選ばれた少なくとも一種の材料からなる犠牲剥離膜40を形成し、第1の配線45をパターン形成した後、フッ化アンモニウム、アミド、有機酸、有機酸塩類、及び水を含有する薬液を用いて、ウェットエッチングにより残存物50を除去する。

(もっと読む)

パターン化された材料層及びこれの形成方法、並びにマイクロデバイス及びこれの製造方法。

【課題】 真空成膜法を用いた方法であって、厚みが大きくパターン化された材料層を、容易にその側面が基板となす角度を垂直等の任意の角度とすることのできる方法を提供すること。

【解決手段】 基板1上に、中間樹脂層22を有するレジスト層2を形成するレジスト層形成工程と、レジスト層2に所定のパターンを露光する露光工程と、基板1が露出するトレンチを形成するとともに当該トレンチ側面に溝23が形成されるように中間樹脂層22を除去して、レジストフレームを形成する現像工程と、材料パターン部分31及び被リフトオフ部分32を有する真空成膜層3を真空成膜法により形成する真空成膜工程と、被リフトオフ部分32をレジストフレームとともに除去して、材料パターン部分31を有する材料パターンを得るリフトオフ工程とを備える、パターン化された材料層の形成方法。

(もっと読む)

半導体装置およびその製造方法

【課題】 プラグと配線との接続抵抗および絶縁膜の誘電率を効果的に低下させる。

【解決手段】 半導体装置100は、半導体基板(不図示)と、半導体基板の上部に設けられ、銅含有金属により構成される第一配線108と、第一配線108の上部に設けられ、第一配線108に接続する導電性の第一プラグ114と、第一配線108の上部において、第一プラグ114が設けられた領域以外の領域に設けられたCuシリサイド層111と、第一プラグ114の上部に設けられたCuシリサイド層117と、第一配線108の側面から第一プラグ114の側面にわたって形成されるとともに、第一配線108の側面と、第一配線108の上部と、第一プラグ114の側面とを被覆する第一ポーラスMSQ膜105と、を含む配線構造を有する。

(もっと読む)

1 - 19 / 19

[ Back to top ]