Fターム[5F033QQ64]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入するもの (714) | 窒素系 (42)

Fターム[5F033QQ64]に分類される特許

21 - 40 / 42

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングによるアルミニウム配線形成後、反応生成物を除去することにより、エレクトロマイグレーション、ストレスマイグレーションの少ない、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】基板11上に、絶縁膜12を介してアルミニウム膜17を形成する。アルミニウム膜をマスク材18を用いてドライエッチングし、アルミニウム配線15を形成する。マスク材を除去した後、アルミニウム配線の少なくとも側壁に形成された反応生成物19にArをイオン注入し、反応生成物に欠陥を発生させる。ウェットエッチングによりアルミニウム配線の表層をエッチングし、反応生成物を浮き上がらせて剥離する。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの解像限界以上で、かつ、寸法制御性に優れた超微細パターンを容易に形成する。

【解決手段】パターニングすべき第1の膜として、例えばアモルファスシリコン膜13を形成し、このアモルファスシリコン膜13上にラインとスペースの比率が略3:1のパターン14、17を形成し、次いで、パターン14、17をマスクとしてアモルファスシリコン膜13を加工し、次いで、パターン14、17を両側から幅が略1/3となるまでスリミングした後、このスリミングされたパターンの反転パターン層として、例えばBSG膜18を形成し、次いで、このBSG膜18をマスクとしてアモルファスシリコン膜13を再加工して、ラインとスペースの比率が略1:1で、かつ、ピッチが元の略半分のパターンを形成する。

(もっと読む)

ドライクリーニング方法、基板処理装置、半導体装置の製造方法及び記憶媒体

【課題】被処理基板中の構造体に熱ストレスが加わり難いドライクリーニング方法を提供すること。

【解決手段】 酸化銅、及び有機汚染物質の少なくともいずれか一方が基板表面に形成、もしくは付着した被処理基板をチャンバ内に設置する工程(ステップ1)と、チャンバ内の雰囲気を有機化合物ガス雰囲気として被処理基板の基板表面にガスクラスターイオンビームを照射し、基板表面に形成、もしくは付着した酸化銅、及び有機汚染物質の少なくともいずれか一方を除去する工程(ステップ2)とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ビアホールに於ける肩落ちを低減させる為、トレンチのエッチング加工途中でビアホールの側壁に保護膜を形成するのであるが、その形成工程段階を適切に選定することで、保護対象を有効に保護できるようにする。

【解決手段】低誘電率材料であるポーラスシリカからなる絶縁膜14(無機膜)を用いてデュアルダマシン加工方法を実施する場合に於いて、トレンチ24形成のエッチングを行なう際に発生するビアホール23開口エッジの肩落ちを低減させる目的で成膜される側壁保護膜31の被覆性を向上させる為、その成膜を前記エッチングの途中段階で実施する工程が含まれる。

(もっと読む)

半導体装置とその製造方法

【課題】新規な特徴を有する半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25の所定の深さに不純物をイオン注入することにより、第1絶縁膜25に不純物層22を形成する工程と、不純物層22を形成した後、第1絶縁膜をアニールすることにより、不純物層22をバリア絶縁膜23に改質する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Cu配線10を、その中央部のCu粒子10aが比較的大きく、その上部や下部のCu粒子10aが比較的小さくなるような構造にする。このような構造は、Cu配線10をダマシン法により形成する際の電解めっき時の電流密度を制御することによって形成することができる。このような構造にしたCu配線10では、その上部よりも中央部に比較的電流が流れやすくなり、その上部のCu原子の拡散が抑えられるようになり、また、それにより、キャップ膜14界面からのCu原子の拡散が抑えられるようになる。

(もっと読む)

薄膜トランジスタ基板、および表示デバイス

【課題】バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極28,29とを有する薄膜トランジスタ基板において、ソース−ドレイン電極28,29は、窒素を含有する窒素含有層、または窒素及び酸素を含有する酸素窒素含有層28a、29aと、純Cu又はCu合金の薄膜28b、29bとからなっている。窒素含有層を構成する窒素の一部若しくは全部、または、酸素窒素含有層を構成する窒素または酸素の一部若しくは全部は、薄膜トランジスタの半導体層33のSiと結合している。また、純CuまたはCu合金の薄膜28b、29bは、窒素含有層または酸素窒素含有層28a、29aを介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明はトランジスタのソース・ドレイン拡散層と配線を多結晶シリコンによって接続したコンタクトプラグを有する半導体装置に関し、特に拡散層中に残留する欠陥を低減して接合リーク電流を減少できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、トランジスタのソース拡散層及び又はドレイン拡散層へのコンタクトが多結晶シリコンのコンタクトプラグである半導体装置において、前記ソース拡散層及び又はドレイン拡散層と多結晶シリコンのコンタクトプラグの間に格子間シリコンまたは空孔の拡散を防止する拡散防止膜を形成した。

(もっと読む)

半導体装置の製造方法

【課題】 制御電極と電荷蓄積層との間に優れた絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11上に形成された第1の絶縁膜12と、第1の絶縁膜上に形成された電荷蓄積層13と、電荷蓄積層上に形成された第2の絶縁膜20と、第2の絶縁膜上に形成された制御電極とを備えた半導体装置の製造方法であって、第2の絶縁膜を形成する工程は、酸素及び金属元素を含有した下層絶縁膜201を形成する工程と、下層絶縁膜に対して酸化性ガスを含む雰囲気下で熱処理を施す工程と、熱処理が施された下層絶縁膜上に水素及び塩素の少なくとも一方を含んだ成膜ガスを用いて上層絶縁膜202を形成する工程とを備える。

(もっと読む)

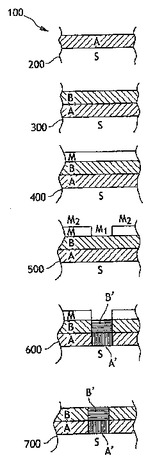

特性が制御された多層構造物の製造方法

本発明はn層の所定材料の元素状活性層(nは2以上の整数)を含む多層構造物を支持体上に製造する方法(100)に関する。この方法は、第1の元素状材料活性層の成膜工程(200)と、n番目の元素状材料活性層の成膜工程(300)とを含む方法であって、特性が制御された多層構造物を得るために、成膜されたn層の材料元素状活性層上に、n層の元素状活性層のそれぞれの個々の特性を変性させるのに適したイオン種をレジストを介して注入する単一の工程(600)を含むことを特徴とする。  (もっと読む)

(もっと読む)

集積回路配線形成方法、拡散バリア形成方法並びに窒化層形成方法

【課題】 集積回路配線に拡散バリア層を形成する方法を提供する。

【解決手段】 集積回路10の銅又は金の配線18の上に、物質を電着し、その少なくとも一部を、窒素と電着物質から成る層22に変質する。変質は、電着物質を窒素含有プラズマに晒すことで行われる。窒化クロム及び酸窒化クロムが、窒素含有物質の例である。電着及び変質の間の処理温度は、500℃を超えない範囲で選択される。一例として、集積回路10の銅配線18は、配線18上にクロムを堆積するため電流が供給されている間、クロムイオン含有環境に晒される。クロムは、窒素含有プラズマを用いて窒化クロム含有拡散バリア22に変質される。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

ウエハレベルで層間絶縁膜の厚さの均一性に優れた半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)シリコン基板上方に配線を形成する工程と、(b)配線を埋め込んで、HDP−CVDにより第1の絶縁膜を堆積する工程と、(c)HDP−CVD以外の堆積方法により、第1の絶縁膜上方に第2の絶縁膜を堆積する工程と、(d)2酸化セリウム砥粒を含む研磨剤を用いた化学的機械的研磨により第2の絶縁膜を平坦化する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 銅イオンの拡散防止機能を持つ低誘電率の層間絶縁膜の成膜初期における銅配線からの銅イオンの拡散を防止する。

【解決手段】 半導体装置の製造方法は、基板上の絶縁膜(1)に形成された銅配線(3b)における露出部位に、窒素を含む層(4a)を形成する。その後、シロキサン(Si−O−Si)結合を有する有機シリコン化合物を原料として用いて、プラズマCVD法により、窒素を含む層(4a)の上に層間絶縁膜(5)を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】Cu配線上にバリア膜を有する半導体装置において、ストレスマイグレーション、エレクトロマイグレーションの劣化を防止する。

【解決手段】本発明の半導体装置は、絶縁膜内に形成された配線溝内に埋め込まれた導電膜を有する配線層と、配線表面に形成されたバリア膜と、バリア膜上に形成された上層配線層とを備える。また、絶縁膜とバリア膜は接しており、導電膜とバリア膜の間にはSi,Cを含むアモルファス層が形成されていることを特徴とする。Siにより導電膜とバリア膜の結合性を高め、アモルファス層中の空孔をSi,Cで埋めるため、配線層とバリア膜の密着性を向上することが出来る。これにより、Cu配線のエレクトロマイグレーション、ストレスマイグレーション耐性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線及びパターンの特定箇所を選択的に細らせて配線間隔を広げ、カバレッジの良い成膜条件でもエアギャップを形成することができ、所望の配線間の静電容量を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】 隣接するフローティングゲート電極層について互いの距離が上層から下地基板面までの間で徐々に離れるように上層から下地基板面へ向けて互いの層形状を選択的に細らせ、互いの距離が離れたフローティングゲート電極層の間にエアギャップを有する層間絶縁膜を備える。

(もっと読む)

低誘電率絶縁膜および半導体装置の製造方法

【課題】 半導体装置を構成する絶縁膜の比誘電率を低下させることができる方法を提供する。

【解決手段】 半導体装置を構成する絶縁膜2に不活性ガス、窒素および水素の内の少なくとも一種のイオン6を注入して絶縁膜2中に多数の空隙8を形成し、絶縁膜2の比誘電率をイオン注入前よりも低下させ、これによって低誘電率絶縁膜10を得る。

(もっと読む)

半導体装置の製造方法

【課題】シリコン内に形成されたシーム部を熱処理により消滅させることにより、シーム部が外部に露出することを防止して、シリコン膜をエッチバックした後に残渣が残ることを防止することができ、また、エッチングを良好に行うことができると共に、シリコン膜上を酸化する際にシリコン膜内も酸化されることを防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板10の主表面側に形成された凹部にシリコン膜を堆積する工程と、シーム部51が形成されたシリコン膜50に1000℃以上にて熱処理を施す工程とを備える。

(もっと読む)

21 - 40 / 42

[ Back to top ]