Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

1,801 - 1,820 / 5,243

カーボンナノチューブ系材料の先端部形成方法

【課題】CNT系材料と他の導電体との低接触抵抗を実現でき、あるいは他の導電体との接触に高い信頼性が確保できる技術を提供する。

【解決手段】凹所に設置され、その凹所上の空間にその先端部が突き出たCNT系材料のその突き出た先端部に、酸化性物質であるまたは酸化性物質を発生しうるガス状物質を接触させつつ、活性エネルギー線を照射する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

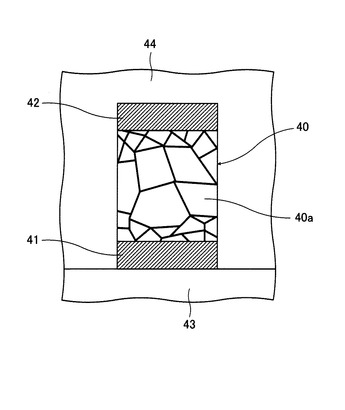

トランス素子が形成されている半導体装置とその製造方法

【課題】トランス素子のコイル間絶縁膜をSiO2で形成すると、形成範囲を規制するのが困難である。有機質絶縁材料を利用すれば形成範囲を自在に調整できが、厚くなってしまい、2次側コイルに生じる電圧が小さくなる。

【解決手段】半導体基板上に、下側コイル135とコイル間絶縁膜140と上側コイル154の積層構造でトランス素子155が形成されている。コイル間絶縁膜140が絶縁性無機質粒子の集積物で形成されている絶縁層141aを備えている。絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、必要な耐圧特性を得るのに必要な厚みが薄くてすむ。従って、1次側コイル154と2次側コイル135の磁気的結合係数を高め、2次側コイル135に大きな電圧を生じさせることができる。しかも、絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、コイル間絶縁膜の形成範囲を規制しやすい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ裏面に貫通電極および裏面配線を形成すると、貫通電極の一部である裏面配線パッドおよび裏面配線によって、チップ裏面に凸部が形成される。これが原因で、チップ吸着時に空気のリークが起こりチップ吸着力の低下が起きる。

【解決手段】裏面配線パッド4dおよび裏面配線4eを形成する領域に、あらかじめ凹部100を形成する。この凹部100内部に裏面配線パッド4dおよび裏面配線4eを設ける。これにより、裏面配線パッド4dおよび裏面配線4e厚さのため生じる凸部によって、チップ1C裏面の平坦性が確保され、チップ1Cを取り扱う際の吸着力の低下が起きない。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

半導体装置

【課題】配線とビアとの界面でのボイドの発生を抑制し、信頼性に優れた半導体装置を提供すること。

【解決手段】半導体装置1は、比誘電率が3.0以下の低誘電率の絶縁膜112中に形成され、配線幅が0.1μm以下の配線14と、配線14に接続された径が0.1μm以下のビア17と、絶縁膜112中に形成されたダミーメタル15とを有し、ダミーメタル15は、配線14の端部に対し、配線14の延在方向に沿って隣接し、ダミーメタル15と、配線14との間の距離Dが0.3μm以下である。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウエハの主面上に形成した絶縁膜の膜厚分布を均一にする。

【解決手段】半導体ウエハ1の主面上にゲート絶縁膜4を介してゲート電極6を形成し、このゲート電極6を覆うように層間絶縁膜としての絶縁膜12を形成する。絶縁膜12には、ゲート電極6に起因して凹凸形状が形成されているため、CMP処理で平坦化する。このCMP処理は、半導体ウエハ1の主面の周辺部1Aは、主面の中央部1Bに比べて、研磨量が大きくなる傾向にある。このため、半導体ウエハ1の主面において、CMP処理時の研磨量が少ない領域よりも、研磨量が多い領域で、絶縁膜12の膜厚が厚くなるように、ウェットエッチングにより絶縁膜12の膜厚分布を補正してから、絶縁膜12をCMP処理して平坦化する。CMP処理後の絶縁膜12の膜厚は周辺部1Aと中央部1Bでほぼ同じになる。

(もっと読む)

半導体装置

【課題】積層された第1インダクタと第2インダクタの間の絶縁耐圧を高くする。

【解決手段】基板10上には、多層配線層400、第1インダクタ310、及び第2インダクタ320が形成されている。多層配線層400は、絶縁層及び配線層をこの順にそれぞれt回(t≧3)以上交互に積層したものである。第1インダクタ310は、多層配線層400の第n配線層に設けられている。第2インダクタ320は、多層配線層400の第m配線層(t≧m≧n+2)に設けられ、第1インダクタ310の上方に位置している。第n配線層と第m配線層の間に位置するいずれの配線層にも、第1インダクタ310の上方に位置するインダクタが設けられていない。第1インダクタ310及び第2インダクタ320は、電気信号を相互に伝達する信号伝達素子300を構成している。

(もっと読む)

CMOSイメージセンサの製造方法

CMOSイメージセンサにおいて相互接続の層間剥離によるヒルロックタイプのピデフェクトの発生を回避可能なCMOSイメージセンサの製造方法が開示されている。CMOSイメージセンサの製造方法は、第1の金属相互接続を有する基板を準備するステップと、第1の金属相互接続上に中間層の絶縁層を形成するステップと、中間層の絶縁層をエッチングすることにより第1金属相互接続の一部を露光するためのコンタクトホールを形成するステップと、コンタクトホールの内側表面に沿って中間層の絶縁層上にバッファ層を形成するステップと、アニール処理を行うステップと、バッファ層をエッチングすることによりコンタクトホールの側壁にスペーサを形成するステップと、スペーサを有す、中間層の絶縁層の頂面に沿ってバリア金属層を形成するステップと、コンタクトホールがコンタクトプラグで埋められるようにバリア金属層上にコンタクトプラグを形成するステップと、および第2の金属相互接続がコンタクトプラグと接触するように中間層の絶縁層上に第2の金属相互接続を形成するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】2つの導電体間の寄生容量、または導電体と基板との間の寄生容量の低減を実現しながら、機械的強度を保つことができる構造を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2と、半導体基板2上に形成された、第1層金属配線11及び第2層金属配線16と、第1層金属配線11と第2層金属配線16との間に形成された、第1層間絶縁膜12及び第2層間絶縁膜14とを備え、第1層金属配線11と第2層金属配線16とは、第1層間絶縁膜12及び第2層間絶縁膜14を挟む半導体装置1において、第1層間絶縁膜12及び第2層間絶縁膜14の、第1層金属配線11と第2層金属配線16とで挟まれた領域は、空隙13を有する。

(もっと読む)

半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有し、容易に製造することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1領域と第2領域を有する半導体基板と、第1領域の半導体基板上方に配置されたMTJと、MTJを覆うように配置され、第2領域上方よりも第1領域上方の膜厚が薄い絶縁膜と、絶縁膜中に配置され、MTJと電気的に接続された導電膜と、第1領域上方の絶縁膜上方に形成され、導電膜と電気的に接続されたビット線と、第2領域上方の絶縁膜上方に形成された配線と、を備える。

(もっと読む)

貫通プラグ配線

【課題】半導体チップの基板を貫通するプラグにおいて、微細になるとプラグに接続する電極との接続抵抗が大きくなる、またリーク電流が大きくなる、あるいは絶縁破壊やストレスマイグレーションが生じる、という問題があった。これらの問題の生じにくい貫通プラグの製造方法を提供する。

【解決手段】半導体基板100の表面に設けられた電極パッド400と、基板裏面に設けられた接続電極380とを電気的に接続する貫通プラグ350の端部が、電極パッドおよび接続電極に部分的に食い込んだ構造とする。および、半導体基板から貫通プラグを絶縁する絶縁分離部210が、半導体基板表面側の絶縁膜205に部分的に食い込んだ構造とする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】F添加カーボン膜を層間絶縁膜として使った多層配線構造ににおいて、開口部内のバリアメタル膜とF添加カーボン膜との反応を抑制し、配線と絶縁膜の密着性を向上させた半導体装置の製造方法を提供する。

【解決手段】開口部44A内のF添加カーボン膜44の露出表面に、Taバリアメタル膜47の堆積に先立って、少なくとも前記開口部の側壁面および底面を覆うように、Fと反応した場合に安定な化合物を形成するAlなどの金属元素よりなる金属膜49を堆積する。

(もっと読む)

半導体装置

【課題】細幅配線間のTDDB寿命の低下、および細幅配線間のショートによる歩留まり低下を抑制する半導体装置を提供する。

【解決手段】半導体装置10は、ダマシン配線からなる配線層を有し、0.5μm以上の幅を有する第1の配線12と、前記第1の配線12に隣接し前記第1の配線12から0.5μm未満の間隔で配置された第2の配線14と、前記第2の配線14に隣接し前記第1の配線12から0.5μm以下の間隔で配置された第3の配線16と、を備え、前記第2および第3の配線は同電位を有するよう構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】導電パターンと貫通電極の間の抵抗を低くし、かつ貫通電極と裏面電極であるバンプを一体に形成することができる半導体装置を提供する。

【解決手段】この半導体装置において、貫通孔102は、基板100に形成され、導電パターン120の下に位置している。絶縁層110は、貫通孔102の底面に位置している。導電パターン120は、基板100の一面側に位置している。開口パターン112は、貫通孔102と導電パターン120の間に位置する絶縁層110に形成されており、周から貫通孔102の中心軸までの距離r3が貫通孔102における距離r1より小さい。開口パターン112が設けられることにより、貫通孔102の底面に導電パターン120が露出している。バンプ302は、基板100の裏面側に位置しており、貫通電極300と一体に形成されている。

(もっと読む)

シリコン基板、デバイスの製造方法、デバイスおよびテスト方法

【課題】表面平坦性と金属汚染ゲタリング機能を確保しながら、STIと共存できる製造工程で500V以上の広い電圧領域の電気的アイソレイションを実現するとともに、貫通電極全体の深さにいたる物理的な金属移動の阻止のためのアイソレイシヨン構造を有する。

【解決手段】シリコン酸化膜を1um以上の幅で1um以上に深い溝を作り、溝の中にシリコン酸化膜を埋め、結晶欠陥のある基板でも500V以上に耐圧のあるアイソレイションを実現する。これによりシャロートレンチアイソレイションで高速で動作する既存デバイスと同一基板に電力デバイスを混載させることが可能となる。また、厚いアイソレイション材料で囲まれたシリコンを除去した空洞にメタルを埋め、金属汚染の拡散を防止した基板貫通電極を形成することにより、基板の積層を可能にする。これにより、電源からの配線を基板貫通で供給することで、ヒートシンクを兼ねた電力給電と、これにより動作する大電力デバイスと高速高集積のデバイスを積層させたデバイスを実現させる。

(もっと読む)

半導体装置の製造装置及びその製造方法

【課題】Al合金膜のシリコン残渣が除去できて、製造工程の簡素化、製造コストが低減される半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法はシリコン基板1上にシリコンを含有するAl合金膜3を形成する工程と、Al合金膜3上にレジストパターン4を設ける工程と、レジストパターン4をマスクとしてAl合金膜3をエッチングする工程と、エッチ後洗浄する工程と、2流体ノズル6によってシリコン残渣5を除去する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】従来の半導体装置の製造方法には、さらなる効率化が困難であるという課題がある。

【解決手段】第1基板41に設けられた第1半導体層51の表示面側に、平面視で第1半導体層51の一部に重なる第1導電パターン107を形成する工程と、第1導電パターンをマスクとして第1半導体層51に不純物を注入する第1注入工程と、前記第1注入工程の後に、第1導電パターン107の一部を除去して、第1導電パターン107と第1半導体層51とが平面視で重なる領域である第1重畳領域113aを縮小する縮小工程と、前記縮小工程の後に、ゲート電極部57をマスクとして第1半導体層51に前記不純物を注入する第2注入工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

1,801 - 1,820 / 5,243

[ Back to top ]