Fターム[5F033SS07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621)

Fターム[5F033SS07]の下位に属するFターム

Fターム[5F033SS07]に分類される特許

101 - 109 / 109

ハイパフォーマンスメタライゼーションキャップ層

【課題】 ハイパフォーマンスメタライゼーションキャップ層を提供する。

【解決手段】 非導電性のキャップ層を有する半導体デバイス100の、第一金属成分からなる非導電性のキャップ層112は、導電線と導電線間の絶縁材料上の、第一窒化金属、第一酸化金属、或いは、酸窒化金属からなる。界面領域114は、導電線の上表面上に形成され、界面領域114は、キャップ層の金属成分を含む。キャップ層112は、導電線中の導電材料が、近接する絶縁材料層中に移動、或いは、拡散するのを防止する。キャップ層112は、エッチ停止層としても機能する。

(もっと読む)

半導体素子の金属配線形成方法

【課題】既存の金属配線パターンマスクを用いてダマシン工程を実施しながら層間絶縁膜の幅を最大限確保し、金属配線間の間隔を広めて相互干渉を防止することにより、半導体素子の誤動作を防止することが可能な半導体素子の金属配線形成方法を提供する。

【解決手段】絶縁膜11〜14の形成された半導体基板を提供する段階と、金属配線パターンマスクを用いたエッチング工程によって前記絶縁膜をパターニングして溝を形成するが、前記エッチング工程の際に発生するポリマーの量を制御し、パターニングされる前記絶縁膜の上部コーナー部位にラウンディング(rounding)16を形成する段階と、前記溝が埋め込まれるように金属配線を形成する段階と、このラウンディング部が除去されるようにCMP工程により全体構造上部を平坦化する段階を含む。

(もっと読む)

半導体装置の製造方法

【課題】パターン寸法のバラツキの少ない、配線容量の低減されたデュアルダマシン配線を、高い歩留まりで形成可能な半導体装置の製造方法を提供する。

【解決手段】基板20上に、有機系絶縁膜4を形成する工程と、有機系絶縁膜上に、無機材料を含む第1および第2のハードマスク5,6を形成する工程と、第2のハードマスクに凹部を形成する工程と、凹部が形成された第2のハードマスク上に、下層膜12、中間層13およびレジスト膜14を順次形成する工程と、レジスト膜をパターン露光する工程とを具備する方法である。前記下層膜は、前記第2のハードマスク上に第1の有機膜9を形成し、第1の有機膜を、スラリーを用いて化学的機械的に研磨して第2のハードマスクの表面を露出し、凹部に前記第1の有機膜を選択的に残置し、第2のハードマスクおよび第1の有機膜上に、第2の有機膜11を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

デュアル・ダマシン構造におけるMIMキャパシタの構造および製作方法

【課題】MIM(金属−絶縁体−金属)キャパシタ(242/252)構造およびそれを形成する方法を提供すること。

【解決手段】第1パターン(216)および第2パターン(218)を有するデュアル・ダマシン・パターンで、半導体デバイス(200)の誘電体層(214)をパターニングする。第2パターン(218)は、第1パターン(216)よりも深い。第1パターン中の誘電体層(214)の上に導電層(226)を形成し、第1パターン(216)中のこの導電層の上に導電層を形成する。第2パターン(218)の導電層(226)の上に、誘電体層(232)、導電層(234)、誘電体層(236)、および導電層(238)を配設する。導電層(234)、誘電体層(232)、および導電層(226)が、第1のMIMキャパシタ(252)を形成する。導電層(238)、誘電体層(236)、および導電層(234)が、第1のMIMキャパシタ(252)に並列な第2のMIMキャパシタ(242)を形成する。  (もっと読む)

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

成膜方法、SiO2膜、電子部品および電子機器

【課題】所定パターンのSiO2膜を容易かつ安価に形成し得る成膜方法、かかる成膜方法により形成されたSiO2膜、このSiO2膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、所定パターンの第2の層間絶縁層(SiO2膜)5を形成する方法であり、主としてポリオルガノシロキサンで構成されるポリオルガノシロキサン膜を形成する第1の工程と、ポリオルガノシロキサン膜の前記所定パターンに対応する領域に、第1のSiO2化処理を施して、前記領域に存在するポリオルガノシロキサンをSiO2に変化させる第2の工程と、SiO2に変化した前記領域をアルカリ溶液により除去する第3の工程と、第3の工程において残存するポリオルガノシロキサン膜に、第2のSiO2化処理を施して、ポリオルガノシロキサンをSiO2に変化させることにより、第2の層間絶縁層5を得る第4の工程とを有する。

(もっと読む)

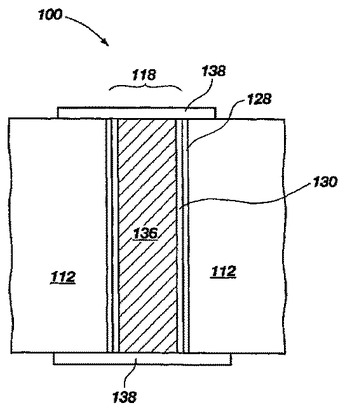

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

ボンドパッドの形成方法

パッシベーション層(68)及びポリイミド層(72)の下層には、ボンドパッド層(62)を覆うように最上層(64)が形成される。パッシベーション層(68)及びポリイミド層(72)の内部には、開口部(70,74)の形成時にボンドパッド層(62)を保護する最上層(64)を露出させるように、開口部(70,74)が形成される。一実施形態において、露出した最上層(64)は、過酸化水素及び水酸化アンモニウム等のアミンを用いて選択的にエッチングされる。この化学系は、ボンドパッド層(62)に攻撃を加えないため、ボンドパッド層の薄化が回避される。従って、ボンドパッドの信頼性が維持される。  (もっと読む)

(もっと読む)

101 - 109 / 109

[ Back to top ]