Fターム[5F033SS07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621)

Fターム[5F033SS07]の下位に属するFターム

Fターム[5F033SS07]に分類される特許

21 - 40 / 109

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

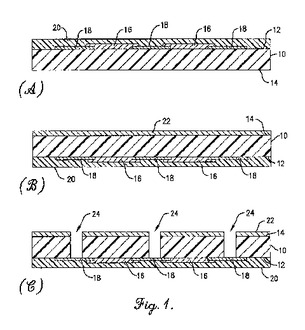

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーション

【課題】AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーションを提供する。

【解決手段】集積回路は、ボンディングパッド領域と非ボンディングパッド領域とを有する基板からなる。“大ビア”と称される相対して大きいビアが、ボンディング領域の基板上に形成される。大ビアは、基板向きの上面図にて、第一寸法を有する。集積回路は、非ボンディング領域の基板上に形成された複数のビアも有する。複数のビアは、それぞれ、上面図にて、第二寸法を有し、第二寸法は、第一寸法より相当小さい。

(もっと読む)

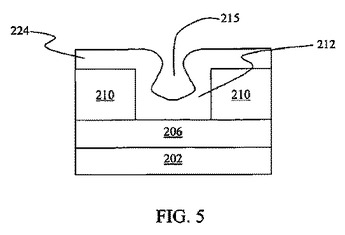

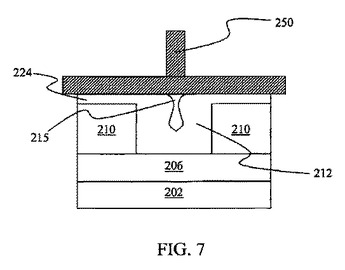

半導体デバイスおよびその構造体の製造方法

【課題】集積回路の配線間に空隙を形成することにより、容量成分が低減された半導体装置の製造方法を提供する。

【解決手段】基板202上に第1の絶縁材が堆積され、この上に、犠牲部分を有する第2の絶縁材232が堆積される。上記第1および第2の絶縁層内に、導電線210がダマシン法により形成される。犠牲部分となる第1の絶縁材を除去するために第2の絶縁材が処理され開口部238が形成される。そして第1の絶縁材が除去されて、導電線間に空隙242が形成される。第2の絶縁材は、堆積時には不透過性であるが、処理後により透過性とし、これを介して犠牲部分を除去する。第2の絶縁材の処理はエッチングによる開口、あるいは熱感受性成分のアニールによる除去である。

(もっと読む)

配線層レイアウト方法及び半導体装置

【課題】配線層にスリットを設けたり、下層に位置する配線層にライン幅及びスペース間隔の比率を制限したりすることなく、SOG膜を含む層間絶縁膜におけるクラックの発生を防止する。

【解決手段】下地絶縁膜3上に第1配線層5が形成されている。下地絶縁膜3上及び第1配線層5上に第1層間絶縁膜7が形成されている。回転塗布法及びエッチバック処理により第1層間絶縁膜7上に第2層間絶縁膜9が形成されている。第1層間絶縁膜7上及び第2層間絶縁膜9上に第3層間絶縁膜11が形成されている。第3層間絶縁膜11上に第2配線層13が形成されている。第1配線層5のうち幅寸法が10.0μm以上の幅広第1配線層5に対して、第2配線層13のうち幅寸法が10.0μm以上の幅広第2配線層13は、上方から見て、幅広第1配線層5と1.0μm以上の重なりをもって配置されているか、幅広第1配線層5とは2.0μm以上の間隔を設けて配置されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線間容量の低い半導体装置を安定的に形成する。

【解決手段】配線1間に、仕切層5aで仕切られた複数の空洞の溝2を形成し、その後、それらの溝2を覆うように、配線1及び仕切層5aの上側に絶縁膜を形成する。配線1間に仕切層5aを設けることにより、絶縁膜形成に用いる絶縁膜原料3aの溝2内への進入が抑えられ、溝2内の絶縁膜形成が抑えられるようになる。それにより、配線1間の容量が低く、また、容量のばらつきが抑えられた半導体装置が形成可能になる。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

積層構造体、電子素子及び電子素子アレイ

【課題】印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能で、かつ、パターン形成以外に高付加価値機能を有する積層構造体を提供する。

【解決手段】積層構造体1は、臨界表面張力が大きい高表面エネルギー部3と臨界表面張力が小さい低表面エネルギー部4を有する濡れ性変化層2と、高表面エネルギー部3に形成されている導電層5と、低表面エネルギー部4に形成されている半導体層6と、を有し、濡れ性変化層2は、エネルギーの付与により臨界表面張力が変化する、側鎖に疎水性基を有する高分子材料を含み、高分子材料は、ポリイミドを含む。

(もっと読む)

透明薄膜トランジスタ及び画像表示装置

【課題】配線抵抗を低下させて、均一かつ確実に動作させる透明薄膜トランジスタ及び画像表示装置を提供すること。

【解決手段】実質的に透明な基板と、基板上に実質的に透明な導電材料の第1の薄膜と金属材料の第2の薄膜とを2層以上積層して形成されたゲート配線と、ゲート配線上に形成された実質的に透明なゲート絶縁膜と、ゲート絶縁膜上に形成された実質的に透明な半導体活性層と、実質的に透明な半導体活性層を挟んで離間して形成された実質的に透明な導電材料の第5の薄膜と金属材料の第6の薄膜とを2層以上積層して形成されたソース配線と、実質的に透明な半導体活性層を挟み、ソース配線に離間して実質的に透明な導電材料の第7の薄膜で形成されたドレイン電極と、を備えることを特徴とする透明薄膜トランジスタ。

(もっと読む)

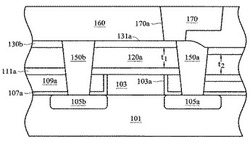

マイクロ電子構造体、マルチチップモジュール及びそれを含むメモリカードとシステム並びに集積回路素子の製造方法

【課題】ビア電極を効果的に配しうるマイクロ電子構造体、マルチチップモジュール、メモリカード及び集積回路素子の製造方法を提供する。

【解決手段】基板110と、前記基板上に提供され、貫通して延長される第1及び第2開口を含む導電性パッド130と、前記導電性パッド上に提供され、前記導電性パッド内の前記第1開口を貫通して前記基板内に延長される第1導電性ビア電極150と、前記導電性パッド上に前記第1導電性ビア電極に隣接するように提供され、前記導電性パッド内の前記第2開口を貫通して前記基板内に延長される第2導電性ビア電極160とを有する。

(もっと読む)

ハードマスク及び二重露光により形成される半導体デバイスのコンタクト及びビア

【解決手段】

コンタクト要素がハードマスク(233)に基いて形成されてよく、ハードマスク(233)は、第1のレジストマスク(210)に基いて及び第2のレジストマスク(211)に基いて、コンタクト要素の最終的な設計寸法を代表し得る適切な交差区域(234)を画定するようにパターニングされてよい。その結果、横方向寸法の少なくとも一方は2つのレジストマスクの各々における非臨界的寸法として選択され得るので、それほど制限的ではない制約を伴うフォトリソグラフィプロセスに基いてレジストマスクの各々を形成することができる。

(もっと読む)

集積回路構造、そのスタック構造及びこれらの製造方法

【課題】導電性電極の連結信頼性を高めることができる集積回路構造、スタック構造及びこれらの製造方法を提供する。

【解決手段】第1面106上の少なくとも一つの導電性パッド120と、少なくとも一つの導電性パッド及び集積回路基板105を貫通する貫通ホールとを持つ集積回路基板である。少なくとも一つの導電性電極150は、貫通ホール内に前記導電性パッドを貫通して前記導電性パッド上に延び、その内部に該第2面107から露出されたボイド160aを備える。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】工程効率が向上し、かつ、信頼性が向上した酸化物半導体薄膜トランジスタ基板とその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、絶縁基板上に形成され、ゲート電極を含むゲート線と、ゲート線と交差しドレイン電極接続部を含むデータ線と、ゲート電極の周辺に形成される酸化物半導体活性層パターンと、データ線と酸化物半導体活性層パターンの上に形成されドレイン電極接続部を露出する第1開口部、及び酸化物半導体活性層パターンを露出する第2開口部を有するパシベーション層と、第1開口部及び第2開口部によって酸化物半導体活性層パターンとドレイン電極接続部とを電気的に接続するドレイン電極とを含む。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法を提供する。また、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜を形成する方法を提供する。また、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】ガリウムと亜鉛を含む液滴を吐出して、基板上に膜パターンを形成する。または、印刷法により、基板上にガリウムと亜鉛を含む材料を用いて膜パターンを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】パターンの3次元形状を大気圧下にて非破壊、非接触、高いスループットをもって高精度に測定することができ、高精度な形状寸法管理がなされた半導体装置およびその製造方法を提供する。

【解決手段】チップ形成領域102内の複数の検査領域に検査用パターンを形成する加工工程181と、検査工程とを含み、検査用パターンが、第1検査領域103aに形成された繰り返しパターン112と、第2検査領域103bに形成された一様なパターン113とを有し、検査工程が、3次元のパターン形状を測定可能な光学的測定法を用いて、第1検査領域103aにおける繰り返しパターン112のパラメータを測定する第1検査と、膜の膜厚を測定可能な光学的測定法を用いて、第2検査領域103bにおける一様なパターン113の膜厚を測定する第2検査とを含むパターン検査工程を少なくとも有することを特徴とする半導体装置の製造方法。

(もっと読む)

金属ヒューズ、アンチヒューズ及び/又は抵抗器を含む金属ゲート統合構造体及び方法

【課題】 個々の半導体デバイス・コンポーネントの統合の強化、製造性の向上をもたらす、半導体構造体及びそれらの半導体構造体を製造する方法を提供する。

【解決手段】 半導体構造体及び半導体構造体を製造するための方法が、半導体基板の活性領域上に配置及び形成された電界効果デバイスと、半導体基板内の活性領域から横方向に分離された分離領域上に少なくとも部分的に同時に配置及び形成された、ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つとを提供する。電界効果デバイスは、高誘電率の誘電体材料を含むゲート誘電体と、金属材料を含むゲート電極とを含む。ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つは、ゲート誘電体と同じ材料を含むパッド誘電体と、随意的に、同様にゲート電極と同じ金属材料を含むことができるヒューズ、アンチヒューズ又は抵抗器とを含む。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

21 - 40 / 109

[ Back to top ]