Fターム[5F033SS07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621)

Fターム[5F033SS07]の下位に属するFターム

Fターム[5F033SS07]に分類される特許

81 - 100 / 109

半導体装置

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題とする。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体装置の製造方法、電子機器の製造方法、半導体装置および電子機器

【課題】半導体装置の製造工程において、エッチング量のモニタ精度を向上させる。

【解決手段】絶縁膜(バンク)13によって所望の形状に区画された領域(開口部OA1)内に、膜厚の異なる検査パターン17a〜17dを形成し、TFTを構成するゲート絶縁膜17のエッチング工程のモニタとして使用し、例えば、ゲート絶縁膜17と同等もしくはゲート絶縁膜より若干厚い膜厚の検査パターン(例えば17c)が消失した時点で、エッチングを終了する。

(もっと読む)

CMOS対応の浅いトレンチのeフューズ構造体及びその製造方法

【課題】 少なくとも1つのeヒューズを含む半導体構造体と標準的な半導体技術との統合が容易であり、よって実施コストが最小になる製造方法を提供する。

【解決手段】 半導体基板(バルク又は半導体オン・インシュレータ)内に配置されたトレンチ内に埋め込まれた少なくとも1つのeヒューズを含む半導体構造体が提供される。本発明によると、eヒューズは、半導体基板内に配置されたドーパント領域と電気接触した状態にある。本発明はまた、埋め込まれたeヒューズが、トレンチ分離領域とほぼ同時に形成される半導体構造体を製造する方法も提供する。

(もっと読む)

成膜方法及び成膜装置

【課題】例えアスペクト比が高く、深さが深いビアホール等の凹部にあっても、銅等の金属材料を、内部にボイドを発生させることなく、凹部内に高速かつ確実に埋込むことができるようにする。

【解決手段】凹部202を有し該凹部202の内部を含む表面に通電層206を形成した基板Wを用意し、凹部202の内部を除く通電層206の表面に電着法で高分子絶縁膜208を形成し、高分子絶縁膜208を形成した基板Wの表面に電解めっきを行って凹部202内に金属材料210を埋込む。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜をLow−k膜で構成し、低比誘電率を維持したままLow−k膜の密着性を向上させて膜剥がれ等を抑制できる、信頼性の高い半導体装置を提供することにある。

【解決手段】半導体基板と、前記半導体基板上方に形成され、表面に複数の配線からなる第1配線層が形成された第1絶縁膜と、前記第1配線層及び前記第1絶縁膜上に形成された第1キャップ層と、前記第1キャップ層上に形成され、表面に複数の配線からなる第2配線層が形成され、前記第2配線層間に前記第1キャップ層まで達する溝部が形成された第2絶縁膜と、前記溝部に埋め込まれた第3絶縁膜とを備え、前記第3絶縁膜の前記第1キャップ層に対する密着性が、前記第2絶縁膜と前記第1キャップ層との密着性よりも高い構成とするので、Low−k膜の密着性を向上させて、効果的に膜剥がれ等を防止することを可能にできる。

(もっと読む)

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

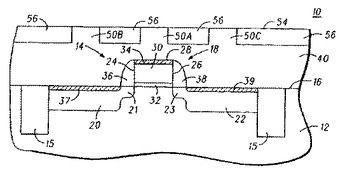

犠牲マスキング構造を用いた半導体装置の製造方法

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】素子が微細化された場合においても、強誘電体キャパシタの特性劣化を抑制し、あるいは、その特性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の上方に設けられた強誘電体キャパシタと、強誘電体キャパシタの側面を被覆する絶縁性の保護膜と、保護膜を介して強誘電体キャパシタの側面に設けられ、強誘電体キャパシタにかかる電界方向へ該強誘電体キャパシタに引張応力を与える側壁膜とを備え、側壁膜はシリコン窒化膜からなる。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

電子デバイスのレーザアブレーション

本発明は、レーザアブレーションを使った電子デバイスの製造方法と、それによって製造されたデバイスに関する。方法の実施形態は特にステップ−アンド−リピートモードでレーザアブレーションを使って薄膜トランジスタ(TFT)構造内に電極を規定するのに適している。電子デバイスを製造する方法であって、該デバイスは基板上の複数のレイヤからなり、該レイヤは上部導電レイヤと該導電レイヤと該基板の間の少なくとも1つのパターニングされた下部レイヤを含み、前記方法は、前記下部レイヤをパターニングし、前記上部導電レイヤを、連続的に印加されたレーザパターンによって前記上部導電レイヤの連続したエリアを剥離するステップ状プロセスを使ってレーザアブレーションによりパターニングすることからなり、前記連続的に印加されたレーザパターンは重複領域で互いに重複し、前記方法は更に、前記重複領域において前記パターニングされた下部レイヤが前記ステップ状レーザアブレーションによって実質的に損傷を受けないように、前記レーザパターンと前記パターニングされた下部レイヤを互いに構成することからなる電子デバイスを製造する方法。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 本発明は、TFTを用いる表示装置及びデータを無線で送受信する機能を持った半導体装置の製造工程においてフォトリソグラフィ工程の回数を削減することを目的とする。また、より簡略化された製造工程で、電気的特性の高いTFT、表示装置及びデータを無線で送受信する機能を持った半導体装置等に代表される電子機器を作製する。低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 基板上に塗れ性が低い層と、塗れ性が低い層に比べて塗れ性が高い領域を形成し、塗れ性が高い領域上に導電性粒子を有する組成物を塗布と焼成を繰り返して凸状の導電層を形成することを特徴とする。

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路におけるRC遅延の容量成分Cを低くするための改良された方法の提供。

【解決手段】基板上に犠牲膜となる第1の絶縁材が堆積され、該第1の絶縁材上に、犠牲部分を有する第2の絶縁材が堆積される。上記第1および第2の絶縁層をパターニングして導電性材料を蒸着し余剰な導電材を除去して導電線が形成される。上記犠牲部分を除去するために上記第2の絶縁材の内部に気孔または開口部を形成して、透過性とする。この気孔または開口を通じて第1の絶縁材が除去され、上記導電線間に空隙が形成される。上記処理後に、第2の絶縁膜と導電膜の上にキャップ層を形成する。この結果、導電線間に空隙が形成される。

(もっと読む)

有機シリコン系膜の形成方法、及び有機シリコン系膜を有する半導体装置

【課題】 比誘電率が低いと共にリーク電流が少ない有機シリコン系膜を得易い有機シリコン系膜の形成方法を提供する。

【解決手段】 原料ガスとして少なくとも1種の有機シリコン化合物を用いた化学的気相堆積法により有機シリコン系膜を成膜するにあたり、前記有機シリコン化合物として、少なくともケイ素、水素、炭素、及び窒素を構成元素として含有していると共に、ケイ素原子と窒素原子とが互いに結合していない化合物を用いることによって、上記課題を解決した。

(もっと読む)

半導体集積回路の製造方法及び半導体集積回路

【課題】 上下の配線層を複数のビアを用いて接続する場合に、複数のビアの周辺に隣接する配線を敷設可能とし、信頼度及び歩留まりを向上可能な半導体集積回路の製造方法及び半導体集積回路を提供する。

【解決手段】 チップ領域8上に下層配線パターン31b及び下層配線パターン31bの上層に上層配線パターン41dをそれぞれ配置するステップと、上層配線パターン41dの長手方向に直交する方向に第1迂回パターン62a及び第2迂回パターン63aとを含む迂回パターン160aを下層及び上層配線パターン31b,41dのいずれかに設定するステップと、下層及び上層配線パターン31b,41d間を接続する複数のビアパターン71a,72aを設定するステップと、迂回パターン160a及びビアパターン71a,72aによりビアセルパターン130bを作成するステップを含む。

(もっと読む)

バリアで内側が覆われた半導体コンポーネントを製造する方法

薄い共形のマルチ層バリア構造を含むメタライゼーションシステムを有する半導体コンポーネント(10)およびこの半導体コンポーネント(10)を製造する方法である。下にある階層の相互接続構造上に絶縁材料(30)(34)を形成する。この絶縁材料(30)(34)上にハードマスク(36)を形成し、このハードマスク(36)を貫通して絶縁層(30)(34)中に開口部(50)(52)(54)をエッチングする。この開口部(50)(52)(54)を、原子層たい積を使用して薄い共形のマルチ層バリア(60)でその内側を覆う。このマルチ層バリアで内側が覆われた開口部を導電材料(66)で充てんする。この導電材料(66)はプレーナ化される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

強誘電体キャパシタ(23)を形成した後、表面の傾斜が緩やかな絶縁膜(24)を、高密度プラズマCVD法又は常圧CVD法等により形成する。その後、アルミナ膜(25)を絶縁膜(24)上に形成する。このような方法によれば、アルミナ膜(25)のカバレッジの低さが問題となることはなく、強誘電体キャパシタ(23)が確実に保護される。  (もっと読む)

(もっと読む)

半導体装置の製造装置

【課題】 本発明は上記問題を解決するためになされたもので、空孔を有する低誘電率絶縁膜上にバリアメタルを成膜する前におけるビア底の高抵抗層の除去手段として、プラズマを用いない新規な半導体装置を製造する装置を提供することにある。

【解決手段】 本発明は、層間膜に比誘電率の値が3未満の低誘電率膜(102)を用いた金属膜配線(103)を含む半導体装置を製造する装置であって、前記金属膜配線(103)と前記層間膜の間に形成されるバリアメタルを成膜する前に、還元性を有するガスもしくは還元性を有するガスを含む混合ガスで熱還元処理に当たって、チャンバーを有し、且つ前記還元性を有するガスの配管を温調してガス導入することを特徴とする。

(もっと読む)

多孔性低k誘電体フィルムの紫外線に補助された細孔シーリング

【課題】多孔性低k誘電体フィルムの紫外線に補助された細孔シーリングを提供する。

【解決手段】多孔性低k誘電体フィルムをシールする方法であって、炭化、酸化及び/又は高密度化の手段により、多孔性誘電体の表面をシールするために有効な強度、時間、波長及び雰囲気中において、多孔性低k誘電体フィルムの多孔性表面を紫外線(UV)照射に暴露することから一般的になる方法。表面の多孔性低k材料の表面は、紫外線暴露後に該表面に実質的に開孔が存在しないよう約20ナノメーター未満又は約20ナノメーターに等しい深さでシールされる。

(もっと読む)

半導体装置の形成方法およびその構造

ダミーフィーチャ(64,65,48a,48b)が、層間誘電体層(36)内に形成される。一実施形態では、非ギャップ充填誘電体層(72)がダミーフィーチャ(64,65,48a,48b)上に形成され、ダミーフィーチャ(64,65,48a,48b)間、またはダミーフィーチャ(48a)と導電領域(44)間に空隙(74)を形成する。一実施形態では、パッシベーション膜(32および54)が無電解めっきによって形成され、下層にある導電性領域(44,48a,48b,および30)をエアギャップ(74)が貫通するのを保護する。さらに、パッシベーション膜(32および54)は、下層にある導電性領域(44,48a,48b,および30)に覆い被さって、それにより、導電性領域(44,48a,および48b)に隣接するダミーフィーチャ(65a,65b,および67)を画定する。パッシベーション膜(32および54)は、追加のパターニング工程なしに形成することができ、ミスアライメントビアがエアギャップを貫通するのを極力低減する。  (もっと読む)

(もっと読む)

多孔質膜の堆積方法

【課題】基板上に多孔質膜を堆積させる処理方法を提供する。

【解決手段】多孔質シリカ膜及びドープシリカ膜を堆積させる処理方法。本方法は、循環方式を用い、各サイクルは、最初にシリカをシリコンと共に共堆積させる段階と、次に選択的にシリコンを除去して多孔質構造体を形成する段階とを含む。好ましい実施形態では、共堆積は、プラズマ強化化学気相蒸着によって行われる。反応剤給送流れは、共堆積反応剤と選択的シリコン除去反応剤との混合物を含む。RF電力変調を使用して、共堆積段階及び選択的シリコン除去段階を制御し、後者は、RF電力が切られるか又は低レベルに低減される度に進行する。本発明を用いて、高度に均一な小さな孔隙及び望ましい空隙率プロフィールを有する多孔質膜を取得することができる。本方法は、半導体集積回路製造のための広範囲の低−k誘電体を形成するのに有利である。本方法はまた、他の用途のための他の多孔質膜を形成するのにも有利である。

(もっと読む)

81 - 100 / 109

[ Back to top ]