Fターム[5F033SS07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621)

Fターム[5F033SS07]の下位に属するFターム

Fターム[5F033SS07]に分類される特許

41 - 60 / 109

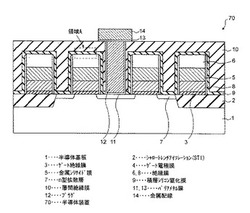

半導体装置の製造方法、半導体装置

【課題】半導体装置に適用される比較的膜厚の厚い絶縁膜中の水素濃度を大幅に低減する。

【解決手段】半導体装置70には、半導体基板1上に複数のメモリセルトランジスタが設けられる。n型拡散層7、シャロートレンチアイソレーション(STI)2、及び絶縁膜6上と、側壁絶縁膜8の側面とには積層シリコン窒化膜9が形成される。メモリセルトランジスタのゲートの周囲に積層シリコン窒化膜9が設けられる。積層シリコン窒化膜9は、例えば膜厚が略100nmであり、n層のシリコン窒化膜から構成される。n層のシリコン窒化膜の膜厚は、それぞれ3nm以下に設定される。n層のシリコン窒化膜は、それぞれ膜中の水素結合がプラズマ処理で置換され、水素が離脱され、膜中の水素濃度が大幅に低減されたシリコン窒化膜である。

(もっと読む)

薄膜およびその薄膜を用いた半導体装置の製造方法

【課題】ニッケルシリサイドを始め他の膜をエッチングすることなく、速やかに半導体装置に利用される側壁スペーサ等の薄膜を除去可能とする薄膜を提供すること。

【解決手段】半導体装置の製造過程で用いられる薄膜であって、薄膜は、ゲルマニウム、珪素、窒素、及び水素を含む。

(もっと読む)

相互接続構造のための貴金属キャップおよびこれを形成する方法(相互接続構造のための貴金属キャップ)

【課題】 誘電率が約3.0以下の誘電材料(52)を含む相互接続構造を提供する。

【解決手段】 この低k誘電材料は、上面が埋め込まれた少なくとも1つの導電材料(60)を有する。また、誘電材料は、貴金属キャップ(62)の形成前に疎水性とされた表面層(52B)を有する。貴金属キャップは、少なくとも1つの導電材料の上面上に直接に配置されている。誘電材料上に疎水性表面層が存在するために、貴金属キャップは、少なくとも1つの導電材料に隣接した誘電材料の疎水性表面層上に実質的に延出せず、この疎水性の誘電表面上に貴金属キャップ堆積からの貴金属残留物は存在しない。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を低減しつつ有機膜を平坦化して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に設けられ凹部を有する絶縁膜の上に、溶剤と有機成分とを含む溶液を塗布して塗膜を形成する工程と、前記塗膜を、前記有機成分の架橋が終了しない第1の温度でベークして有機膜前駆体を得る工程と、前記有機膜前駆体を、樹脂粒子を含有するスラリーを用いて研磨して前記凹部内に残置する工程と、前記研磨に引き続いて、前記有機膜前駆体を前記第1の温度より高い第2の温度でベークして前記溶剤を除去し、前記凹部内に埋め込まれた第1の有機膜19を得る工程と、前記第1の有機膜が埋め込まれた絶縁膜の上に、塗布法により第2の有機膜20を形成して下層膜を得る工程と、前記下層膜の上に中間層22及びレジスト膜23を順次形成する工程と、前記レジスト膜をパターン露光する工程とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線に十分なEM耐性を確保しつつ、配線層間・線間リークを低減しかつTDDB寿命を向上することができるとともに、ビアエッチの際に高選択比を確保して高信頼性な配線を得ることができる半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板上の第1の絶縁膜1に形成された配線溝M1と、配線溝M1側壁及び底部に形成されたタンタル系バリアメタル2aと、タンタル系バリアメタル2aに沿って配線溝M1を埋め込むように形成されたCu膜2bと、Cu膜2b表面に形成された銅とシリコンの合金層または銅とシリコンと窒素のCuSiN層3aと、CuSiN層3aの上及び第1の絶縁膜1の上に形成され第1の絶縁膜1より高密度なSiNx膜3dとを有する。

(もっと読む)

導電性クラッディング部を有する、ドープされた半導体ラインを含む集積回路

【課題】メモリセルアレイのメモリセルを選択する配線の抵抗率を低減することにより、配線中の電圧降下を低減し、消費電力を低減する半導体ラインの構造を提供する。

【解決手段】集積回路は、各メモリセルのアレイと半導体基板内に形成されたドープされた各半導体ライン202とを含む。上記ドープされた各半導体ライン202は、各メモリセルのロウに結合されている。上記集積回路は、上記ドープされた各半導体ライン202に接触している導電性クラッディング部203を含む。

(もっと読む)

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】アンダーフィルを用いることなく、半導体装置の高い実装信頼性を提供する。

【解決手段】能動素子10と、能動素子10に形成される電極12と、電極12に接続される導電層15と、導電層15上に形成された絶縁層16とを有し、導電層15の上部が絶縁層16から露出され、導電層15が露出される部分において、導電層15と絶縁層16とに段差が設けられる半導体装置を構成する。

(もっと読む)

半導体装置、およびその製造方法

【課題】ビアの径を調節するスペーサ膜と、ビア間絶縁膜上に形成されたエッチングストッパ膜を有し、スペーサ膜とエッチングストッパ膜の界面におけるリーク電流の発生を抑えた半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、表面に半導体素子を有する半導体基板と、前記半導体基板上に形成された配線と、前記配線の下側に接続されるビアと、前記ビアと同じ層に形成された第1の絶縁膜と、前記第1の絶縁膜と前記配線との間、および前記第1の絶縁膜と前記ビアとの間に一体に形成された第2の絶縁膜と、を有する。

(もっと読む)

カーボンナノチューブベースの電気的接続の製造方法

【課題】デュアルダマシン構造にも適用出来る好ましくはカーボンで作られるナノチューブによるビアの形成法を提供する。

【解決手段】底部と、側壁とを備える、少なくとも1つのビアを、金属材料の2つの層4及び12を隔てる絶縁材料層5の中に形成する。次いで接着層7及び/又は保護層8の上に触媒層9を堆積する。さらに抑止層11を、前記ビアの前記底部における前記触媒層9の部分を除く、前記ビアの前記ビアの側壁の上と、前記絶縁材料層5の上に方向性堆積によって形成する。ナノチューブを前記抑止層11のない前記ビア底部の前記触媒層9の部分から成長させて前記金属材料の2つの層4及び12を電気的に接続する。

(もっと読む)

自己集合ナノ構造をパターン化する方法及び多孔性誘電体層を形成する方法(自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法)

【課題】 自己集合ナノ構造をパターン化しそして多孔性誘電体層を形成する方法を提供する。

【解決手段】 自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法は、1つの態様において、下側層を覆ってハードマスク層を設けるステップと、パターン化の間に保護されるべきハードマスク層の領域をフォトレジスト層により予め画定するステップと、ハードマスク層及びフォトレジスト層を覆って共重合体層を形成するステップと、共重合体層から自己集合ナノ構造を形成するステップと、自己集合ナノ構造をパターン化するためにエッチングするステップとを含む。

(もっと読む)

金属配線形成方法

【課題】本発明は、低価の工程が可能であり、低い電気抵抗を提供できる金属配線の形成方法を提供することを目的とする。

【解決手段】

(a)基板上部に誘電体層を蒸着する段階;(b)前記誘電体層上部に金属配線の潜在的マスクパターンを形成する段階;(c)前記潜在的マスクパターンにより露出された誘電体層をエッチングする段階;(d)前記基板を活性化処理して表面にシード層を形成する段階;(e)前記潜在的マスクパターンおよびその上部をリフトオフして除去する段階;および(f)上記ターン形成されたシード層上部に金属層をめっきする段階を含む金属配線形成方法と前記方法により製造された金属配線構造および前記構造を含む薄膜トランジスタ−液晶ディスプレーを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】紫外線から受けるダメージを抑制することができ、且つ、小型化にも対応することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に設けられたシリコン粒子36を含む第1絶縁膜40と、半導体基板10と第1絶縁膜40との間に設けられた電荷蓄積層14を含むONO膜からなる第2絶縁膜34と、第2絶縁膜34と第1絶縁膜40との間に設けられたゲート電極20と、ゲート電極20を挟むように半導体基板10内に設けられたビットライン22と、を具備する半導体装置およびその製造方法である。

(もっと読む)

半導体パッケージ、その製造方法、半導体パッケージを利用したパッケージモジュール及び電子製品

【課題】貫通電極と導電性パッドとを電気的に連結すると同時に、貫通電極と半導体基板とを絶縁させることによって信頼性を高めた半導体パッケージを提供する。

【解決手段】第1面1051及び第2面1052を持つ半導体基板105と、半導体基板105の第1面上1051の層間絶縁層115と、層間絶縁層115の一部分上の導電性パッド120と、第2面1052から半導体基板105を貫通して伸張する第1部分、及び第1部分から層間絶縁層115を貫通して導電性パッド120と電気的に連結された第2部分を備える貫通電極155と、半導体基板105から貫通電極155の第1部分を分離するスペーサ絶縁層145と、を備える。

(もっと読む)

半導体装置及び半導体装置内に空洞を形成する方法(核化防止層を使用する選択的なピンチ・オフを有する空隙)

【課題】配線用の導電体相互間のクロストークを減少した半導体装置を提供する。

【解決手段】半導体装置内に空洞を形成する方法が開示される。本発明の方法は、半導体装置のILD層内の空洞の内面上に核化防止層を付着することを含む。この核化防止層は、後に付着される誘電体層が空洞内に付着することを防止する。誘電体層が空洞内に付着することを防止することにより、キャパシタンスが減少され、これにより、改善された半導体動作特性を実現する。

(もっと読む)

半導体素子の製造方法

【課題】絶縁膜の比誘電率が小さくて高速応答性に優れ、かつ、絶縁膜の機械的強度にも優れ、更には配線の信頼性が高い半導体素子を提供することである

【解決手段】膜2に凹部3を形成する工程を有する半導体素子の製造方法において、前記凹部3を形成した後、該凹部が形成された膜2に電磁エネルギを照射する照射工程を有する。

(もっと読む)

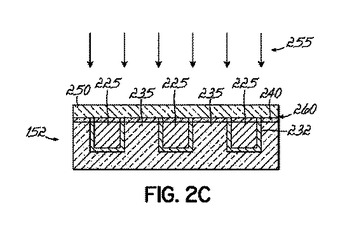

不揮発性メモリの第1層間誘電体スタック

略均一な厚さの保護ゲッタリング層(72)を有する第1層間誘電体(ILD0)スタックを形成する方法および装置について記載する。基板(31)上にデバイス部品(32,33)を形成した後、PEN ESLのエッチング停止層(42)の上方に、SATEOSの間隙充填誘電体層(52)を堆積する。SATEOSの間隙充填誘電体層(52)を平坦化してから、平坦化した間隙充填誘電体層(52)上にBPTEOSのゲッタリング層(72)およびキャッピング誘電体層(82)を堆積する。ILD0スタックを形成すると、ILD0スタックに対して一つまたは複数のコンタクト開口部(92,94,96)をエッチングする。これにより、所望のコンタクト領域上方でエッチング停止層(42)が露出する。  (もっと読む)

(もっと読む)

フッ素系薄膜の成膜方法及び半導体装置の製造方法

【課題】低誘電率且つ化学的に安定なフッ素系薄膜を成膜することができるフッ素系薄膜の成膜方法及び該成膜方法を用いた半導体装置の製造方法の提供。

【解決手段】本発明のフッ素系薄膜の成膜方法は、基板上にフッ素系樹脂からなる薄膜を成膜するフッ素系薄膜の成膜方法であって、前記基板上にガスを照射するガス照射工程と、前記フッ素系樹脂をプラズマ化するプラズマ化工程とを含む。イオン化蒸着法、イオンプレーティング法、レーザアブレション法、イオンビームスパッタ法から選択される少なくとも1種によりフッ素系樹脂からなる薄膜を成膜する態様等が好ましい。

(もっと読む)

貫通ビアによって前面接点に接続された後面接点を有するチップ

超小型電子ユニットを提供する。このユニットでは、半導体要素(100)の前面(102)および後面(114)が、第1の厚みを有する薄い領域(105)および第1の厚みの少なくとも約2倍の厚みを有する厚い領域を画定しているとよい。半導体素子(112)は、前面に位置し、前面における複数の第1の導電接点(116)が、この素子に接続されているとよい。複数の導電ビア(125)が、後面から半導体要素の薄い領域(105)を通って第1の導電接点(116)に延在しているとよい。複数の第2の導電接点(134)を半導体要素(100)の外部に露出させることができる。複数の導電トレース(126)が、これらの第2の導電接点(134)を導電ビア(125)に接続しているとよい。  (もっと読む)

(もっと読む)

2層金属キャップを有する相互接続構造体及びその製造方法

【課題】 2層金属キャップを有する相互接続構造体を製造するための構造及び方法を提供する。

【解決手段】 1つの実施形態において、本方法は、誘電体材料層内に相互接続構造部を形成するステップ、及び、相互接続構造部の上面に2層金属キャップを形成するステップを含む。本方法は、誘電体材料層の露出面及び2層金属キャップの表面を覆う、誘電体キャップ層のブランケット層を堆積するステップを更に含む。2層金属キャップは、相互接続構造部の導電面上に形成された金属キャップ層、及び金属キャップ層の頂部に形成された金属窒化物を含む。また、誘電体層内に形成された相互接続構造部、相互接続構造部の頂部に形成された2層金属キャップ、及び、2層金属キャップを覆って形成された誘電体キャップ層を有する相互接続構造体を含む。

(もっと読む)

41 - 60 / 109

[ Back to top ]