Fターム[5F033TT03]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが有機材料 (79)

Fターム[5F033TT03]に分類される特許

61 - 79 / 79

半導体装置及びその製造方法並びに電子装置

【課題】 外部基板へ実装した際に、接続不良を低減できる半導体装置を提供する。

【解決手段】 本発明に係る半導体装置1は、一面に電極を配してなる半導体基板2と、 半導体基板1の一面を覆うように配され、かつ、前記電極が露呈するように開口部を有すると共に、厚さが異なる部分を有する中間層21と、中間層21を覆い、外部基板との接続領域に配された第一導電部6A、6aと、前記開口部を通して前記電極と第一導電部6A、6aとを電気的に接続する第二導電部と、第一導電部6A、6aに接合されるバンプ9A、9aと、を少なくとも備え、第一導電部6A、6aが配された中間層21の厚さに応じて体積の異なるバンプ9A、9aを有する。図1に示す構成例は、第一中間層4に第二中間層5を重ねた厚い中間層21上に配されるバンプ9Aが、第一中間層4のみからなる薄い中間層21上に配されるバンプ9aに比べて、小さな体積を有する場合を示す。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、電子機器、及びアクティブマトリクス基板の製造方法

【課題】幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】本発明の膜パターンの形成方法は、基板18上に第1バンク層35と第2バンク層36とを積層形成する工程と、前記第1バンク層35及び第2バンク層36をパターニングすることで、第1のパターン形成領域55と、該第1のパターン形成領域55に連続し、かつ該第1のパターン形成領域55より幅が広い第2のパターン形成領域56とからなるパターン形成領域13を有するバンク34を形成する工程と、を有し、前記パターン形成領域13に臨む前記第1バンク層35の側壁35sの接触角が、水を含む機能液に対して50°未満であり、前記第2バンク層36の接触角が前記第1バンク層35の接触角より大きい角度である前記バンク34を設けることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 本発明の目的は、導電性の密着性の向上及びマイグレーションの防止を図ることにある。

【解決手段】 半導体装置の製造方法は、(a)電極パッド16及びパッシベーション膜18を有する半導体基板10の上方に、複数回のパターニング工程を行うことにより、少なくとも電極パッド16側が階段状をなす樹脂層40を形成する工程と、(b)樹脂層40をキュアすることにより、樹脂突起41を形成する工程と、(c)電極パッド16と電気的に接続し、かつ樹脂突起41の上方を通る導電層50を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】配線材料となるCuの拡散を防止し、配線間リークが少なく、又、凹凸が少なく、それだけ信頼性が高く、更には配線プロセスが簡略化され、コストがそれだけ低廉なものになる半導体装置を提供することである。

【解決手段】基板1と、前記基板1上に設けられたCu配線層8,19と、前記Cu配線層8,19上に設けられた層間絶縁層9,20とを具備する半導体装置であって、前記層間絶縁層9、20がCu拡散防止機能を有する塗布型絶縁膜である。

(もっと読む)

半導体相互接続構造上に金属層を堆積するための方法

【課題】 エレクトロマイグレーション抵抗が向上し、応力移動が軽減し、TDDBを回避する金属相互接続、特に銅相互接続を製造するための方法を提供すること。

【解決手段】 半導体ウエハのための相互接続構造上に金属層を堆積するための方法を開示する。この方法において、金属導体を誘電層によって被覆する。誘電層をパターニングして、金属導体を露出させる。次いで、パターン内にライナ層を堆積する。次いで、ライナ層をアルゴン・スパッタ・エッチングして、ライナ層を除去すると共に金属導体を露出させる。アルゴン・スパッタ・エッチングでは、ライナ層はパターンの側壁に再堆積する。最後に、パターン内に追加層を堆積して、再堆積したライナ層を覆う。  (もっと読む)

(もっと読む)

表面疎水化方法、ならびに半導体装置およびその製造方法

【課題】 その後の加工プロセスとの整合性を有し、層の表面をより簡便にかつ効率良く疎水化することができ、かつ、層のより深い領域を疎水化することができる表面疎水化方法、ならびに半導体装置およびその製造方法を提供する。

【解決手段】 本発明の表面疎水化方法は、(A)反応性シラン化合物および(B)有機溶媒を含む表面疎水化用組成物を層の表面に接触させる工程と、前記(A)反応性シラン化合物を活性化する工程と、前記層を加熱する工程と、を含む。本発明の半導体装置は、上記本発明の表面疎水化方法によって得られた疎水性膜を含む。本発明の半導体装置の製造方法は、上記本発明の表面疎水化方法によって、疎水性膜を形成する工程を含む。

(もっと読む)

半導体装置、半導体装置の製造方法、光ピックアップ装置および光通信装置

【課題】 層間絶縁層の平坦性に優れると共に、配線の導通不良が起こらず、かつ、スルーホール抵抗のばらつきが小さい半導体装置およびその半導体装置の製造方法を提供することにある。

【解決手段】 表面に高さが異なる第1および第2の部分16,17を有する下地絶縁膜4と、下地絶縁膜4に形成された下層配線11,12と、下層配線11,12および下地絶縁膜4上に順次形成された第1絶縁膜6、有機SOG膜7および第2絶縁膜8とを備える。第2絶縁膜8の上面から下層配線11,12の上面まで延びると共に、側壁が第1絶縁膜6と第2絶縁膜8とで構成された第1、第2スルーホール31,32を有する。有機SOG膜7は、下層配線11,12の夫々の上面の上方に位置する部分を有している。

(もっと読む)

半導体素子の製造方法、及びエッチング方法

【課題】デュアルダマシン多層配線構造の形成においてハードマスクの肩落ちを抑制する。

【解決手段】半導体基板100上の第1配線層102上に無機系絶縁膜104を形成し、無機系絶縁膜上に開口部を有する第1レジストパターンを形成し、無機系絶縁膜をエッチングして無機系絶縁膜にビアホール106を形成し、第1レジストパターンを除去する。無機系絶縁膜上及びビアホールの内部を覆うように有機系絶縁膜107を形成する。有機系絶縁膜上にハードマスク108を形成し、ハードマスク上に開口部を有する第2レジストパターン109を形成してハードマスクパターン108aを形成する。第2レジストパターン及びハードマスクパターンをエッチングマスクとしてビアホール内の有機系絶縁膜が除去されるまで有機系絶縁膜をエッチングしてビアホール上に配線溝110を形成し、第2レジストパターンを除去する。ビアホール及び配線溝に導電材料を充填する。

(もっと読む)

電子装置、半導体装置およびそれらの製造方法

【課題】様々な材料に適用可能であり、無電解めっき処理を用いて、より簡便にかつ安価に、選択的に形成可能な導電層を有する電子装置と半導体装置、それらの製造方法を提供する。

【解決手段】基板10に形成された易めっき性の第1絶縁膜20aと、第1絶縁膜上に形成された難めっき性の第2絶縁膜20bと、第1絶縁膜および第2絶縁膜に連通して形成された凹部20cと、凹部に埋め込まれた導電層70とを有する構成とする。基板10に絶縁膜(20a,20b)を形成し、次に絶縁膜に20c凹部を形成する。次に、凹部の内壁面の少なくとも一部を選択的に触媒化し、次に凹部に導電層70を埋め込んで形成する。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

選択的メタライゼーションを受容するための、光活性化可能なポリイミド組成物ならびにそれに関する方法および組成物

【課題】本発明は、一般に、スピネル結晶充填剤に有用な、ポリイミドベースマトリックス中に分散されているポリイミド複合体であって、0.05と0.60ミクロン-1の間およびこれらの値を含む可視−赤外線吸光係数を有する複合体を提供すること。

【解決手段】そこから形成された複合体ポリイミドは、典型的な場合、ポリイミド基板に隣接した微細な導電性経路を有する回路を作製するのに使用される。これらの微細な導電性経路は、典型的な場合、無電解金属メッキステップを使用して、基板上に形成される。まず、ポリイミド複合体の表面を、典型的な場合にはレーザ光線を使用して光活性化し、次いで光活性化した部分をメッキして、細いラインまたは経路を被膜表面に形成する。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

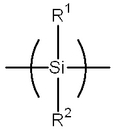

【解決手段】 本発明の表面疎水化用組成物は、(A)下記一般式(1)で表される化合物と、(B)沸点が50〜350℃である溶媒とを含む。

Si(R1)2(R2)2 ・・・・(1)

(式中、R1はアシルオキシ基、アルコキシ基またはヒドロキシ基を示し、R2はアルキル基を示す。)

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 (A)ポリシランと、(B)有機溶媒を含む、表面疎水化用組成物。(A)下記一般式(1)で表わされる化合物の群から選ばれた少なくとも1種のポリシランと、(B)有機溶媒を含む、表面疎水化用組成物、および該組成物を用いた表面疎水化方法、半導体装置。

[式中、R1,R2は水素原子、アルキル基、ビニル基、アリル基またはフェニル基を示す(ただし、R1,R2のうち水素原子は1個または0個である)。]

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 (A)ケイ素原子と炭素原子とが交互に連続してなる主鎖を有するポリカルボシラン化合物と、(B)有機溶媒とを含む表面疎水化用組成物。

(もっと読む)

電子デバイス及びその製造方法

【課題】 low−k膜のような疎水性膜を使用した多層配線構造において、層間絶縁膜に使用する疎水性膜とライナー膜又はバリア膜として使用する親水性膜との界面剥離の発生を防止する。

【解決手段】 電子デバイスは、図示しない基板上に形成された第1の層間絶縁膜11の下層配線溝11aを埋め込むように形成された下層配線12と、下層配線12の上に形成されたバリア膜13と、第1の層間絶縁膜11及びバリア膜13の上に形成された第2の層間絶縁膜14とを備えている。そして、電子デバイスは、第1の層間絶縁膜11と第2の層間絶縁膜12とが接合している界面を有している。

(もっと読む)

配線基板の製造方法

【課題】 微細配線を実現することができる「配線基板の製造方法」を提供すること。

【解決手段】 ダマシンプロセスを用いた配線形成工程を含む配線基板の製造方法において、下層配線層10上に形成された層間絶縁層11に、下層配線層11に達するビアホールVHを形成し、その際に生じたスミアSMを除去した後、層間絶縁層11上に、ビアホールVHの上方に位置する所要の配線パターンの形状に従う開口部(配線溝)OPを有するように感光性永久レジスト層12を形成する。次に、全面にシード層13を形成し、ビアホールVH及び開口部(配線溝)OPの内部を充填するようにしてシード層13上に導体層14を形成した後、感光性永久レジスト層12が露出するまで導体層14の表面を研磨して平坦化し、配線パターン15を形成する。

(もっと読む)

オルガノシロキサン

本発明は、少なくとも80重量%の式I:[Y0.01−1.0SiO1.5−2]a[Z0.01−1.0SiO1.5−2]b[H0.01−1.0SiO1.5−2]c[式中、Yはアリール、Zはアルケニル、aは式Iの15%−70%、bは式Iの2%−50%、cは式Iの20%−80%を表す]の化合物を含むオルガノシロキサンを提供する。本発明のオルガノシロキサンは、セラミックバインダー、高温カプセル化剤及び繊維マトリックス結合剤として使用し得る。本発明の組成物はまた別の材料と組合わせたときに優れた接着性を示すのでマイクロエレクトロニクス以外の用途またはマイクロエレクトロニクスの用途で接着促進剤として有用である。好ましくは本発明の組成物はマイクロエレクトロニクスの用途でエッチストップ、ハードマスク及び誘電体として使用される。 (もっと読む)

空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

【課題】半導体デバイスの形成方法および該方法によって形成されたデバイスを提供すること。

【解決手段】第1の誘電材料(12a〜f)と第2の誘電材料(14a〜f)の互層を付着させる。ここで、第1の誘電材料と第2の誘電材料は異なる速度で選択的にエッチング可能である。誘電材料の互層内に第1のフィーチャ(22、24)を形成する。誘電材料の互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の少なくとも一部分(26)を除去し、第2の誘電材料は本質的にエッチングされていないままにしておく。

(もっと読む)

多孔質絶縁膜及びその製造方法並びに多孔質絶縁膜を用いた半導体装置

半導体装置を構成する絶縁膜として有効な多孔質絶縁膜の作製方法、該絶縁膜の上下界面に接する半導体材料と高い密着性を有する多孔質絶縁膜の作製方法を提供。

少なくとも一つ以上の、分子中に環状シリカ骨格を有し且つ該環状シリカ骨格に少なくとも一つ以上の不飽和炭化水素基が結合されている有機シリカ化合物の分子蒸気、を含む気体をプラズマ中に導入し、半導体基板上に多孔質絶縁膜の成長を行う。

(もっと読む)

61 - 79 / 79

[ Back to top ]