Fターム[5F033TT03]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが有機材料 (79)

Fターム[5F033TT03]に分類される特許

21 - 40 / 79

半導体素子及びその製造方法

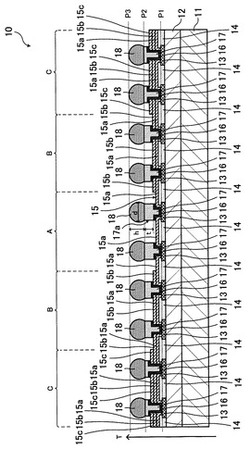

【課題】回路基板に確実に実装可能で、且つ、加熱に起因して発生する応力が抑制可能な半導体素子を提供する。

【解決手段】半導体素子10において、複数の電極パッド13の上方に、中央部Aより中間部Bで、更に中間部Bより端部Cで膜厚が厚くなるように形成した絶縁部材15を設ける。各電極パッド13に接続するアンダーバンプメタル17は、それぞれ絶縁部材15から突出させ、その先端にそれぞれバンプ18を形成する。

(もっと読む)

低誘電率絶縁体材料層の形成方法及び該方法で形成された層又はパターン

【課題】 塗布法又は印刷法により有機電子素子を形成するために用いる低誘電率絶縁材料層を低温で形成する方法、該方法で形成された層又はパターン及び有機電子素子を提供する。

【解決手段】 (a)基材上又は該電子素子を構成する導電層乃至は半導体層上に、フルオロポリマー分散体からなる第一の絶縁層形成材料を塗布又は印刷する工程、(b)フルオロポリマー分散体の乾燥皮膜を形成する工程、(c)フルオロカーボン共重合体溶液からなる第二の絶縁層形成材料を前記乾燥皮膜上に塗布又は印刷する工程、(d)フルオロカーボン共重合体溶液の乾燥皮膜を形成する工程を有する低誘電率絶縁体材料層の形成方法。

(もっと読む)

半導体装置、その半導体装置の製造方法及びパワーモジュール

【課題】絶縁層を厚くして電極間の寄生容量を低く抑えることができ、かつ、当該絶縁層に精度良く開口部を形成して作製される小型の半導体装置、その半導体装置の製造方法、及びその半導体装置を含むパワーモジュールを提供する。

【解決手段】セル160は、基板104と、基板104上に形成されるドレイン電極180、ソース電極182、及びゲート電極184と、基板104及び各電極上に形成され、ドレイン電極180の表面を露出する開口部220が形成された絶縁層142とを含む。開口部220は、ドレイン電極180の表面から絶縁層142の表面に向かってその径を広げながら所定高さまで立上がる壁面222と、基板104の表面から当該所定高さで基板104の表面に平行となった踊り場状の平坦面224と、平坦面224から絶縁層142の表面に向かってその径を広げながら立ち上がる壁面226とを有する。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】正常に動作しないチップに接続された配線に起因する問題を低減しながら、正常に動作しないチップを使用不能にする。

【解決手段】積層チップパッケージ1は、複数の階層部分11〜18を含む本体2と、本体2の側面に配置された配線3A,3Bとを備えている。複数の階層部分は、第1の種類の階層部分11〜16,18と、第2の種類の階層部分17とを含んでいる。第1の種類の階層部分と第2の種類の階層部分は、いずれも、半導体チップを含んでいる。第1の種類の階層部分は、それぞれ半導体チップに接続され、配線3A,3Bが配置された本体2の側面に配置された端面を有する複数の電極を含むが、第2の種類の階層部分は、半導体チップに接続されると共に配線3A,3Bが配置された本体2の側面に配置される端面を有する電極を含んでいない。配線3A,3Bは、複数の電極の端面に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板と、ホトダイオードの出力を半導体基板の一方の主面側から他方の主面側に導く導電性部材との間の電気絶縁性を確保することが可能な半導体装置及びその製造方法を提供すること。

【解決手段】n型半導体基板105には、隣接するp型不純物拡散領域109間に、一方の主面側から他方の主面側に貫通する貫通孔105cが形成されている。貫通孔105cは、p型不純物拡散領域109それぞれに対応して設けられている。貫通孔105cを画成するn型半導体基板105の壁面上には、熱酸化膜113が形成されている。貫通孔105c内には、熱酸化膜113の内側に導電性部材としての貫通配線115が設けられている。貫通配線115の一端側の部分は、電極配線117の一端側の部分に電気的に接続されている。電極配線117は、熱酸化膜107上に形成されており、その他端側の部分がp型不純物拡散領域109に電気的に接続されている。

(もっと読む)

半導体装置

【課題】電極の断線が生じても動作可能であり、かつ大電力で動作することが可能な、小型の半導体装置を提供する。

【解決手段】セル160は、六角形の素子形成領域を画定する開口部を形成するように形成されたソース電極182と、素子形成領域に、ソース電極182と一定距離を隔てて帯状に形成されたドレイン電極180と、ソース電極182とドレイン電極180との双方から所定の距離を隔てて形成されたゲート電極184とを含む。ゲート電極184の各辺の中央部分からソース電極182に重畳するようにゲート引出電極186を形成し、ゲート引出電極186とソース電極182との間には絶縁膜を形成する。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】ビア位置に形成されるパッドの平面寸法を小さくすることにより、上層の導電層における配線パターン形成の設計自由度を向上させることができる半導体基板の製造方法および半導体基板を提供する。

【解決手段】コア基板10に下層の配線パターン20を形成し、下層の配線パターン20を保護する第1の絶縁層30を形成し、第1の絶縁層30に第2の絶縁層であるレジスト40を積層し、レジスト40に上層の配線パターン80を形成するためのパターン溝42を形成した後、レジスト40に向けてレーザ光を照射し、レジスト40と第1の絶縁層30を厚さ方向に連通し下層の配線パターン20が底面に露出するビア穴60を形成し、ビア穴60内面、パターン溝42内面、レジスト40表面にシードメタル層70を形成した後、シードメタル層70上に電解めっきを行いめっき層72を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子と、半導体素子上の絶縁膜と、絶縁膜中に、欠陥の多い領域と欠陥の少ない領域とを有し、欠陥の多い領域は、金属元素が拡散され、絶縁膜の表面の一部と裏面の一部をつなぐ導電領域である半導体装置、及び、基板上に半導体素子を形成し、半導体素子上に絶縁膜を形成し、絶縁膜上に、半導体素子と電気的に接続された第1の導電膜を形成し、絶縁膜中にイオンを添加して、あるいはレーザビームを照射して、欠陥の多い領域を形成し、欠陥の多い領域上に、金属元素を含む導電材料を形成し、欠陥の多い領域に、金属元素を拡散させ、絶縁膜中に、第1の導電膜と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

絶縁膜形成用組成物、絶縁膜の製造方法、およびそれによって得られる絶縁膜

【課題】絶縁膜形成用組成物を提供すること。

【解決手段】絶縁膜形成用組成物は、ポリマーAと、ポリマーBと、溶媒Aおよび大気圧における沸点が溶媒Aよりも低い溶媒Bと、を含み、かつ、以下の式(i)および(ii)を満たす。

前記ポリマーAの溶媒Aへの溶解度>前記ポリマーAの前記溶媒Bへの溶解度

・・・(i)

前記ポリマーBの溶媒Aへの溶解度<前記ポリマーBの前記溶媒Bへの溶解度

・・・(ii)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

半導体デバイス及びその製造方法

【課題】半導体デバイスにおける層間絶縁膜間の密着性を良好にし、デバイスの信頼性を向上する。

【解決手段】異なる二つの絶縁膜が上下に接する構造を有する半導体デバイスにおいて、上層膜51について膜強度M1[GPa]、膜密度D1[g/cm3]、膜応力S1[GPa]、膜厚T1[nm]、下層膜52について膜強度M2[GPa]、膜密度D2[g/cm3]、膜応力S2[GPa]、膜厚T2[nm]で示されるとき、

|S2×T2/10−S1×T1/10|−(M1+M2)×(D1+D2)>280・・・・(101)

を満たし、上下層間のC/Si比が1.7以下かつO/Si比が0.8以上とする。

(もっと読む)

多孔質絶縁膜及びその形成方法並びに半導体装置の製造方法

【課題】 炭化水素含有の多孔質層間絶縁膜を用いた多層配線では、低エネルギプラズマによる放電不安定性と隣接膜との密着性劣化により、低誘電率化と高信頼化を両立することが困難であった。

【解決手段】 本発明の多孔質絶縁膜10は、有機シロキサンを原料とするプラズマCVDによって形成されたものにおいて、第一の電子エネルギのプラズマを用いてプラズマCVDによって形成された第一層11と、第一層11の上に第二の電子エネルギのプラズマを用いて前記プラズマCVDによって形成された第二層12とを備え、第一の電子エネルギが第二の電子エネルギよりも大きい、ことを特徴とする。

(もっと読む)

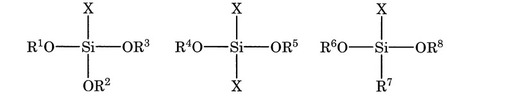

積層体およびその製造方法ならびに半導体装置

【課題】低い比誘電率を有し、かつ密着性に優れた積層体およびその製造方法、ならびに該積層体を含む半導体装置を提供する。

【解決手段】積層体は、シリカ系膜および有機系膜を含み、前記シリカ系膜と前記有機系膜とが、アルキル基、アシル基またはアリール基、と水素原子、フッ素原子、アルキル基、またはアリール基を有し2重結合を含む炭化水素基を有するアルコキシシランシラン化合物を硬化させて得られる層間膜を介して積層する。 (もっと読む)

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を低減しつつ有機膜を平坦化して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板20上に設けられ凹部を有する絶縁膜の上に、溶剤と有機成分とを含む溶液を塗布して塗膜を形成する工程と、前記塗膜を、前記有機成分の架橋が終了しない第1の温度でベークして有機膜11前駆体を得る工程と、前記有機膜前駆体を、第1の樹脂粒子および水溶性高分子を含有する第1のスラリーを用いて研磨して、表面を平坦化する工程と、前記表面が平坦化された有機膜前駆体を、前記第1の樹脂粒子より平均粒子径の小さな第2の樹脂粒子および水溶性高分子を含有する第2のスラリーを用いて研磨して前記凹部内に残置し、前記絶縁膜を露出する工程とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を低減しつつ有機膜を平坦化して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に設けられ凹部を有する絶縁膜の上に、溶剤と有機成分とを含む溶液を塗布して塗膜を形成する工程と、前記塗膜を、前記有機成分の架橋が終了しない第1の温度でベークして有機膜前駆体を得る工程と、前記有機膜前駆体を、樹脂粒子を含有するスラリーを用いて研磨して前記凹部内に残置する工程と、前記研磨に引き続いて、前記有機膜前駆体を前記第1の温度より高い第2の温度でベークして前記溶剤を除去し、前記凹部内に埋め込まれた第1の有機膜19を得る工程と、前記第1の有機膜が埋め込まれた絶縁膜の上に、塗布法により第2の有機膜20を形成して下層膜を得る工程と、前記下層膜の上に中間層22及びレジスト膜23を順次形成する工程と、前記レジスト膜をパターン露光する工程とを具備する。

(もっと読む)

平坦化構造の製造方法、及び表示装置の製造方法

【課題】平坦化構造のアッシングに対する耐性を高めつつ、レジスト層の露光精度についても可及的に高める。

【解決手段】基板11上に形成した平坦化膜15の表面に、バリア層16を積層する工程と、バリア層16の表面にレジスト層20を形成する工程と、レジスト層20を露光してレジスト層20に開口部を形成することにより、マスクを形成する工程と、マスクの開口部を介して平坦化膜15をエッチングする工程と、エッチングされた平坦化膜15からマスクをアッシングにより除去する工程とを備え、バリア層16は、下層反射防止膜により構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】アンダーフィルを用いることなく、半導体装置の高い実装信頼性を提供する。

【解決手段】能動素子10と、能動素子10に形成される電極12と、電極12に接続される導電層15と、導電層15上に形成された絶縁層16とを有し、導電層15の上部が絶縁層16から露出され、導電層15が露出される部分において、導電層15と絶縁層16とに段差が設けられる半導体装置を構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続孔内から無電解めっき層が剥がれて抜け落ちるのを防止できる半導体装置及びその作製方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体層32上に形成された第1の絶縁層33,203と、前記第1の絶縁層に形成され、前記第1の絶縁層の上面から途中まで異方性エッチングにより形成された第1の接続孔203cと、前記第1の絶縁層に形成され、前記第1の接続孔に繋げられ、前記第1の接続孔下の前記第1の絶縁層が等方性エッチングにより形成され、前記半導体層上に位置する第2の接続孔203gと、前記第1の接続孔内の側面及び前記第1の絶縁層上に形成された第2の絶縁層203dと、前記第2の接続孔の底面の前記半導体層から成長され、前記第2の接続孔内及び前記第1の接続孔内に埋め込まれた無電解めっき層204aと、を具備することを特徴とする。

(もっと読む)

電子素子および電子素子の製造方法

電子素子、特にTFT、蓄積コンデンサまたはスタック装置の導電層間の交差部等を備えるものが開示されている。電子素子は、電極を形成する第1の導電層を基板上に備える。第2の導電層により形成された第2の電極は第1の電極から少なくとも誘電体層により隔てられている。この誘電体層は電気絶縁材料の中間層、好ましくは絶縁破壊に対して高い耐性を有する中間層と、光パターニング可能な電気絶縁材料のさらなる層とを包含する。 (もっと読む)

21 - 40 / 79

[ Back to top ]