Fターム[5F033VV15]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | TFT用 (1,331)

Fターム[5F033VV15]に分類される特許

141 - 160 / 1,331

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

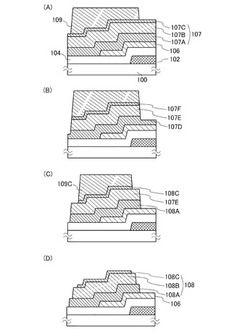

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下を抑制する半導体装置及びその製造方法を提供する。

【解決手段】実施の形態の半導体装置1は、配線20を有する配線層11bと、配線層11b上に形成された層間絶縁膜26と、層間絶縁膜26上に形成され、上部がシリサイド化されたアモルファスシリコン層27を有するTFT14と、TFT14上に、層間絶縁膜47を介して形成された配線50を有する配線層12aと、層間絶縁膜47、アモルファスシリコン層27及び層間絶縁膜26を貫通し、第1及び第2の配線を電気的に接続するコンタクトプラグ32と、を備える。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

表示装置およびその製造方法

【課題】内部短絡を防ぐ表示装置を提供する。また、内部短絡を防ぐ前記表示装置の製造方法を提供する。

【解決手段】本発明の実施形態に係る表示装置は、基板111と、前記基板上に形成された半導体層133と、前記半導体層上に形成された有機絶縁膜170と、前記有機絶縁膜上に形成された複数の導電配線184,185,187,188,189と、前記複数の導電配線の間で前記有機絶縁膜に形成されたオープングルーブ7080とを含む。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】高い電荷移動度を有し、大面積表示装置に対して均一な電気的特性を得ることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板上に形成されたゲート電極と、前記ゲート電極上に形成されたSiNxから構成された第1ゲート絶縁膜と、前記第1ゲート絶縁膜の上に形成されたSiOxから構成された第2ゲート絶縁膜と、前記ゲート電極と重畳するように形成され、チャネル部を有する酸化物半導体層と、前記酸化物半導体層及び前記ゲート電極の上部に形成されたSiOxから構成された保護膜とを含み、前記保護膜はドレイン電極拡張部を露出するコンタクトホールを含む。ここで、前記コンタクトホールは、ドレイン電極拡張部を直接的に露出する部分の保護膜が、その上部の保護膜よりさらに狭い領域を占める形状を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグを、配線のバリア層に安定して接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、バリア層を介して配線に接続されたコンタクトプラグ、第1及び第2の絶縁膜を有する。第1の絶縁膜は、配線及びバリア層の側面を覆い少なくともバリア層よりも上方で配線が延在する方向と直交する方向の幅が狭まる傾斜面を有し、バリア層の上面の一部を露出すると共に配線及びバリア層の側面を露出させないように形成された開口部を備える。第2の絶縁膜は、開口部の内側を除き第1の絶縁膜上に形成され、かつ開口部を備える。

(もっと読む)

141 - 160 / 1,331

[ Back to top ]