Fターム[5F038AR28]の内容

Fターム[5F038AR28]に分類される特許

1 - 20 / 51

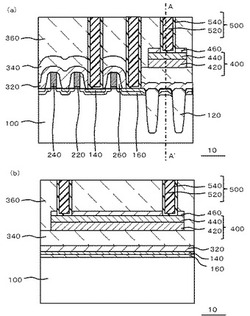

半導体装置及び半導体装置の製造方法

【課題】多層配線中に、抵抗率が高く、かつ抵抗温度係数が小さい抵抗素子を備える半導体装置を提供する。

【解決手段】第1絶縁層(層間絶縁層340)と、第1絶縁層(層間絶縁層340)上に設けられ、少なくとも表層がTaSiN層440である抵抗素子400と、第1絶縁層(層間絶縁層340)および抵抗素子400上に設けられた層間絶縁層360と、層間絶縁層360に設けられ、一端がTaSiN層440と接続する複数のビア500と、を備えている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における抵抗の比精度の改善にある。

【解決手段】第1抵抗R1の第1抵抗体10は、長さL、幅Wを有する。第1コンタクト12aは、第1抵抗体10の一端に形成され、第2コンタクト12bは、第1抵抗体10の他端に形成される。第2抵抗R2の第2抵抗体10は、長さL/2、幅Wを有する。第2抵抗体10の一端には、N個の第1コンタクト12aが形成され、第2抵抗体10の他端には、N個の第2コンタクト12bが形成される。

(もっと読む)

半導体装置

【課題】次段回路で基準電圧として用いられる定電圧を生成する基準電圧回路について、ツェナーダイオードの製造ばらつき等が出力定電圧の温度特性に及ぼす影響を低減する。また、当該出力定電圧の温度特性の平坦性を向上する。また、回路規模の増大を抑制しつつ優れた起動性、応答性および安定性を実現する。

【解決手段】分圧回路332は直列接続されたダイオード304,306,308に対して並列的に設けられている。分圧回路332の低電位側接続点yの電圧は正の温度特性を示し、分圧回路332の高電位側接続点xの電圧は負の温度特性を示す。分圧点zにおける定電圧V0が平坦な温度特性を持つように分圧抵抗316,318の抵抗値が設定されている。分圧回路332の分圧点zは、フィードバックループに接続されることなく次段回路へ接続されることにより、次段回路へ定電圧V0を出力する。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置の製造方法

【課題】温度係数の小さいポリシリコン抵抗体を含む半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にノンドープポリシリコン膜4を形成する工程と、ノンドープポリシリコン膜4をパターニングしてノンドープポリシリコンパターン40を形成する工程と、ノンドープポリシリコンパターン40を窒素雰囲気中でアニールし、ノンドープポリシリコンパターン40のシリコン結晶粒径を拡大する第1アニール工程と、第1アニール工程においてシリコン結晶粒径が拡大されたノンドープポリシリコンパターン40に導電型がP型のBF2+イオンを注入する工程と、BF2+イオンが注入されたポリシリコン抵抗体8を酸素雰囲気中でアニールする第2アニール工程によって半導体装置を形成し、第1アニール工程は、不純物を注入する前で、ポリシリコン膜形成の後に行われ、処理時間が不純物の量に対応する。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

高音質抵抗膜及びその製造方法

【課題】オーディオ信号処理回路に最適なTaN膜とTa膜との積層膜を使用して、TCR値が小さく、シート抵抗が大きく、実用上必要な膜厚を確保できる高抵抗の高音質抵抗膜及びその製造方法を提供する。

【解決手段】高音質抵抗膜は、窒化タンタル膜2aとタンタル膜2bとの積層膜2からなり、この積層膜全体として、抵抗値温度係数TCRが−50乃至+50ppm/℃であると共に、シート抵抗が100Ω/□以上であり、前記窒化タンタル膜は、半導体装置の製造工程で常温から400℃までの温度で、窒素分圧比を3乃至15%として、2.5kW以下の低パワーで、スパッタリングにより成膜されたものである。前記TaN膜のスパッタリング時の基板温度をTとし、窒素ガス分圧比をmとしたとき、前記基板温度T及び窒素ガス分圧比mは、(2/165)T+(91/33)≦m≦(1/66)T+(155/33)を満たすことが好ましい。

(もっと読む)

薄膜抵抗体を備えた半導体装置の製造方法

【課題】TCR値が小さく、実用上必要な膜厚を確保できるTaN膜からなる薄膜抵抗体を、その配線形成時のTaN膜の損傷を防止して形成できる半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板上に第1層間絶縁膜を形成し、基板温度を常温から400℃までの温度に設定し、反応ガス中の窒素ガス分圧比を3乃至10%として、第1スパッタリングにより、前記第1層間絶縁膜上に窒化タンタル膜を形成する。その後、第1層間絶縁膜上に形成した第2層間絶縁膜に窒化タンタル膜に至るビアホールを湿式エッチングにより形成し、第2スパッタリングにより金属膜を堆積して前記ビアホール内に金属膜を形成し、前記窒化タンタル膜に接続するビアを設ける。

(もっと読む)

集積回路

【課題】従来のものに比べて音質を向上させた、アナログ音声信号処理用の回路を内蔵する集積回路を提供する。

【解決手段】集積回路10において、入力端子12,14から入力されたアナログ音声信号は、抵抗素子R1,R2で構成される抵抗回路網20で分圧されてオペアンプ22の非反転入力端に入力される。オペアンプ22の出力信号は抵抗素子R3,R4で構成される抵抗回路網24で分圧されてオペアンプ22の反転入力端に帰還される。抵抗素子R3,R4の両端の信号が出力端子16,18から出力される。抵抗回路網20,24を構成する抵抗素子R1〜R4はそれぞれ窒化タンタル層30とタンタル層28の二層積層構造で構成されている。

(もっと読む)

抵抗アレイ及びそれを用いた集積回路

【課題】微細化した抵抗アレイ及びそれを用いた集積回路において、局所的な温度分布の影響を軽減して相対精度を向上する。

【解決手段】抵抗アレイは、素子分離膜102を有する半導体基板101上に形成された複数の抵抗素子103を含む。それぞれの抵抗素子103は、少なくともシリコンを含む多結晶体からなる抵抗部と、シリサイド層を含むコンタクト部104とを備える。それぞれの抵抗素子103の少なくとも一部が、素子分離膜102よりも膜厚の薄い絶縁膜301を介して半導体基板101上に配置されている。

(もっと読む)

抵抗器の温度係数を調整する回路

【課題】集積回路の一部となりうる温度補償抵抗(TCR)回路を提供する。

【解決手段】TCR回路100は、2つの抵抗器110、120およびダイオード130からなる。2つの抵抗器は並列に接続され、またダイオードは、これらの抵抗器のうちの1つと直列に接続される。TCR回路の2つの並列な脚部は、接地などの基準電圧源に接続することができる。バイポーラトランジスタ、ツェナーダイオードもしくはショットキーダイオード、または特別に処理された抵抗器などの特化されたデバイスは、TCR回路では必要とされない。TCR回路の抵抗器およびダイオードは、抵抗器の抵抗値の温度変化を調整するように選択することができ、それにより、回路に対する抵抗の温度係数を負、ゼロ、または正にする。位相ロックループ(PLL)回路については、TCR回路の応用例として記載される。

(もっと読む)

半導体装置及びその製造方法

【課題】適切な抵抗素子を得ることが可能な半導体装置を提供する。

【解決手段】素子領域11及び素子分離領域12を含む基板10と、素子領域上に形成されたゲート絶縁膜21と、ゲート絶縁膜上に形成された金属膜22及び金属膜上に形成された第1の半導体膜23を有するゲート電極とを含むトランジスタ部と、基板の上方に形成され且つ第1の半導体膜と同一の材料で形成された第2の半導体膜23と、基板と第2の半導体膜との間に形成された空洞25とを含む抵抗素子部とを備える。

(もっと読む)

MOSトランジスタ抵抗器、フィルタおよび集積回路

【課題】製造上のばらつきによるリーク電流の変化に起因する抵抗値の変動が低減され、かつ温度特性の良好なMOSトランジスタ抵抗器を提供する。

【解決手段】抵抗器として使用される第1MOSトランジスタM1と、第1MOSトランジスタのソースに接続され、入力電圧Vinを印加する入力電圧源1と、第1MOSトランジスタのゲートに接続され、ゲート電圧Vgを印加するゲート電圧源6とを備えたMOSトランジスタ抵抗器。ゲート電圧Vg及び入力電圧Vinは、第1MOSトランジスタのゲート−ソース間電圧及びソース−ドレイン間電圧が、第1MOSトランジスタを非飽和領域で動作させる範囲で印加されるとともに、第1MOSトランジスタの抵抗値における温度特性の温度特性が一定になる条件を満たす関係に設定される。

(もっと読む)

半導体集積回路装置

【課題】高精度で低電圧までの動作が可能な基準電圧発生回路を提供する。

【解決手段】デプレッション型第1MOS及びエンハンスメント型第2MOSにより差動回路部が構成され、上記第1と第2MOSの共通化されたソースと回路の接地電位との間に定電流源が設けられ、それぞれのドレインと動作電圧との間に負荷回路が設けられる。上記差動回路部の出力信号がゲートに供給され、出力電圧を上記第2MOSのゲートに負帰還させるソースフォロワ形態の第3MOSのソースと上記接地電位との間に第1抵抗、第2抵抗及びダイオード形態の第4MOSからなる直列回路が設けられる。上記第1MOSのゲートは、上記接地電位が供給され、上記直列回路は、上記出力電圧の持つ温度依存性を補償するよう上記第1抵抗と第2抵抗の抵抗比及び上記第4MOSとの接続構成と、温度補償された定電圧を得る出力点が選ばれる。

(もっと読む)

半導体装置及びその製造方法

【課題】温度係数とそのシート抵抗値とを独立に調整することができる抵抗素子を提供する。

【解決手段】半導体基板1上に第1の多結晶半導体膜3を形成し、その上層にアモルファス半導体膜4を形成する。アモルファス半導体膜4の中にキャリア不純物をイオン注入し、その後に熱処理を行うことにより、アモルファス半導体膜4を多結晶化して、第2の多結晶半導体膜5を形成する。これにより、第2の多結晶半導体膜5の平均的なグレインサイズは、第1の多結晶半導体膜3の平均的なグレインサイズよりも大きくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】温度係数とそのシート抵抗値とを独立に調整することができる抵抗素子を提供する。

【解決手段】半導体基板1上に第1の多結晶半導体膜3を形成し、その表面から膜厚の途中までの領域に不活性元素をイオン注入することにより、該領域をアモルファス半導体膜3Aに変化させる。次に、アモルファス半導体膜3Aの中にキャリア不純物をイオン注入し、その後に熱処理を行うことにより、アモルファス半導体膜3Aを多結晶化することにより、第2の多結晶半導体膜4を形成する。これにより、第2の多結晶半導体膜4の平均的なグレインサイズは、第1の多結晶半導体膜3の平均的なグレインサイズよりも大きくなる。

(もっと読む)

半導体装置の製造方法

【課題】同一の半導体基板に、温度係数が低くて抵抗値の制御が容易な抵抗素子と、単位面積当たりの容量値が大きくて占有面積を縮小でき、かつ電圧依存性の小さい容量素子と、MOS型半導体素子とを高信頼性に製造でき、かつ製造工程の短縮を計ることができる半導体装置の製造方法を提供すること。

【解決手段】ゲート電極を含むnウエルと抵抗素子とに第二p型不純物を導入してpチャネル型MOSFETの形成と抵抗素子の抵抗値の調整とをそれぞれ行う工程と、第一p型不純物を含有する容量素子の上層電極に第三n型不純物を導入してn型に変換する工程を有する半導体装置の製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】抵抗体素子の特性のバラつきを低減できるようにした半導体装置の製造方法を提供する。

【解決手段】MOSトランジスタ10と薄膜抵抗素子30とを同一のシリコン基板1上に有する半導体装置の製造方法であって、最上層電極27を形成した後で、層間絶縁膜40上に薄膜抵抗素子30を形成する工程と、この薄膜抵抗素子30にレーザーアニール処理を施してその特性を改質する工程と、を含む。このような方法によれば、ファーネス又はホットプレートを用いたバッチ式のアニール処理と比べて、ロット内のウエーハ間や、ウエーハ面内の各位置におけるアニール温度のバラつきを低減することができる。また、シリコン基板1全体を加熱するのではなく、薄膜抵抗素子30のみを所望の温度まで加熱することができるので、レーザーアニールの処理温度を高温度に設定することができる。

(もっと読む)

1 - 20 / 51

[ Back to top ]