Fターム[5F038BB08]の内容

Fターム[5F038BB08]に分類される特許

1 - 20 / 294

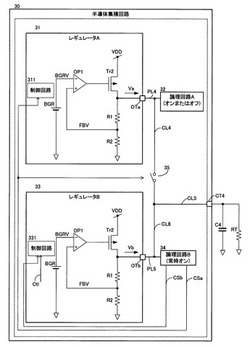

半導体集積回路

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

半導体装置

【課題】適切に電源電圧を負荷回路に供給することができる、半導体装置を提供する。

【解決手段】電圧トランスファ20及びセンスノード配線33が設けられており、電圧トランスファ20は、各Sub−Arrayに応じて設けられたNMOSトランジスタTRにより、ノード32とノード30との間が接続される。電圧トランスファ20のトランジスタTRは、ソース及びドレインの一方が電源線31の各Sub−Arrayに応じた位置に接続されており、ソース及びドレインの他方がセンスノード配線33に接続されている。また、トランジスタTRのゲートには、対応するSub−Arrayのデコード信号A0〜AXが入力される。

(もっと読む)

半導体集積回路

【課題】クランプ電圧を正確な値に設定できる半導体集積回路を提供することを目的とする。

【解決手段】第1の電圧である電源を供給されて定電流を発生する定電流部60と、定電流部60で発生された定電流を供給されて第1の電圧より低い第2の電圧を発生し、第1の電圧の電源を第2の電圧にクランプするクランプ部71と、クランプ部71でクランプされた電源を供給されて基準電圧を発生する基準電圧発生部72とを有し、クランプ部71は、ゲートとドレインに接続され縦型接続された複数段のMOSトランジスタM11−1〜M11−nである。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

メモリ電圧制御装置およびメモリ電圧制御方法

【課題】メモリを低電圧で制御して省電力制御を図ることおよびエラーの発生を防止することを改善できるメモリ電圧制御装置およびメモリ電圧制御方法を提供する。

【解決手段】メモリ電圧制御装置10およびメモリ電圧制御方法は、デバイス13,14と、デバイス13,14の異常を検出する電気機器11と、を備え、電気機器11は、デバイス13,14の異常を検出した時に、デバイス13,14に対して動的または静的に駆動電圧を昇圧する制御を行う。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

電圧検出回路

【課題】出力目標値の設定に別途の基準電圧源を必要とせず、かつ、出力電圧範囲の拡大と回路規模の縮小を実現することのできるレギュレータ回路を提供する

【解決手段】電圧検出回路300は、監視対象電圧Voutを分圧して第1電圧V31と第2電圧V32を生成する分圧回路(303、307〜311)と、エミッタ面積の異なるトランジスタ対(305及び306)に入力される第1電圧V31と第2電圧V32を比較して電圧検出信号S2を生成する比較回路(301、302、304〜306、312、313)と、を有する。

(もっと読む)

保護回路

【課題】低圧回路10を保護しつつ、かつ、低圧回路10の動作を継続させる保護回路100を提供する。

【解決手段】PチャネルMOSトランジスタMP1は入力電源Vinと低圧回路10との間に設けられている。第1ツェナーダイオードZ1のカソードは、入力電源VinとPチャネルMOSトランジスタMP1のソースとの間に接続されている。第1ツェナーダイオードZ1のアノードは、分岐ノードN1で分岐され、一方は抵抗R1を介して接地されている。分岐ノードN1で分岐された他方は、PチャネルMOSトランジスタMP1のゲートに接続されている。第2ツェナーダイオードZ2のカソードは、低圧回路10とチャネルMOSトランジスタMP1のドレインとの間に接続されている。第2ツェナーダイオードZ2のアノードは、接地されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

半導体集積回路

【課題】レイアウト面積が増大を抑制しつつ、高電位入力から低電位出力を生成するトランジスタのESD耐性を向上させる。

【解決手段】電源配線112、113間にはPチャンネル電界効果トランジスタ131が接続され、電源配線113とPチャンネル電界効果トランジスタ131のゲートとの間にはPチャンネル電界効果トランジスタ132が接続され、異常電圧検出回路142は、第1の電圧V1と第3の電圧V3との電位差に基づいてPチャンネル電界効果トランジスタ132をオン/オフ制御する。

(もっと読む)

半導体装置

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

半導体装置

【課題】電圧生成回路を備えた半導体装置において、電圧生成回路の電荷供給能力が十分でない場合であってもチャージシェアを引き起こすことなく、電圧生成回路の出力電圧を従来よりも高精度に検出できるようにする。

【解決手段】半導体装置1は、電圧生成回路11と、第1のスイッチSW2と、充電回路20とを備える。電圧生成回路11は、電圧を生成して出力し、生成する電圧の大きさを調整する機能を有する。第1のスイッチSW2は、オン状態のときに互いに導通する第1および第2の導通端子を有し、第1の導通端子が電圧生成回路11の出力ノードと配線を介して接続される。充電回路20は、第1のスイッチSW2の第2の導通端子に接続された配線を充電する。

(もっと読む)

1 - 20 / 294

[ Back to top ]