Fターム[5F038BE01]の内容

Fターム[5F038BE01]の下位に属するFターム

Fターム[5F038BE01]に分類される特許

1 - 20 / 114

半導体装置

【課題】液晶等の電気光学素子若しくは発光素子等を表示媒体として用いる表示装置及びその駆動方法を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制する。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体集積回路及び制御方法

【課題】LSIの機能増加に伴い外部端子数が増加傾向にある。更に、回路の微細化が進み、パッケージサイズも小型化が進んでいる。このため、LSIの外部端子数の削減が求められている。

【解決手段】本発明は、複数の外部記憶デバイスから1つを選択して、実行プログラムをロードする半導体集積回路であって、複数の内蔵ヒューズ回路を備えるヒューズ部と、前記内蔵ヒューズ回路が示す値に応じて選択した外部記憶デバイスからの実行プログラムをロードする処理部と、を有する半導体集積回路である。

(もっと読む)

半導体集積回路

【課題】低消費電力で動作し、かつ、端子数を減らすことが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の回路と、第2の回路と、信号伝播制御回路と、を備える。第2の回路は、前記第1の回路の電源端子とは独立の電源端子を有する。信号伝播制御回路は、前記第2の回路に電源が投入されてから所定期間、所定の固定値を前記第2の回路へ入力し、前記所定期間経過後、前記第1の回路からの出力信号および前記所定の固定値のいずれを前記第2の回路へ入力するかを制御する。

(もっと読む)

半導体装置の製造方法

【課題】テスト時間の増加を防止しながら、低コストで、効率よく品種展開された半導体装置のテストを行う。

【解決手段】計算機3から、テストプログラム、テストパターン、および半導体装置のROMに書き込まれるROMファイルが、テスタ4に送信される。テスタは、品種固有テストであるRAM機能テスト、電源リーク測定、およびROMファイルを書き込むROM書き込みのそれぞれのテストの前に、ROMファイルに含まれるROMファイル番号が、’XXX’か、’YYY’かを判定し、テスト中の半導体装置が品種Aか、品種Bかを判定する。これら品種固有テストでは、品種の判定結果に基づいて、判定された品種に見合った規格値によるテスト判定が行われる。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

テスト回路およびテスト回路の制御方法

【課題】テスト専用端子の増加を防ぎ、テストの長時間化を防止する。

【解決手段】テストアクセスポートに入力されるテスト信号に応じて、回路ブロックの試験を行うテスト回路であって、第1のTAP制御部及びその制御下にある第2のTAP制御部と、第1のTAP制御部のテスト動作の無効と、記憶情報の書き換えを不可に制御する第1の情報を記憶する第1のレジスタと、第1の情報に応じて記憶情報の書き換えを不可に制御され、第2のTAP制御部のテスト動作の有効・無効の制御する第2の情報を記憶する第2のレジスタと、外部から入力されるTDI信号に応じて前記第1、2のレジスタが書き換え不可状態を解除する制御回路と、を有するテスト回路。

(もっと読む)

スキャンテスト装置及びスキャンテスト方法

【課題】回路規模が増大することなく、テストデータを入力する入力端子の個数を削減できるスキャンテスト装置及びスキャンテスト方法を提供すること。

【解決手段】本発明にかかるスキャンテスト装置1は、テストデータ入力端子、OR素子17、スキャンフリップフロップ12を備える。テストデータ入力端子には、第1のスキャンチェーンに対する第1のテストデータと第2のスキャンチェーンに対する第2のテストデータとを少なくとも含むテストデータが入力される。OR素子17は、テストデータが入力され、クロック信号とは非同期であるマスク信号に基づいて、第2のテストデータをマスクして、第1のテストデータを出力する。スキャンフリップフロップ12は、前記第1のスキャンチェーンの先頭に配置され、OR素子17が出力した第1のテストデータに対応する非同期テストデータを保持する。

(もっと読む)

スキャンモード信号生成回路および半導体集積回路

【課題】半導体集積回路の端子数の増加を抑制することができるスキャンモード信号生成回路および半導体集積回路の提供を図る。

【解決手段】スキャンモード制御信号SMCを受け取るスキャンモードフリップフロップ41と、該スキャンモードフリップフロップの出力信号を遅延してタイミング調整を行うタイミング調整用回路42と、前記スキャンモード制御信号および前記タイミング調整回路の出力信号を受け取ってスキャンモード信号SMを生成するスキャンモード用論理回路43と、を有するように構成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の検査方法

【課題】レギュレータ回路の検査用端子と他の機能端子との兼用を可能とする。

【解決手段】負荷電流印加回路は、スイッチ経路選択信号に基づいて負荷電流印加端子から負荷回路に検査用負荷電流を印加する。レギュレータ回路駆動用回路は、複数のスイッチ回路を備え、ゲート制御信号に基づいて負荷回路に供給する電流量を制御する。差動増幅器は、レギュレータ回路駆動用回路から出力される負荷電源電圧と、基準電圧とを比較する。ゲート制御信号選択回路は、差動増幅器の出力に基づいて、負荷電源電圧が所定の電圧になるようにゲート制御信号を生成してレギュレータ回路駆動用回路に出力する。検査するとき、ゲート制御信号選択回路は、複数のスイッチ回路のうちの所定のスイッチ回路を差動増幅器の出力に基づいて動作させ、他のスイッチ回路をオフ状態にするゲート制御信号を出力する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の性能を下げることなく、コスト低減及び小型化を図ることができる半導体集積回路装置を提供する。

【解決手段】内部回路と、外部から入力された入力信号を内部回路に供給及び内部回路から供給された出力信号を外部に出力する入出力回路と、を有する半導体集積回路装置であって、内部回路に駆動電圧を供給するための内部回路用電源端子と、入出力回路に駆動電圧を供給するための入出力回路用電源端子と、内部回路及び入出力回路に共通のグランド電圧を供給するための共通グランド端子と、を有し、内部回路用電源端子、入出力回路用電源端子、及び共通グランド端子が隣り合って配置されることによって当該3つの端子から単位端子群が形成されていること。

(もっと読む)

クロック制御回路、その制御方法、半導体装置及びそのクロック生成方法

【課題】外部端子を用いず設定値を設定することができるクロック制御回路及びクロック制御回路の制御方法を提供する。

【解決手段】クロック制御回路は、スキャンテスト対象回路のスキャンクロックを生成するクロック制御ブロック11と、クロック制御ブロック11に設定値を設定するブロック設定保存回路13と、クロック制御ブロック11とブロック設定保存回路13との間に配置され、ブロック設定保存回路13の設定値を受け取り、スキャンテスト時にクロック制御ブロック11に当該設定値を設定するスキャン用設定保存回路12とを有する。

(もっと読む)

テスト回路

【課題】レイアウトが複雑になることを抑える。

【解決手段】テスト対象とされる複数の出力バッファ11のそれぞれに対応してサブテスト回路1aを備える。それぞれのサブテスト回路1aは、前段のサブテスト回路1aの出力が後段のサブテスト回路1aの入力に接続されてチェーン構成をなし、初段のサブテスト回路1aの入力には信号TDIを入力し、最終段のサブテスト回路1aの出力から信号TDOを出力する。サブテスト回路1aは、対応する出力バッファ11の出力値と入力における入力値とが異なる場合に、出力に信号TDIの論理値とは異なる論理値を出力する。

(もっと読む)

半導体集積回路装置

【課題】テスト出力端子数を増大させることなく、テストの信頼性を向上させる。

【解決手段】同一の機能を有し、スキャン入力信号10を入力可能とするIP回路111〜113と、IP回路111〜113のそれぞれに対し、スキャンクロック信号20を選択的に供給する選択回路100と、IP回路111〜113のそれぞれから出力されるスキャンテスト結果信号を通過させるか遮断するかを決定するマスク回路120と、マスク回路120から出力されるそれぞれの出力信号の論理積を求めるAND回路140と、マスク回路120から出力されるそれぞれの出力信号の論理和を求めるOR回路150と、AND回路140の出力に接続される第1のテスト出力端子と、OR回路150の出力に接続される第2のテスト出力端子と、を備える。

(もっと読む)

半導体集積回路および半導体集積回路の試験方法。

【課題】半導体集積回路の外部端子の試験において、より少ない端子で、LSIチップのテストを実現させる。

【解決手段】本発明に係る半導体集積回路のテスト方法は、内部回路と、内部回路と接続される複数の外部端子と、内部回路と複数の外部端子との間に設けられ、複数の外部端子をテストするためのテスト回路とを有する半導体集積回路のテスト方法であって、外部端子に複数の外部出力端子を含む場合に、複数の外部端子を、テスタに接続された1本の共通配線に接続し、テスト回路により、テスタからの制御信号をデコードして選択信号を生成し、当該選択信号により複数の外部出力端子のいずれか1つを選択し、テスタからテスト信号を入力し、選択された一の外部出力端子から当該テスト信号を共通配線に出力し、共通配線を介して出力されるテスト信号を、テスタにて観測することで外部出力端子の導通をテストする半導体集積回路のテスト方法。

(もっと読む)

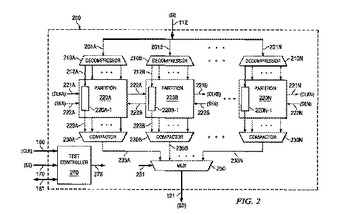

パーティションを設けたスキャン・チェーンを備えた集積回路のスキャンテストにおける向上した制御

パーティションを設けたスキャン・チェーンを備えた集積回路(IC)に実装されたテスト・コントローラが、スキャンテストを実行する際に向上した制御を提供する。一つの側面に従って、テスト・コントローラは、独立しているべき、ICの異なるスキャン・チェーンに対するスキャンテストのスキャンイン、スキャンアウト、及びキャプチャ位相を選択的に制御できる。外部テスターとインタフェースするためにテスト・コントローラに必要なピンの数は、そのテスト・コントローラがサポートし得るパーティションの数より少ない。別の側面に従って、ICは、遷移故障(又はLOS)テストをサポートするため各パーティションに対応するレジスタを含む。別の側面に従って、パーティションを設けたスキャン・チェーンを備えたICが、シリアル−パラレル及びパラレル−シリアル変換器を含み、それにより、スキャンテストをサポートするために必要とされる外部ピンを最小限にする。  (もっと読む)

(もっと読む)

半導体装置

【課題】温度検出素子の温度検出素子の静電破壊に対する耐性の向上と、測定精度の向上させることができる半導体装置を提供すること

【解決手段】半導体装置100は、温度検出素子10と、一方の端子が温度検出素子10の電流入力端子に接続される抵抗器11とをそれぞれが備え、互いに並列に接続される複数の温度検出素子列12とを備える。また、複数の温度検出素子列12の抵抗器11の他方の端子が接続される第1の外部端子14を備える。

(もっと読む)

半導体集積回路装置、及び半導体集積回路装置のテスト方法

【課題】測定パターンに含まれる電極数を低減することのできる、半導体集積回路装置、及びそのテスト方法を提供する。

【解決手段】複数の第1チェーンと、複数の第2チェーンと、前記複数の第1チェーンの各々の一端に接続される、第1共通電極と、前記複数の第2チェーンの各々の一端に接続される、第2共通電極と、複数の選択電極とを具備する。前記複数の選択電極の各々は、前記複数の第1チェーンのうちのいずれかの他端と、前記複数の第2チェーンのうちの何れかの他端とに接続される。テスト対象チェーンが前記複数の第1チェーンの中から選ばれた場合に、前記第1共通電極には、第1基準電圧が印加され、前記第2共通電極には、第2基準電圧が印加され、前記複数の選択電極のうちで前記テスト対象チェーンに接続された対象選択電極には、前記第2基準電圧が印加され、前記対象選択電極を流れる電流値を測定することにより、前記テスト対象チェーンの抵抗値が求められる。

(もっと読む)

1 - 20 / 114

[ Back to top ]