Fターム[5F038BE04]の内容

Fターム[5F038BE04]の下位に属するFターム

テスト用との切換 (119)

Fターム[5F038BE04]に分類される特許

1 - 20 / 66

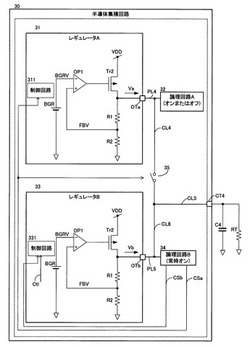

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

半導体装置

【課題】パッケージのピン数が変更された場合でも設計変更を必要としない半導体装置を提供する。

【解決手段】半導体装置に設けられた第1の選択部50は、機能ブロック群23と複数のパッド33との間の信号の経路に設けられ、各パッドごとに、標準設定として割当てられた複数の信号うち1つの信号を選択する。レジスタ61は、少なくとも第1または第2のデータを保持する。第2の選択部51は、第1の選択部50と複数のパッド33との間の信号の経路に設けられる。第2の選択部51は、レジスタ61に第1のデータが保持されたときに、第1の選択部50によって選択された各信号を標準設定のパッドを介して外部との間で入出力可能にし、レジスタ61に第2のデータが保持されたとき、第1の選択部によって選択された複数の信号のうち少なくとも一部の信号を標準設定と異なるパッドを介して外部との間で入出力可能にする。

(もっと読む)

電圧レギュレータを有する集積回路装置

【課題】集積回路装置のモード端子の数を低減する。

【解決手段】第1の電源端子VCCに接続され第1の電源電圧VDDEを供給する第1の電源配線11と,第1の電源電圧VDDEから第2の電源電圧VDDIを生成し第2の電源配線13に出力する電圧レギュレータ12と,電圧レギュレータの出力に接続され外部キャパシタが接続されるキャパシタ端子Cと,キャパシタ端子に印加される電圧に従い第1の状態と第2の状態とを判定する判定回路21とを有する。この判定回路は、キャパシタ端子Cに第3の電源電圧が印加されないで電圧レギュレータが動作する第1の動作モードと,キャパシタ端子Cに第3の電源電圧が印加されると共に電圧レギュレータが停止する第2の動作モードとを切り換えるので、モード端子数を削減することができる。

(もっと読む)

アナログ電圧調整回路、及びアナログ電圧調整方法

【課題】検査工程と調整工程をほぼ同時に実行可能な、アナログ電圧調整回路を提供する。

【解決手段】アナログ電圧調整回路1は、外部装置から、目標電圧を示す目標電圧信号を入力する、目標電圧入力端子12と、目標電圧信号に基づいて生成された目標電圧を示すデータを取り込み、期待値データとして格納する、期待値データ格納回路7と、トリミングデータを格納し、トリミングデータに応じたトリミング信号を出力する、トリミングデータ格納回路11と、トリミング信号を取得し、トリミングデータに応じた電圧レベルで、アナログ出力信号を出力する、アナログ信号出力回路2と、アナログ出力信号の電圧レベルを示す測定データと、格納された前記期待値データとを比較し、比較結果を示す比較結果信号を生成する比較回路8と、比較結果信号に基いて、トリミングデータを変更するか否かを決定する、制御回路10とを具備する。

(もっと読む)

高電圧集積回路用のモード選択のための方法と装置

【課題】追加の高電圧回路の不便なしに高電圧集積回路の端子に機能性を追加する方法を開示する。

【解決手段】特典は追加の端子の犠牲なしに集積回路の試験、トリミング・パラメータ、または他の目的で代替動作モードを選択することができることである。一実施形態において、普通の低電圧回路が、通常高電圧に曝される端子の電圧をモニタリングする。簡単な電圧検出器と通常のラッチの構成により、集積回路が意図された用途にないときには試験とトリミング・モードに容易に入ることができるが、集積回路が意図された用途で動作しているときには試験とトリミング・モードに入ることが禁止される。

(もっと読む)

LSI,鉄道用フェールセーフLSI,電子装置,鉄道用電子装置

【課題】従来のフェールセーフLSIは、チップ内のプロセッサや比較回路の配置について言及されていたが、パッケージの信号ピン配置までは言及されていなかった。また、多様な周辺回路や高速な外部メモリへの対応も考慮されていなかった。

【解決手段】2つのプロセッサからの出力を照合して一本化された内部インタフェースを共通系内部バスに接続し、その共通系内部バスに複数の外部インタフェース回路を接続する。また、2つの系統に関する信号ピンをパッケージの対角に配置するともに、それらの間に共通系に関する信号ピンを配置するようにする。

(もっと読む)

半導体装置

【課題】異なる電圧で動作する回路を備えた半導体装置において、面積の増加を抑制することのできる半導体装置を提供する。

【解決手段】半導体装置は、外部端子10に接続され、該外部端子から入力される第1電圧で動作する第1回路20と、外部端子に抵抗素子を介して接続され、第1電圧より絶対値が小さい第2電圧で動作する第2回路40と、抵抗素子と第2回路との間の第1ノードに接続され、制御信号により導通と非導通とのいずれか一方が選択される分圧素子と、を具備する。分圧素子は、第1電圧が外部端子に印加され第1回路を動作させる場合、制御信号により導通状態が選択される。

(もっと読む)

半導体集積回路装置

【課題】電源供給能力を向上させる場合のチップサイズの増大を抑える。

【解決手段】外部接続端子14a(14b)と、外部接続端子14a(14b)に出力端を接続し、CMOS回路で構成されるバッファ回路12a(12b)と、バッファ回路12a(12b)の入力端を、第1の動作モード時には出力信号Sout1(Sout2)に従ってハイレベルまたはローレベルに変化させ、第2の動作モード時には出力信号Sout1(Sout2)のレベルに係らずハイレベルおよびローレベルの一方に固定する論理回路10a(10b)と、を備える。

(もっと読む)

半導体装置、入力選択制御方法

【課題】端子数の異なる各パッケージに搭載されても制御プログラムの流用性を維持する半導体装置、入力選択制御方法を提供する。

【解決手段】半導体装置は、複数の入力端子と、アナログ入力パッドと、情報保持部と、チャネル指定部と、チャネル変換部と、AD変換部とを具備する。複数の入力端子は、チャネル番号により識別され、アナログ信号を入力する。アナログ入力パッドは、パッド番号により識別され、入力端子に接続される。情報保持部は、入力端子に関する情報を保持する。チャネル指定部は、入力端子のそれぞれを識別するチャネル番号のうちの1つを指定するチャネル指定信号を生成する。チャネル変換部は、情報に基づいて、チャネル指定信号により示されるチャネル番号をパッド番号に変換する。AD変換部は、指定されたパッド番号に対応するアナログ入力パッドから入力されるアナログ信号をアナログ・デジタル変換する。

(もっと読む)

集積回路装置及び電子機器

【課題】様々な電気光学パネルに対応できる集積回路装置等の提供。

【解決手段】集積回路装置は、コモン信号又はセグメント信号を出力する第1〜第nの出力セルQ1〜Qnと、第1〜第nの出力セルQ1〜Qnの制御を行う制御回路10を含む。第1の出力モードでは、第1〜第nの出力セルQ1〜Qnのうちの第1〜第iの出力セルQ1〜Qiがコモン信号を出力し、第1〜第nの出力セルQ1〜Qnのうちの第j〜第kの出力セルQj〜Qkがセグメント信号を出力する。第2の出力モードでは、第1〜第iの出力セルQiがセグメント信号を出力し、第j〜第kの出力セルQj〜Qkがコモン信号を出力する。

(もっと読む)

集積回路装置及び電子機器

【課題】様々な電気光学パネルに対応した場合にも適正な表示画像を得ることができる集積回路装置等の提供。

【解決手段】集積回路装置は駆動回路と制御回路を含み、制御回路はアドレス制御回路を含む。表示メモリーには電気光学パネルの第1、第2の表示領域の表示データを記憶する第1、第2のメモリー領域MR1、MR2が確保される。アドレス制御回路は、第1の表示モードでは第1、第2のメモリー領域MR1、MR2のアドレスを、第1のアドレスAD1から第NのアドレスADNへと変化させて、表示データを読み出し、第2の表示モードでは、第1のメモリー領域MR1のアドレスについては第1のアドレスAD1から第NのアドレスADNへと変化させ、第2のメモリー領域MR2のアドレスについては第NのアドレスADNから第1のアドレスAD1へと変化させて表示データを読み出す。

(もっと読む)

半導体装置

【課題】半導体集積回路にDAコンバータが内蔵され、且つ、上記DAコンバータとデジタル回路とでパッドが共有される場合のアナログ電源電圧の動作範囲を改善する。

【解決手段】複数の抵抗が結合されて成るラダー抵抗回路を含むR−2R型DAコンバータ(106)と、デジタル信号の入出力を可能とするデジタル回路(601)と、上記DAコンバータの出力ポートと上記デジタル回路の入出力ポートとの間で共有されるパッド(602)とを設ける。そして、上記R−2R型DAコンバータが非アクティブ状態とされるとき、上記ラダー抵抗回路を上記R−2R型DAコンバータから切り放すためのスイッチ制御回路(20)を設け、上記DAコンバータのアナログ信号出力ポートを導電ライン(320)によって上記パッドに直結することで、アナログ電源電圧の動作範囲を拡大する。

(もっと読む)

半導体装置

【課題】特性劣化を生ずることなく、半導体装置における外部端子の割り当て変更を可能とする。

【解決手段】マイクロコンピュータ(40)は、複数の外部端子(51−1,51−2,52−1,52−2,53−1,53−2)と、上記外部端子を介して入力又は出力されるデータを取り扱うデータ系機能部(11,12)と、上記外部端子を介して入力又は出力されるクロック信号を取り扱うクロック系機能部(13)とを含む。このとき、上記データ系機能部及び上記クロック系機能部に対する上記外部端子の割り当ての変更を可能とする端子割り当て変更回路(21〜23)を設ける。互いに端子割り当て仕様が異なる半導体装置間で、外部端子の配列順番を整合させることができるので、特性劣化を生ずることはない。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】インターフェース回路の端子を共通化できる集積回路装置、電気光学装置及び電子機器を提供すること。

【解決手段】本発明は、シリアルバスを介して差動信号を受信するレシーバ回路42と、差動信号が入力される端子DP、DMと、レシーバ回路用の電源電圧が供給される電源端子VDDAと、端子DPとノードN1との間に設けられた終端抵抗R1と、端子DMとノードN2との間に設けられた終端抵抗R2と、ノードN1とN2の間に設けられたトランジスタTP、TN(スイッチ素子)を含む。トランジスタTP、TNは、レシーバ回路用電源端子VDDAからの電圧に基づいて、高速シリアルインターフェースモードにおいてオンし、パラレルインターフェースモードにおいてオフする。

(もっと読む)

集積回路

【課題】 温度検出素子を備えた集積回路に、温度検出素子が検出した温度情報を出力する機能を追加しつつ、端子数の増加を防止する。

【解決手段】 第1の抵抗と温度検出素子が直列に接続された第1の直列回路と、前記第1の抵抗とトランジスタが直列に接続された第2の直列回路と、駆動対象を駆動する駆動回路が停止すべき状態であることを検出した場合に、前記トランジスタをオンすることにより、前記第2の直列回路の接続点に前記駆動回路の動作を停止させるための制御信号を発生させる検出回路と、前記第1の直列回路の接続点および前記第2の直列回路の接続点に共通に接続される端子と、を有する。

(もっと読む)

半導体集積回路

【課題】リードフレームのピン数を従来よりも削減することが可能な半導体集積回路を提供すること。

【解決手段】半導体チップ14上に形成され、かつ出力信号が択一的に選択されて外部の使用に供される第1機能別回路19及び第2機能別回路20の各々についてリードフレームを設けるのではなく(つまり2つのリードフレームを設けるのではなく)、外部の使用に供される出力信号の個数分だけ(つまり1個)のリードフレーム12cにみを設けるので、第1機能別回路19及び第2機能別回路20の各々についてリードフレームを設ける場合よりもリードフレームの個数を削減することが可能である。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路においてコストの増大を伴うことなく外部端子の異常状態(出力短絡状態および入力開放状態)を検出する技術を提供する。

【解決手段】 半導体集積回路(MCU)は、複数の入出力回路(IO1〜IO4)、監視対象指定回路(DPSEL)および異常検出回路(PCDET)を備える。複数の入出力回路(IO1〜IO4)は、複数の外部端子(P1〜P4)に対応して設けられる。監視対象指定回路(DPSEL)は、複数の外部端子(P1〜P4)の中から監視対象外部端子を可変指定する。異常検出回路(PCDET)は、監視対象外部端子に対応する入出力回路が出力回路として機能している場合に監視対象外部端子の出力短絡状態を検出し、監視対象外部端子に対応する入出力回路が入力回路として機能している場合に監視対象外部端子の入力開放状態を検出する。

(もっと読む)

1 - 20 / 66

[ Back to top ]