Fターム[5F038BG02]の内容

Fターム[5F038BG02]に分類される特許

1 - 20 / 208

半導体集積回路

半導体装置

半導体集積回路

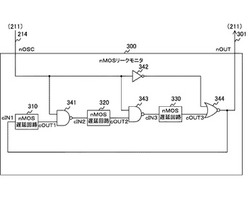

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体装置

【課題】低電圧で動作するとともに高電圧が入力された場合でも破壊することがないチャージポンプ回路を備えているとともに、通常の量産用の半導体製造プロセスが適用可能な半導体装置を提供する。

【解決手段】半導体装置において、チャージポンプ回路30は、薄膜トランジスタで構成され、外部電源電圧を昇圧する。スイッチ制御部11は、外部電源電圧が基準電圧を超えている場合には、チャージポンプ回路30への外部電源電圧の供給が遮断されるようにするとともに外部電源電圧がチャージポンプ回路30を介さずに負荷回路50に直接供給されるようにする。基板電圧制御部14は、外部電源電圧が基準電圧以下の場合に、チャージポンプ回路30を構成するトランジスタの基板領域に順方向となるバイアス電圧を供給する。

(もっと読む)

昇圧回路

【課題】負荷電流に応じて昇圧能力を調整することにより、過剰な昇圧回路出力リップルを抑制する。

【解決手段】昇圧回路1は、昇圧部出力CPOの電圧を変動させて昇圧回路出力VPPを生成し、昇圧回路出力VPPの負荷電流の大きさに応じて制御電圧CON1を生成する制御部2と、制御電圧CON1に応じて電源VDDP1の電圧を変動させることにより昇圧部電源VDDPを生成する電源降圧部3と、昇圧回路出力VPPの電圧と目標電圧との差分に応じて昇圧部電源VDDPの電圧を変動させることにより昇圧部出力CPOを生成する昇圧部4とを備える。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

MOSトランジスタ集積回路およびMOSトランジスタ劣化度合模擬算出システム

【課題】MOSトランジスタ集積回路中のリング発振器では、使用期間が長くなるとそれを構成しているMOSトランジスタの特性に劣化が生じ、発振周期が大になって来る。従って、劣化度合を量的に把握する必要があったが、個別の集積回路につき、MOSトランジスタの劣化度合を算出するようにしたものは従来なかった。

【解決手段】リング発振器2を集積するMOSトランジスタ集積回路1内に、NMOSトランジスタの劣化のみ生ずる構成にしたリング発振器4、PMOSトランジスタの劣化のみ生ずる構成にしたリング発振器5を作り込む。それらの現時点での発振周期もしくは製造当初の発振周期を基に、劣化による増加遅延時間や発振周期を模擬算出装置7で算出する。

(もっと読む)

電源回路システム

【課題】チャージポンプ回路の消費電流を所定の昇圧電圧を得るために必要最小限に抑える電源回路システムを提供する。

【解決手段】電源回路システム100は、可変抵抗回路10を備えたリング発振器20と、リング発振器20の発振出力信号OSC_OUTに応じて昇圧電圧HVを出力するチャージポンプ回路30、チャージポンプ回路30の昇圧電圧HVを調整する電圧レギュレータ回路40、電圧レギュレータ回路40に流れる第1の電流I0と、第1の基準電流とを比較する第1の電流比較回路50、前記第1の電流I0と、第2の基準電流を比較する第2の電流比較回路60、第1及び第2の電流比較回路50,60の第1及び第2の比較信号SIG_UP9U,SIG_UP18Uに応じて、可変抵抗回路10の抵抗値を制御するための制御信号(SEL2,SEL1,SEL0)を出力する制御回路70と、を含んで構成される。

(もっと読む)

電子回路

【課題】簡易な構成でありながら正確に同期したクロックを各基板に分配することができる電子回路を提供すること。

【解決手段】第1コイルL1と第1キャパシタC1による第1共振回路を含む第1発振器21を有する第1基板11と、第2コイルL2と第2キャパシタC2による第2共振回路を含む第2発振器22を有する第2基板12とを備え、前記第1コイルL1と第2コイルL2が誘導結合して前記第1発振器21と第2発振器22が結合共振することを特徴とする電子回路。

(もっと読む)

半導体集積回路パッケージ、および受信装置

【課題】電源および/またはグランドを介したスプリアス・ノイズ対策と、端子数の削減との両立を可能とする、半導体集積回路パッケージ、およびそれを備えた受信装置を実現する。

【解決手段】MOP−IC3は、I/O PAD2において、所定数のグランド端子6bおよび7bに関して、アナログ回路がグランド端子6bと接続されており、デジタル回路がグランド端子7bと接続されており、グランド端子6bおよび7bはいずれも、ダウンボンド10および11によりそれぞれ、リードフレーム4の裏面共通グランド5に接続されている。

(もっと読む)

半導体装置

【課題】テストパターンの内容、あるいは回路規模によらず、動作試験が短時間且つ高効率で行える半導体装置の実現。

【解決手段】フリップフロップ回路37と、試験モード時に、フリップフロップ回路に所定の値を設定すると共にフリップフロップ回路の保持する値を読み出すスキャンチェーンと、通常モード時に非動作で、試験モード時には、フリップフロップ回路の値が変化する場合に動作状態となり、前記フリップフロップ回路の値が変化するタイミングで非動作状態になる電流消費回路37A,37Bと、を有する半導体装置。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

1 - 20 / 208

[ Back to top ]