Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

1,561 - 1,574 / 1,574

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

キャパシタ

集積回路の中にキャパシタを作製する方法。本発明の基本形態にかかるキャパシタは、容量を増大させるために強いフリンジング電界を利用する。これは平面に平行な平板ではなくて、集積回路の中の2つの面の間に垂直な、重畳している導電性電極を持ったキャパシタを作製することによって達成される。本発明のキャパシタは水平な平板、すなわち平行な平板を付加的に備えていてもよい。本方法によるキャパシタも開示されている。  (もっと読む)

(もっと読む)

電圧発生回路と半導体集積回路装置

第1電流がエミッタに流れるようにされた第1トランジスタと、上記第1トランジスタよりも大きな電流密度となるような第2電流がエミッタに流れるようにされた第2トランジスタとのベース,エミッタ間の電圧差を第1抵抗に流して定電流を形成し、それと直列にして第2抵抗を回路の接地電位側に設け、上記第1トランジスタと第2トランジスタのコレクタと電源電圧との間に第3抵抗と第4抵抗とを設け、上記第1と第2トランジスタの両コレクタ電圧とCMOS構成の差動増幅回路に供給して、出力出力電圧を形成するとともに、かかる出力電圧を上記第1トランジスタと第2トランジスタのベースに共通に供給する。 (もっと読む)

集積回路製造をモニタするためのテスト構造体またはライン・アレイを接続するための方法および構成

テスト・チップは、各領域が少なくとも1つのテスト構造体を含むことができる複数領域のアレイを有する少なくとも1つのレベルを具える。その少なくとも幾つかの領域はそれぞれのテスト構造体を含む。そのレベルは、テスト構造体に入力信号を供給する複数のドライバ・ラインを有する。そのレベルは、テスト構造体から出力信号を受信する複数の受信機ラインを有する。そのレベルは、電流を制御するための複数のデバイスを有する。各テスト構造体は、ドライバ・ラインの中の少なくとも1本のラインに、その間にあるそのデバイスの中の第1のデバイスで接続される。各テスト構造体は、受信機ラインの中の少なくとも1本のラインにその間にあるそのデバイスの中の第2のデバイスで接続されていて、そのテスト構造体の各々がドライバ・ラインおよび受信機ラインを用いてテストを行うべく個々にアドレス可能である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

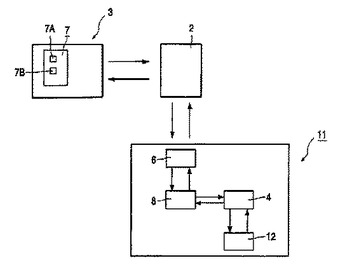

半導体デバイス、認証方法およびシステム

本発明の半導体デバイス(11)は回路と保護構造(50)とを備える。本発明の半導体デバイス(11)は、第1および第2のセキュリティ素子(12A、12B)と、入力および出力(14、15)とを備える。セキュリティ素子(12A、12B)は、異なる第1および第2のインピーダンスをそれぞれ有する。このデバイスはさらに、測定手段、処理手段および接続手段を備える。処理手段は、受け取られた第1の情報を特定の測定プログラムに変換する。これによって、デバイス(例えばスマートカード)のオーセンティシティをチェックし、またはアイデンティティを確立するために、デバイス(11)および読取り装置中にチャレンジ−レスポンス機構が実装される。  (もっと読む)

(もっと読む)

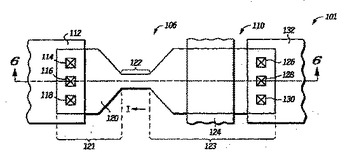

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

アナログセルレイアウト設計装置および方法

【課題】 アナログセルレイアウトの設計制約を設計者の熟練度に依らずに回路図データから自動予測することができるようにすること。

【解決手段】 回路図作成部1にて作成されたアナログ回路図のデータが回路図記憶部2に書き込まれる。回路接続情報抽出部3では、回路図記憶部2に記憶されるアナログ回路図データから抽出された回路接続情報が回路接続情報記憶部4に書き込まれる。設計制約予測抽出部5では、回路接続情報記憶部4に記憶される回路接続情報からペアリングの必要な素子が予測・抽出され、回路接続情報に設計制約として付加され、回路接続情報記憶部6に書き込まれる。自動配置部9では、回路接続情報記憶部6に記憶される設計制約を含む回路接続情報に基づきレイアウトセルの配置が実行される。自動配線部11では、配置後レイアウト記憶部10に記憶されたレイアウトセル間の配線が実行される。

(もっと読む)

半導体集積回路

【課題】 ある機能ブロック内の回路に間違いがあった場合における予備素子への配線切り替えを簡単に行うことができるようにするとともに、予備素子への配線長もできるだけ短くできるようにする。

【解決手段】 機能ブロック2a〜2f内の回路に間違いがあったときに代用する予備素子11〜16を、機能ブロック2a〜2f間のデッドスペース100ではなく、機能ブロック2a〜2f内に配置することにより、ある機能ブロック内の回路に間違いがあった場合における予備素子への配線の際に、他の機能ブロックが邪魔になることがないようにするとともに、同じ機能ブロック内で配線することによって予備素子への配線長も短くできるようにする。さらに、既に拡散工程が済んでいる機能ブロック2a〜2fに予備素子を配置することで、メタル配線の工程から作業を開始すれば良いようにする。

(もっと読む)

自動配置配線装置及びそれを用いる配置配線方法

【課題】 ハードマクロブロックの周辺のようにバッファセル等を挿入することが困難なセル混雑部分や、隣接配線の間隔を広げることが困難な配線混雑部分での、隣接配線間容量値を削減してクロストークノイズを低減させる。

【解決手段】 外部インタフェースを有する複数種類のクロストークノイズ改善用セルをハードマクロブロックの内部の隙間部分に埋め込み、そのクロストークノイズ改善用セルを選択して半導体集積回路の配線に挿入する。隣接する配線の信号遷移期間が重なる場合、改善用セルを遷移期間の長い方の配線に挿入する。または、隣接する配線のうち一方の配線を他の配線層に移動させ、それにより空いた領域にシールド線を配線する。

(もっと読む)

半導体装置

【課題】 フィールドスルー電荷補償機能を備えるアナログスイッチにおいて、半導体製造工程の誤差によらず、スィッチング用のMOSトランジスタのフィールドスルー電荷を安定に補償し、アナログスイッチ動作時の入出力間の誤差を低減できる構造を実現する。

【解決手段】 入力端子INと出力端子OUTの間に同一サイズの2つのトランジスタ1a、1bを、電気的に並列に、また物理的には相対するように配置し、トランジスタ1a、1bの入力端子IN側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ2を配置し、トランジスタ1a、1bの出力端子OUT側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ3を配置し、製造工程の誤差によって、位置ずれが発生しても、トランジスタ1a、1bのソース側の寄生容量の総和および、ドレイン側の寄生容量の総和が不変であるようにし、トランジスタ1a、1bのスィッチング動作に伴うフィールドスルー電荷の補償が、設計通りにできるようにした。

(もっと読む)

配線構造、インダクタ及びそれらの形成方法

【課題】 レイアウト設計上の自由度が大きく、しかも経済的に形成できる構成を備えた配線構造、インダクタ及びそれらの形成方法を提供する。

【解決手段】 本多層インダクタ60は、1層目のインダクタ64と、第1の層間絶縁膜66を介して1層目のインダクタ上に形成された2層面のインダクタ68と、第2の層間絶縁膜70を介して2層目のインダクタ上に形成された3層目のインダクタ72とを備えている。1層目のインダクタは、第1の層間絶縁膜を貫通するコンタクト76を介して2層目のインダクタに接続されている。2層目のインダクタは、第2の層間絶縁膜を貫通するコンタクト78を介して3層目のインダクタに接続されている。3層目のインダクタは、コイル巻線が接続配線74上をエアーブリッジ構造で跨いでいる。接続配線は、コイル巻線の下を通り、コイル巻線の中心部の接続端からコイル巻線に電気的に接触することなく多層インダクタの外部に出ることができる。

(もっと読む)

1,561 - 1,574 / 1,574

[ Back to top ]