Fターム[5F038CD03]の内容

Fターム[5F038CD03]に分類される特許

1 - 20 / 245

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

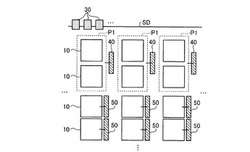

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

電源制御装置

【課題】ラッシュカレントを抑えて、電源電圧の供給・非供給を切り替えることができる電源制御装置を提供する。

【解決手段】電源制御装置は、第1の電源線1と、第2の電源線3と、制御回路と、制御信号線4と、第1の配線と、第2の配線と、第3の配線とを備える。第1の電源線は、基準電源電圧が供給される。第2の電源線は、内部回路に接続される。制御信号線は、前記制御回路に接続され、前記接続を制御する制御信号を供給する。第1の配線は、半導体基板の上方の配線層に形成され、トランジスタの第1の端子と前記第1の電源線とを接続する。第2の配線は、前記半導体基板の上方の配線層に形成され、前記トランジスタの第2の端子と前記第2の電源線とを接続する。第3の配線は、前記半導体基板の上方の配線層で、かつ、前記トランジスタの制御端子の上方に配置されて、前記制御信号線と一体に形成される。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

半導体集積回路装置

【課題】バイアス電流を配給する際のノイズ耐性を大幅に向上させる。

【解決手段】基準バイアス電流回路11は、基準バイアス電流Ipと該基準バイアス電流Ipと電流の極性が逆となる基準バイアス電流Inとを生成し、2本の配線を1ペアとしたバイアス電流用配線H1を介してバイアス電流回路2aに供給する。ペアの配線のうち、一方の配線は他方の線の近傍に平行してレイアウトされており、これら配線の配線長が略同じとしている。バイアス電流回路2aでは、基準バイアス電流Ipを反転させ、基準バイアス電流Inに加算した後、必要なバイアス電流となるように調整し、バイアス電流を生成する。

(もっと読む)

半導体装置

【課題】交流リークが電圧検出回路に流れるのを防ぐことができる半導体装置を提供する。

【解決手段】半導体装置は、アンテナ回路102と、共振周波数調整回路126と、電圧検出回路と、第1の容量素子と、を有する。共振周波数調整回路126は、一方の端子がアンテナ回路102の第1の端子と電気的に接続された第2の容量素子と、第1の端子が第2の容量素子の他方の端子と電気的に接続され、第2の端子がアンテナ回路102の第2の端子と電気的に接続され、ゲートが第1の容量素子及び電圧検出回路と電気的に接続されたトランジスタと、を有する。

(もっと読む)

1 - 20 / 245

[ Back to top ]