Fターム[5F038CD15]の内容

Fターム[5F038CD15]の下位に属するFターム

ON・OFF制御 (837)

Fターム[5F038CD15]に分類される特許

1 - 20 / 261

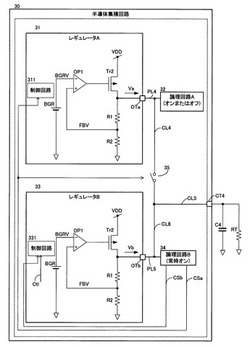

半導体装置

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

昇圧回路を備えた半導体装置

【課題】回路面積を縮小でき、昇圧効率の高い昇圧回路を備える半導体装置を提供する。

【解決手段】出力電圧を監視するモニタ電圧MON1に基づいて、出力電圧を所定電圧に制御する制御回路と、出力電圧を通常動作時に第1電圧に設定し、評価時に第1電圧より高い第2電圧に設定するトランジスタTR4,TR5と、出力電圧の振幅をクロック信号の振幅としてクロック信号を発生するクロックドライバ11と、コンデンサ及びダイオードを含む単位回路21が直列に複数段接続され、コンデンサに入力されるクロック信号により電源電圧VCCを昇圧するチャージポンプ12とを備える。

(もっと読む)

半導体装置及びこれを備えたメモリシステム

【課題】電源の瞬断および過渡状態での急激な電圧変動を起こさずに電源電圧を切り替えできる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、電源スイッチと、降圧型の第1のレギュレータと、を備える。前記半導体装置は、入力端子に供給された外部電源電圧に基づいて内部電源電圧を出力端子から出力する。前記電源スイッチは、一端が前記入力端子に接続され、他端が前記出力端子に接続されている。前記第1のレギュレータは、前記電源スイッチの前記一端に接続された電源端子と、前記電源スイッチの前記他端に接続された電圧出力端子と、を有し、前記電源端子の電圧に基づいて前記電圧出力端子の電圧を目標電圧に近づくように制御する。前記目標電圧は、前記電源端子の電圧以上の第1電圧又は前記電源端子の電圧より低い第2電圧に切り替えられる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体回路

【課題】ノーマルモードとスタンバイモードとの切替が、外部容量を必要とせず、レギュレータの出力電圧を安定できる半導体装置を提供することを課題とする。

【解決手段】回路の動作がノーマルモードとスタンバイモードを有し、ノーマルモードを設定する信号の入力とスタンバイモードを設定する信号の入力とで各々独立して一定の電圧を発生する電圧発生回路を備え、ノーマルモードを設定、および解除する信号に対し、すくなくともスタンバイモードを設定する信号を遅延させる遅延回路を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体集積回路のレイアウト設計装置、半導体集積回路のレイアウト設計方法及びプログラム

【課題】信号の遅延調整を柔軟に行なうことができる半導体集積回路レイアウト設計装置を提供する。

【解決手段】図1に示す半導体集積回路レイアウト設計装置は、配線部と遅延調整部を備える。配線部では、第1の配線層の配線上に、第2の配線層では接続先となる配線がないビア(未接続ビア)を形成する。その後、遅延調整部において、遅延時間の調整が必要であれば、未接続ビアから、遅延調整に適したビアを選択し、第1の配線上のビア間の配線を削除する。その後、第2の配線層において第1のビアと第2のビアを配線する。その結果、信号配線の抵抗は、ビアの持つ抵抗値の分上昇し、遅延時間の調整を行なうことができる。

(もっと読む)

マルチチャネル半導体装置及びそれを具備したディスプレイ装置

【課題】別途のプローブ接続用パッドなしに、出力チャネルの個数より少ない個数のプローブを接続して多数の出力チャネルの出力信号をモニタリングすることができるマルチチャネル半導体装置及びそれを具備するディスプレイ装置を提供する。

【解決手段】少なくとも1つの出力バッファを具備する複数のバッファ・グループ;少なくとも1つの出力パッドを具備する複数のパッド・グループ、及び複数のバッファ・グループ;複数のパッド・グループとの連結を制御するチャネル・スイッチング部;を含むマルチチャネル半導体装置であり、該複数のパッド・グループのうち1つのパッド・グループは、第1動作モードで、対応するバッファ・グループの出力信号を出力し、第2動作モードで、複数のバッファ・グループの出力信号を順次に出力する。

(もっと読む)

1 - 20 / 261

[ Back to top ]