Fターム[5F038CD19]の内容

Fターム[5F038CD19]に分類される特許

1 - 20 / 91

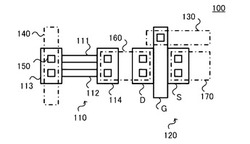

半導体装置

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】スパイラルインダクタを有する半導体装置における寄生容量の低減と、Q値の低下を抑制すること。

【解決手段】半導体基板と、前記半導体基板の表面近傍に設けられた複数個の素子分離領域と、前記素子分離領域間の半導体基板上に設けられた能動素子部と、基板上に積層された複数の配線層と、前記素子分離領域のうち第1の素子分離領域の鉛直上方であって、かつ、前記配線層のうち少なくとも最上の配線層に設けられたスパイラルインダクタとを備え、前記スパイラルインダクタが形成されたインダクタ形成領域の鉛直下方であって、かつ、前記第1の素子分離領域の半導体基板表面上にシリサイド形成防止膜が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ面積の増加を抑えつつ、金属等からなるゲート電極を有するMISトランジスタと、抵抗体とを同一基板上に不具合なく形成する。

【解決手段】半導体装置は、半導体基板1上にそれぞれ設けられたMISトランジスタと抵抗素子とを備える。MISトランジスタは、活性領域1aと、活性領域1a上に設けられたゲート絶縁膜18と、ゲート絶縁膜18上に設けられたゲート電極19とを有する。抵抗素子40は、素子分離領域2上に設けられた抵抗体10を有しており、ゲート電極19の少なくとも一部は、抵抗体10よりも小さな抵抗率を有しており、活性領域1a上においてはゲート電極19の上面を覆っておらず、抵抗体10の上面を覆っている層間絶縁膜16がさらに設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の製造方法

【課題】半導体記憶装置の面積を縮小する技術を提供する。

【解決手段】高抵抗付加型ラッチ回路(12)と、その高抵抗付加型ラッチ回路(12)に保持されるデータの読み出しと書込みとを制御する選択回路(13)とを具備する半導体記憶装置(11)を構成する。その高抵抗付加型ラッチ回路(12)は、第1駆動トランジスタ(22)と、第2駆動トランジスタ(24)と、第1抵抗(121)と、第2抵抗(123)とを備えることが好ましい。また、その選択回路(13)は、第1選択トランジスタ(31)と、第2選択トランジスタ(32)とを備えることが好ましい。ここにおいて、その第1抵抗(121)と第2抵抗(123)とは、サイドウォール状の導電性材料(21)(23)で形成されるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】フューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置を提供する。

【解決手段】半導体基板上にフィールド酸化膜を介して抵抗体を設け、抵抗体上に第一の金属配線を設け、第一の金属配線上に吸湿性膜を含む平坦性の良い金属間層間膜を形成する。抵抗体のトリミング用フューズは吸湿性膜を含む金属間層間膜の上に形成することで吸湿性膜の露出を防止する。

(もっと読む)

偽装トランジスタをカムフラージュするためのシリコンブロックプロセスステップの使用

【課題】アーチファクト縁部を利用してリバースエンジニアを混乱させる半導体デバイスおよび半導体デバイスを製造する方法を提供する。

【解決手段】輪郭を管理した導電性材料の層を配置して、デバイスが実際には動作不能であるときに、動作可能なデバイスのような導電性材料のアーチファクト縁部を形成する。実際に形成されるデバイスの特徴を示さないアーチファクト縁部を提供することにより、集積回路構造をカムフラージュするたの技術および構造である。

(もっと読む)

多結晶シリコン抵抗

【課題】多結晶シリコン抵抗の特性バラツキを抑制する。

【解決手段】結晶粒を有する多結晶シリコン膜(2)と、多結晶シリコン膜(2)の上に設けられ、多結晶シリコン膜(2)の第1端部から第1距離(d1)の位置に配置された第1接続領域(3)と、多結晶シリコン膜(2)の上に設けられ、第1端部と異なる第2端部から第2距離(d2)の位置に設けられた第2接続領域(3)とを具備する多結晶シリコン抵抗(1)を構成する。その多結晶シリコン抵抗(1)おいて、多結晶シリコン膜(2)は、第1端部と第1接続領域(3)との間の第1部分(6)と、第2端部と第2接続領域(3)との間の第2部分(7)と、第1接続領域(3)と第2接続領域(3)との間の第3部分(8)とを具備するものとする。そして、第3部分(8)に含まれる結晶粒の結晶粒径は、第1部分(6)または第2部分(7)に含まれる結晶粒の結晶粒径よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】静電保護素子である保護トランジスタのサイズを縮小することができ、ゲート端子の抵抗成分を同程度に抑え、時定数を増加させることなく、保護トランジスタの回路動作スピードの低下を防ぐことができるとともに、電荷集中を緩和し、静電破壊耐量を向上させることができる。

【解決手段】本発明に係る半導体装置は、ソース・ドレイン領域と、ソース・ドレイン領域の上方に形成されたゲート電極と、ゲート電極の側面に形成されたサイドウォールと、ソース・ドレイン領域の上面に、サイドウォールから所定の距離だけ離間して形成された第1のシリサイド膜と、ゲート電極の上面に、サイドウォールから所定の距離だけ離間して形成された第2のシリサイド膜とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

半導体装置

【課題】ポリシリコン配線構造を利用する場合にプログラム後の抵抗値のばらつきがなく高抵抗値化が図れ、良好なプログラム特性や高信頼性を有する半導体装置を提供する。

【解決手段】第1の端子部12aと、第2の端子部12cと、前記第1および第2の端子部の相互間を接続するヒューズリンク12bとを有する半導体装置であって、前記第1の端子部および前記ヒューズリンクは、不純物イオンがドープされたポリシリコン層とその上に積層された金属元素を含む層とを有し、前記第2の端子部は、前記ヒューズリンクとの接続端側に不純物イオンがドープされていないポリシリコン層とその上に積層された金属元素を含む層とを有する。

(もっと読む)

トレラント及びフェールセーフ設計のためのロバストなESD保護回路、方法及び設計構造体

【課題】 トレラント及びフェールセーフ設計のためのロバストなESD保護回路、方法及び設計構造体を提供する。

【解決手段】 トレラント及びフェールセーフ設計のためのロバストなESD保護回路、方法及び設計構造体が開示される。回路(200)は、ESD事象中、積層型NFET静電放電(ESD)保護回路(パッド215、接地220、上部NFET225、下部NFET230、上部抵抗器235、及び下部抵抗器240)の上部NFET(225)をオフにする中間接合部制御回路(250)を含む。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留りを向上させる。

【解決手段】素子分離領域2を含む半導体基板1上に多結晶シリコン膜7と絶縁膜8を形成してパターニングし、多結晶シリコン膜7かならる下部電極11a,11bおよび下部電極11a,11b間のダミーパターン12を形成する。下部電極11a,11bおよびダミーパターン12とそられの上に形成された絶縁膜8を覆うように多結晶シリコン膜17を形成し、多結晶シリコン膜17上にキャップ保護膜を形成する。キャップ保護膜上に反射防止膜およびフォトレジストパターンを形成し、フォトレジストパターンをエッチングマスクとして用いて反射防止膜、キャップ保護膜および多結晶シリコン膜17を順次ドライエッチングすることで、下部電極11a,11b上に容量絶縁膜としての絶縁膜8を介して多結晶シリコン膜17からなる上部電極21a,21bを形成してキャパシタ36a,36bを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

1 - 20 / 91

[ Back to top ]