Fターム[5F043BB08]の内容

ウェットエッチング (11,167) | エッチング液、洗浄液、表面処理液 (2,072) | III−V族化合物半導体用 (228) | In−P系用 (27)

Fターム[5F043BB08]に分類される特許

1 - 20 / 27

半導体装置の製造方法

【課題】本発明は、Br−アルコール液を有するエッチング液のエッチングレートを安定させることができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、Brをアルコールで希釈した溶液に、該アルコールよりも比重が小さく、かつ該アルコールに難溶解性の液体である封止液を加えたエッチング液に、ウエハを浸漬させて該ウエハをエッチングするエッチング工程を備えたことを特徴とする。

(もっと読む)

半導体光素子の製造方法

【課題】過剰なエッチングを抑制するとともに半導体表面の突起物を除去する半導体光素子の製造方法を提供する。

【解決手段】半導体光素子の製造方法は、エッチストップ層13及び複数の半導体層を含み、半導体光素子のための半導体積層10を半導体基板11の主面11aにエピタキシャル成長させる半導体積層成長工程と、半導体積層10の最表面から突出する突起物の先端部が露出するように、最表面にマスク層を形成するマスク層形成工程と、マスク層を用いて、ウェットエッチングにより突起物をエッチングするウェットエッチング工程と、ウェットエッチングの後に、ドライエッチングにより突起物を除去するドライエッチング工程と、突起物を除去した後に、最表面からマスク層を除去するマスク層除去工程と、マスク層を除去した後に、半導体積層10に半導体光素子のための加工を行う加工工程と、を備えている。

(もっと読む)

光集積素子の製造方法

【課題】バットジョイント構造を構成する第1及び第2の半導体積層部上に成長する半導体層に生じる結晶欠陥を低減する。

【解決手段】エッチングマスク30を用いて第1の半導体積層部20にエッチングを施す工程と、Alを含む光吸収層42、及び光吸収層42上に設けられるInPクラッド層44を有する第2の半導体積層部40を、エッチングマスク30を用いて選択的に成長させる第1の再成長工程と、エッチングマスク30を除去するマスク除去工程と、第1及び第2の半導体積層部20,40上に第3の半導体積層部を成長させる第2の再成長工程とを行う。第1の再成長工程において、InPに対してエッチング選択性を有するInP系化合物半導体を含むキャップ層46を第2の半導体積層部40上に更に成長させる。マスク除去工程の前に、エッチングマスク30上に生じたInP系堆積物Deを除去する。

(もっと読む)

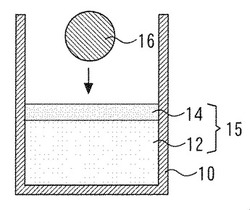

エッチング液組成物およびエッチング方法

【課題】エッチングにより、適切に、エッチング対象物の表面に凹凸形状を形成して粗面化を行うことができるエッチング液組成物を提供する。

【解決手段】エッチング液組成物は、エッチング対象物の表面16をエッチングして凹凸形状を形成するエッチング液組成物であって、有機酸、有機酸塩、無機酸、無機酸塩、キレート剤、界面活性剤、糖アルコール類、フェノール類、アゾール類、および複素環化合物からなる群から選択される少なくとも一つと、酢酸と、フッ化水素酸と、硝酸とを含む。

(もっと読む)

光集積素子の製造方法

【課題】パッシブ素子の特性の設計値からの低下を抑制することができる光集積素子の製造方法を提供すること。

【解決手段】基板上に、活性コア層を含む半導体積層構造で形成された、アクティブ素子を形成するためのアクティブ領域と、パッシブコア層を含む半導体積層構造で形成された、パッシブ素子を形成するためのパッシブ領域とを形成し、アクティブ領域とパッシブ領域とに被覆部と開口部とを有する第1エッチングマスクを形成し、アクティブ領域およびパッシブ領域において開口部からドライエッチングを行い、アクティブ領域にアクティブ素子のアクティブメサ構造を形成するとともにパッシブ領域にパッシブ素子のパッシブメサ構造を形成し、パッシブ領域に第2エッチングマスクを形成し、パッシブメサ構造を第2エッチングマスクにて保護しながらアクティブメサ構造をウェットエッチングする、ことを含む。

(もっと読む)

光電素子及びその製造方法

【課題】本発明は光電素子及びその製造方法を提供する。

【解決手段】本発明による光電素子であって、表面及び表面と垂直する法線方向を有する基板と、基板の表面に位置して表面と接触する第一半導体層と、第一半導体層と基板の表面の間に位置する少なくとも一つの空洞構造とを有し、少なくとも一つの空洞構造は幅と高さを有し、幅は空洞構造における表面に平行する方向の最大寸法であり、高さは空洞構造における法線方向に平行する方向の最大寸法であり、高さは幅より小さい。

(もっと読む)

発光素子

【課題】光取り出し効率を向上させることのできる発光素子を提供する。

【解決手段】発光素子1は、第1半導体層と、第2半導体層と、第1半導体層と第2半導体層とに挟まれる発光層とを有する半導体積層構造10と、半導体積層構造10の一方の面上に設けられ、線状表面電極部を有する表面電極50と、半導体積層構造10の表面電極50が設けられる側の反対の面側に設けられ、光を反射する反射層32と、半導体積層構造10と反射層32との間に設けられる誘電体層と、半導体積層構造10と反射層32とを電気的に接続し、線状界面電極部を有する界面電極40とを備え、線状表面電極部と線状界面電極部とがそれぞれ、平面視にて予め定められた方向に沿って延び、半導体積層構造10が、半導体積層構造10の反射層32の反対側の表面に、予め定められた方向とは異なる方向に沿って設けられる溝80を有する。

(もっと読む)

半導体基板の製造方法

【課題】厚みのある半導体基板に対し、正確な位置でのへき開を可能とするような十分な深さのガイド溝を形成する半導体基板の製造方法を提供する。

【解決手段】本発明に係る半導体基板の製造方法は、インジウムリン化合物半導体またはガリウムヒ素化合物半導体からなる基板本体の表面に、開口幅が略40um以下である開口部が形成されたマスクを、その開口部が基板本体のへき開線に沿って延びるように転写する工程と、基板本体の表面に臭素系のエッチング液を用いてウエットエッチング処理を施すことによって、縦断面で略V字型を有するガイド溝を形成する工程と、ガイド溝に反応性ガスを用いてドライエッチング処理を施すことによって、底部の縦断面形状を略V字型に保持したままガイド溝の溝深さを深くする工程と、を含むものである。

(もっと読む)

エピタキシャルリフトオフを用いたフレキシブル光起電力デバイスの製造方法、およびエピタキシャル成長に用いる成長用基板の一体性を保持する方法

エピタキシャルリフトオフを用いる、フレキシブル光電(PV)デバイス等の感光性デバイスの製造方法が開示される。同様に、成長用基板を有する構造を含むフレキシブルPVデバイスを製造する方法が開示され、この方法では、保護層の選択的エッチングにより、再利用に好適な平滑な成長用基板が得られる。 (もっと読む)

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第2半導体が第1原子を第2濃度で含有し、かつ第2原子を含有し、前記第1原子が前記第2半導体に第1伝導型のキャリアを発生させ、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2原子が前記第2半導体におけるフェルミ準位と電荷中性準位との差を小さくする半導体基板提供する。

(もっと読む)

発光素子の製造方法

【課題】発光素子表面を粗面化して光出力を向上させるとともに、静電気による故障発生率を低減させた発光素子の製造方法を提供する。

【解決手段】GaAsと格子整合し、AlGaInPにて表される組成を有する化合物にて各々構成された第一導電型クラッド層、活性層及び第二導電型クラッド層がこの順序で積層されたダブルへテロ構造を有し、第二導電型クラッド層上に積層された透明半導体層とを有する発光素子ウェーハをダイシングすることで発光素子チップを形成し、その表面を、酢酸と弗酸と硝酸とヨウ素と水とを、その合計が90質量%以上となるように含有し、酢酸と弗酸と硝酸とヨウ素との合計質量含有率が水の質量含有率よりも高い第一のエッチング液にて第一のエッチング工程を行い、その後、等方性エッチング液を用いて発光素子チップ表面のエッチング取り代が0.12μm以下の第二のエッチング工程を行うことを特徴とする発光素子の製造方法。

(もっと読む)

化合物半導体装置とその製造方法

【課題】

隣接するAs系半導体層からのAsの拡散を防止できるP系化合物半導体層を成長する。

【解決手段】

化合物半導体装置の製造方法は、(a)化合物半導体基板上方に、第2のAs系化合物半導体層、第3のAs系化合物半導体層を形成する工程と、(x)第3のAs系化合物半導体層の上に、As濃度5×1017atoms/cm3〜3×1019atoms/cm3の範囲のAsをドーピングしつつ、V族元素がPである第1のP系化合物半導体層を形成する工程と、(y)第1のP系化合物半導体層の上にV族元素がAsである第1のAs系化合物半導体層を形成する工程と、を含む。

(もっと読む)

発光素子及びその製造方法

【課題】 素子の光取出面積をより拡大することができ、ひいては光取出効率の更なる向上を図ることができる発光素子を提供する。

【解決手段】 発光素子を構成する積層体の、光取出面をなす一方の主表面に有底孔LPを分散形成し、その有底孔LPの内面に異方性エッチング処理による微細な面粗し突起部を分散形成する。光取出面を平坦に形成する場合と比較して、面粗し対象面の総面積が有底孔LPを形成する分だけ増大し、これにさらに面粗し突起部Fを重畳形成することによって、面粗し突起の総形成量を増加させることができる。その結果、異方性エッチングによる面粗し処理のみを行なう従来の手法と比較して、素子の光取出面積をより拡大することができ、ひいては光取出効率の更なる向上を図ることができる。

(もっと読む)

半導体装置

【課題】 エッチング量を工程内で測定し、フィードバックをかけることにより、エッチング量のばらつきを無くすことを実現する。

【解決手段】 半導体層が選択エッチングされることにより半導体素子が形成される半導体素子領域と、前記半導体層と同じ材質からなり、前記半導体素子が選択エッチングされた量を検査するモニタ用半導体素子が設けられたモニタ領域とを有することを特徴とする。

(もっと読む)

超格子/量子井戸ナノワイヤ

【課題】 超格子/量子井戸構造体を含むセグメント化された半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】 セグメント化された半導体ナノワイヤは、テンプレートなしに、2つ又はそれ以上の半導体材料の層状構造体から材料を除去することによって製造する。除去は、層状構造体の表面上のいくつかの場所で起こり、優先的に結晶軸の方向に沿って進行するので、除去が殆どまたは全く生じなかった場所に、セグメント化された構造体を有するナノワイヤが残る。異なるセグメント間の界面は、ナノワイヤの長手方向に対して垂直であるか又はある角度をなしている。

(もっと読む)

III−V族半導体基板からのバルク金属汚染の除去方法

【課題】III−V族半導体基板からバルク金属汚染を除去するための単一工程の方法を提供する。

【解決手段】該方法は、金属汚染したIII−V族半導体基板を、体積比x:y H2SO4:H2O2(xは3〜9、yは1)を有する硫酸および過酸化物の混合物の中に浸漬することを含む。本発明の実施形態に係る方法を用いてIII−V族半導体基板を処理した後、バルク金属汚染は、基板からほぼ完全に除去できるとともに、処理後の基板の表面粗さは、2μm×2μmの表面グリッドに関して0.5nmRMS未満とすることができる。本発明は、半導体デバイスを製造する更なる処理ステップを実施する前に、本発明の実施形態に係るバルク金属汚染を除去する方法を用いて、半導体デバイスを製造するための方法を提供する。

(もっと読む)

電気絶縁材料の表面上の半導体層の厚さを減少しかつ均一化する方法

【課題】費用のかかる付加的露光装置を必要とせずに、SOIウェハの半導体層を均一化する方法を提供すること

【解決手段】電気絶縁性材料の表面上に存在する半導体層の厚さを減少しかつ均一化する方法において、半導体層の表面をエッチャントの作用にさらし、その酸化還元ポテンシャルを前記材料及び前記半導体層の所望の最終厚さの関数として調節して、前記半導体層の表面の単位時間当たりのエッチャントによる材料浸食を半導体層の厚さの減少と共に低下させ、かつ前記材料浸食は所望の最終厚さに達した場合に1秒当たり前記の厚さの0〜10%だけとなるようにし、その際、前記方法を光の作用なしで又は外部電圧の印加なしで実施する、半導体層の厚さを減少しかつ均一化する方法

(もっと読む)

半導体素子の製造方法

【課題】 InP基板、GaAs基板などの化合物半導体ウエハーの上に薄膜をエピタキシャル成長させたエピタキシャルウエハーを、デバイスを作製するためのプロセス工程で処理するとウエハーが30%〜40%の高率で割れる。プロセス工程でのエピウエハーの割れを防止すること。

【解決手段】 エピタキシャルウエハーの外周部を除去し、外周の面取り部にできた異常成長隆起部を取り除く。エピタキシャルウエハーの厚みをtとして、エピタキシャル層を周辺部からq=t〜5tの幅で除去し、基板の表面を露呈するようにする。

(もっと読む)

金属拡散接合による発光ダイオード及びその製造法

【課題】製品の信頼性と高性能を増進することを可能にする金属拡散接合による発光ダイオード及びその製造法を提供する。

【解決手段】第二導電型電極32の上に形成される第二導電型永久性基板30と、永久性基板30の上に形成されるオーム接触金属層と、オーム接触金属層の上に形成される金属拡散接合層と、金属拡散接合層40の上に形成されるオーム接触面25と、オーム接触面25の上に形成され、その頂面が粗面化されたAlInGaP半導体エピタキシー層20と、オーム接触面25とAlInGaP半導体エピタキシー層20の底面との間の部分的な表面に配置される絶縁透明層24と、AlInGaP半導体エピタキシー層20の第一導電型の第一束縛層21の部分的な表面の上に形成され、かつ絶縁透明層24に対応する位置の上方に配置される第一導電型電極50と、を有する。

(もっと読む)

基板の表面処理方法およびIII−V族化合物半導体の製造方法

【課題】 III−V族化合物半導体からなる基板をストイキオメトリにし、エピタキシャル成長後の表面の微小荒れを抑制する基板の表面処理方法およびIII−V族化合物半導体の製造方法を提供する。

【解決手段】 III−V族化合物半導体からなる基板を準備する工程(S10)と、基板を、pHを2以上6.3以下の酸性に調整するとともに酸化剤を添加した洗浄液により洗浄する洗浄工程(S20)とを備える。

(もっと読む)

1 - 20 / 27

[ Back to top ]