Fターム[5F044EE20]の内容

ボンディング (23,044) | ボンディングパッド電極 (1,310) | 高集積度化したもの (45)

Fターム[5F044EE20]に分類される特許

1 - 20 / 45

パワー半導体モジュール

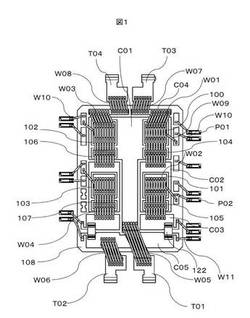

【課題】単一のパワー半導体モジュールに例えば12アームを搭載可能にコンパクトに実装するとともに、直流端子と交流端子のそれぞれの端子をモジュール端面にそれぞれ配置し、また、電力回路のインダクタンスを低く保つこと。

【解決手段】1枚の絶縁基板108上に2組の上アーム(100,104と102,106)を絶縁基板上の上寄り左右に配置し、2組の下アーム(101,105と103,107)を絶縁基板上の下寄り左右に配置して、絶縁基板上の配線パターンとして、2組の上アームを第1の配線パターンC01上に実装し、2組の下アームは第1の配線パターンの下に配置した第2、第3の配線パターンC02,C02上にそれぞれ実装して、第2、第3の配線パターンの間に第1の配線パターンC01を延長し、その延長した端部に正極端子T01からの配線を接続し、さらに、絶縁基板108を1モジュール中に3枚並置して実装して12in1モジュールの構成とすること。

(もっと読む)

半導体装置

【課題】信号伝送速度を高速化しても信頼性が高く、かつ、汎用的なリードフレームを利用可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、内側ワイヤボンディング20、内側ボンディング用端子100、配線110、外側ボンディング用端子120、外側ワイヤボンディング30を具備し、この順に、ボンディングパッド90からインナーリード60までを電気的に接続する信号伝送手段を有する。内側ボンディング用端子100、配線110、外側ボンディング用端子120は、絶縁性部材40上に形成されている。信号伝送手段は、ボンディングパッド90から前記アウターリード70の先端までの信号伝送路の距離が実質的に等しくなるように、配線110の配線長によって調整されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の組み立てにおけるボイドの発生を抑制する。

【解決手段】一対の第1辺3aa,3ab及び一対の第2辺3ac,3adを有する四角形からなるダイパッド3aにMCUチップ1とAFEチップ2を搭載し、MCUチップ1及びAFEチップ2にワイヤボンディングを行った後、2つの第2辺3ac,3adのうちの一方の第2辺3ac側から他方の第2辺3ad側に向かって樹脂を供給し、前記樹脂をMCUチップ1上の第1パッド群1ccと第2パッド群1cdとの間の開口に通してチップ間を充填することで、チップ間の領域におけるボイドの発生を抑制する。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、オーバーハング部に対するワイヤボンディング不良を防ぐ半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、実ボンディング時におけるボンディングヘッドが接地基準位置をサーチする下降速度及び荷重と同じ下降速度及び荷重でもってボンディングヘッドをオーバーハング部のボンディングパッドに対して下降させて接触させ、接地基準位置を予め取得する。実ボンディングでは、半導体チップにおける下方の支持体から張り出したオーバーハング部に形成されたボンディングパッドに対する前記接地基準位置までボンディングヘッドを下降させて、ボンディングヘッドの先端でワイヤをボンディングパッドに押し付けて接合する。

(もっと読む)

半導体装置

【課題】ワイヤボンディングにおいて、隣接する電極パッド間でショートさせることなく、電極パッドを狭ピッチ化した半導体装置を提供する。

【解決手段】この半導体装置100は、複数の電極パッド(第一電極パッド420、第二電極パッド440)と、ボンディングワイヤ600と、を備える。また、ボンディングワイヤ600は、第一電極パッド420と第二電極パッド440にボンディングされている。このとき、隣接する第一電極パッド420と第二電極パッド440は、上面の高さが交互に異なるように形成されている。また、第一電極パッド420と第二電極パッド440との間の段差部のうち、側面の少なくとも表面は、絶縁膜(保護絶縁膜260または保護絶縁膜500)で形成されている。

(もっと読む)

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の小型化を図る。

【解決手段】半導体チップ5の複数の第1電極パッドaと配線基板2の複数の第1接続部3b1を、複数の第1ワイヤ10b1を介して電気的に接続する工程と、第2電極パッドbと前記配線基板の複数の第2接続部3b2を、第2ワイヤ10b2を介して電気的に接続する工程と、第3電極パッドcと前記配線基板の複数の第3接続部3b3を、第3ワイヤ10b3を介して電気的に接続する工程とを有し、前記複数の第1ワイヤ10b1のそれぞれを前記複数の第1接続部3b1のそれぞれの前記第1部分に接続し、前記第3ワイヤ10b3を前記第3接続部3b3の前記第2部分に接続し、前記複数の第110b1、第210b2および第3ワイヤ10b3は、平面視において、前記半導体チップ5の前記第2辺の中心部を経由し、かつ前記第2辺と直交する仮想線5sに対して鋭角をなす角度で、前記複数の電極パッドから延在させる。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体基板1上に積層された複数の層間絶縁膜16、19、22と、複数の層間絶縁膜16、19、22の最上面の上に形成され、外部からプローブが当てられるプローブ接触領域を有するパッド25と、複数の層間絶縁膜16、19、22の間に形成される複数層の配線12,15、18と、パッド25のプローブ接触領域の直下の領域に形成され、前記層間絶縁膜22が充填される非直線状スリットか孔の少なくとも一方を有する導電性パターンを有する応力緩和部42とを有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路におけるパッドの配置の自由度を増加させること。

【解決手段】本発明の一態様に係る半導体集積回路は、半導体チップ100に形成されたI/Oバッファ102と、単層パッド103と、多層パッド104とを備える。単層パッド103は、I/Oバッファ102上に形成されている。多層パッド104は、I/Oバッファ102上に形成され、単層パッド103と分離して設けられている。単層パッド103はボンディング専用のパッドであり、多層パッド104はプロービングとボンディングが行われるパッドである。

(もっと読む)

半導体素子とそれを用いた半導体装置

【課題】半導体素子の実装方法の違いによるコストアップを抑制する。

【解決手段】半導体素子10は、集積回路を有する基板11と、集積回路に対して同じ接続機能を有する電極として、基板11の同一主面11a上に、ワイヤー接続用電極1b、2b、3b及び4b及びバンプ接続用電極1a、2a、3a及び4aを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数を増加させず、有機誘電体層上に形成された電極端子にワイヤボンディングできる半導体装置を提供する。

【解決手段】本発明に係る半導体装置10は、半導体基板11と、半導体基板11の上に形成される有機物で構成される有機誘電体層14と、有機誘電体層14の上に形成される電極端子15と、有機誘電体層14を貫き、電極端子15を支える支持体13とを備える。また、支持体13は電極端子15の直下に形成されてもよい。

(もっと読む)

半導体装置

【課題】多層の金属配線層を有する半導体装置において、より一層のパッド配置面積の低減を図る。

【解決手段】アルミ3と、アルミ3との間に層間絶縁膜を介して設けられたアルミ2と、アルミ2,3間を接続するコンタクトと、アルミ3に対応して設けられた保護膜の開口部1と、を備え、開口部1の内側領域が、外部電極用パッドであり、かつ、ボンディング領域とプローブテスト領域の二つに分けて使用される半導体装置である。前記ボンディング領域では、アルミ3が露出され、該アルミ3によりアルミ2が隠れている。前記プローブテスト領域では、アルミ2が露出されている。

(もっと読む)

半導体装置とその製造方法

【課題】バンプを有するパッド電極の下方の領域の有効活用を図り、また実装時においてバンプの下方の半導体基板に局所的に大きな力が加わることを防止するために、パッド電極上に突起電極を有した半導体装置とその製造方法を提供する。

【解決手段】半導体基板上に形成された1層目メタル配線5と、1層目メタル配線5上に層間絶縁膜を介して形成され、層間絶縁膜に形成されたビアホール10を通して1層目メタル配線5と接続されたパッド電極7が設けられている。また、パッド電極7上に形成され、パッド電極7を露出する1つの開口部と、開口部の中に島状保護膜9とを有する保護膜8と、パッド電極7上に形成され、保護膜8の開口部を通してパッド電極7に接続されたAuバンプ11が設けられている。そして、ビアホール10は島状保護膜9の下方に形成され、かつビアホール10に、パッド電極7の一部が不完全に埋め込まれている。

(もっと読む)

半導体装置

【課題】 半導体装置が機能するのに必要な半導体構造を製造できる有効領域を拡大する技術を提供する。

【解決方法】 本発明の半導体装置2では、その表面に形成されるパッド12の少なくとも一部が、半導体基板4の表面の外周の内側を一巡する耐圧保持部65上に形成されている。従来技術では耐圧保持部65の内側に形成されていたパッド12の少なくとも一部を耐圧保持部65上に形成することで、耐圧保持部65の内側のパッド領域10の面積を縮小することができる。これにより、耐圧保持部65の内側で半導体装置2が機能するのに必要な半導体構造を製造できる有効領域8を拡大することができる。また、パッド12と耐圧保持部65の間に導電膜を含む積層構造20を形成することで、耐圧保持部65に局所的な電界が印加されることがない。半導体装置2の耐圧特性が悪化することを防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】外部接続用のパッドが形成される表層より一層下の配線層の配線密度を下げることなく、パッド下の層間絶縁膜のクラックを防止できる半導体装置を提供する。

【解決手段】表層より一層下の層に形成された配線のうち、パッド1の領域下を通過する配線3aの厚さを、パッド1の領域下から外れて配置される配線3bの厚さよりも薄くする。

(もっと読む)

ワイヤボンディング方法およびワイヤボンディング構造体

【課題】半導体チップ上の電極と基板上の電極との間で複数本のワイヤを接続する場合に、1組の電極間にて複数本のワイヤを重ねるにあたって適切なワイヤ形状を形成できるようにする。

【解決手段】半導体チップ10の電極11と基板20の電極21との間でワイヤ接続工程を複数回行って両電極11、21上にワイヤ30を複数本重ねて形成するものであって、重ねられた複数本のワイヤ30のうち最上部に位置するワイヤ30よりも下側に位置するワイヤ30を形成する接続工程では、1次ボンディング後のワイヤ30の引き出しを、当該ワイヤ30における1次ボンディング部30a側の根元部から中間部までが2次ボンディング側のランド21に向かって水平面Hから斜め上方の方向に延びる形状となるように行う。

(もっと読む)

半導体装置とワイヤボンディング方法

【課題】 半導体装置が機能するのに必要な半導体構造を製造できる有効面積を拡大する技術を提供する。

【解決方法】 本発明の半導体装置2では、活性領域4に第1ボンディングパッド24が形成されていると共に、不活性領域6に第2ボンディングパッド26が形成されている。本発明の半導体装置2では、外部回路と半導体装置2を、第1ボンディングパッド24を用いて接続する場合、一旦を外部回路とボンディングしたワイヤ14を第1ボンディングパッド24でボンディングする。さらにそのワイヤ14を、第1ボンディングパッド24で切断しないで第2ボンディングパッド26にボンディングする。第1ボンディングパッド24でワイヤ14を切断しないので、第1ボンディングパッド24の面積を縮小することがでる。これにより、半導体構造を製造できる有効面積である半導体領域8を拡大することができる。

(もっと読む)

ボンディング用のパッド及び電子機器

【課題】AuワイヤがワイヤボンディングされたAlパッドは、経時変化によりワイヤ接合部のAu−Al合金化領域が拡大し、隣接するパッドに接触して短絡するおそれがある。

【解決手段】互いに隣接するパッド1の対向する辺のうち、ワイヤ接合部5に最も近い部分を含む凹部形成領域4aに、パッド1の辺が凹になるように凹部4を形成する。凹部4ではパッド1からのAlの供給が途絶えるため、合金化速度が遅くなる。このため、最も短絡を生じやすい凹部近傍で合金化領域11の拡大が抑制されるので、隣接するパッド1との短絡が遅延する。

(もっと読む)

半導体チップおよび半導体チップの製造方法

【課題】SiONx膜系のパッシベーション膜21とポリイミド膜22の2層構造からなる保護膜20を有する半導体チップにおいて、アセンブリ時にアセンブリ冶工具が保護膜20と干渉せず、耐湿信頼性の低下を起こさない半導体チップを得ること。

【解決手段】半導体基板上にトランジスタを含む電子部品が形成された半導体基材10の最上層の層間絶縁膜11に形成された電極パッド12と、層間絶縁膜11上の全面と電極パッド12の周縁部を覆い、電極パッド12の中心部が開口した第1の開口領域31を有するパッシベーション膜21と、パッシベーション膜21上の全面に形成されるポリイミド膜22と、を備え、ポリイミド膜22は、電極パッド12の形成位置に対応する位置に第2の開口領域32を有し、第2の開口領域32は、ポリイミド膜22の上面から所定の深さまでの領域では、第1の開口領域31よりも広い。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下の層間絶縁膜にクラックが入るのを防ぎ、ボンディングパッドと同層に形成された上層配線を微細化することができる半導体装置及びその製造方法を提供する。

【解決手段】層間絶縁膜17上に第1金属膜20を形成する。第1レジストをマスクとして第1金属膜20を異方性エッチングする。残された第1金属膜20を覆うように層間絶縁膜17上に、第1金属膜20よりもヤング率が低い第2金属膜24を形成する。層間絶縁膜17上に第1金属膜20が存在する領域及び第1金属膜20が存在しない領域の一部において第2金属膜24上に第2レジストを形成する。第2レジスト33をマスクとして第2金属膜24を異方性エッチングして、第1金属膜20と第2金属膜24とを有するボンディングパッドと、第2金属膜24を有するが第1金属膜20を有しない上層配線22とを形成する。

(もっと読む)

1 - 20 / 45

[ Back to top ]