Fターム[5F044LL15]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 接触によるもの (125)

Fターム[5F044LL15]に分類される特許

121 - 125 / 125

チップ状電子部品、その製造方法及び実装構造

【課題】 外部接続端子を効率良く配置し、高周波特性を維持でき、小型化が可能なチップ状電子部品、その製造方法及び実装構造を提供すること。

【解決手段】半導体チップ101の電極パッド113と、フリップチップ接続端子108と、外部接続端子104とを有し、半導体チップ101の電極パッド113がフリップチップ接続端子108にフリップチップ接続され、フリップチップ接続端子108と外部接続端子104とが金属ワイヤー103によって電気的に接続されている半導体パッケージ109。

(もっと読む)

半導体装置およびその製造方法

【課題】金等のバンプ電極を用いた狭ピッチな微細フリップチップ接続を低コストかつ高信頼に達成すること。

【解決手段】配線が形成された基板と、前記基板上に配置され、半導体回路、及び前記半導体回路に電気的に連絡する複数の外部端子が形成された第一の半導体素子と、前記第一の半導体素子は、前記外部端子を介して前記配線に電気的に連絡され、前記第一の半導体素子と前記基板との間に形成され、前記外部端子の周囲に充填された接着材と、を備え、前記基板表面から前記半導体素子の前記外部端子が形成され主面の反対側の主面までの厚さは、前記外部端子の位置する領域の方がその周囲より厚くなるよう形成されている領域を有する。

【効果】バンプ電極の塑性変形を抑制し,温度変化や外力に対して高信頼性接続を低コストなプロセスで達成できる。

(もっと読む)

イメージセンサモジュール及びその製造方法

【課題】 軽薄化、小型化を達成しつつ、高い信頼性を持つCOG(Chip On Glass)CMOSイメージセンサモジュール及びその製造方法を提供する。

【解決手段】 透明媒質18の対面に一定パターンのメッキを形成するステップと、メッキパターンが形成された透明媒質の対面にイメージセンサチップのパターン部及びフレキシブルPCB16と電気的に接続する1次及び2次金バンプ13,14を形成するステップと、1次金バンプとイメージチップのパターンを電気的に接続するようにボンディングする1次ボンディングステップと、フレキシブルPCBのパターン部と第2ステップを通じて形成された2次金バンプを電気的に接続するように超音波と熱を利用してボンディングする2次ボンディングステップと、フレキシブルPCBにイメージチップが実装された後面を、エポキシ樹脂19を利用してモールディングするステップとを含む。

(もっと読む)

LSIパッケ−ジ及びそれに用いる内部接続工法

【課題】 ベアチップへのはんだバンプ形成・インタポ−ザへの実装という製造工程を不要とするLSIパッケージを提供する。

【解決手段】 ベアチップ4に設けられたベアチップI/O(入出力)端子3に接続する配線パタ−ン6を基板1のビルドアップ層2に形成し、ベアチップ4をLSIパッケージに実装する。その際、配線パタ−ン6は基板1の外部I/O端子7に接続するように形成される。

(もっと読む)

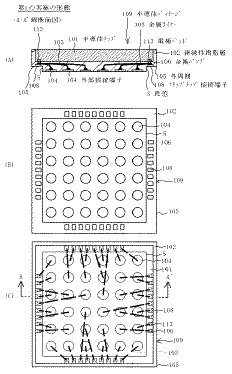

半導体チップの実装構造

【課題】 半導体チップを配線基板にワンタッチで実装したり実装し直したりできる半導体チップの実装構造を得る。

【解決手段】 半導体チップの接続端子12に突起20を設ける。配線基板30の絶縁基板32には、突起20を遊嵌する穴40を設けて、絶縁基板32表面に備えた導体回路50の一端に設けた板状の導体リング52の内側周縁を穴40の開口部上端に庇状に突出させる。そして、半導体チップの突起20の中途部を、導体リング52の弾性に抗して、導体リング52の内側に挿抜可能に押入、係止できるようにする。それと共に、半導体チップの突起20の下部を、絶縁基板の穴40に遊嵌できるようにする。そして、半導体チップ10を配線基板30に実装できるようにする。

(もっと読む)

121 - 125 / 125

[ Back to top ]