Fターム[5F045DA66]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の物性 (649) | 抵抗値 (59)

Fターム[5F045DA66]に分類される特許

1 - 20 / 59

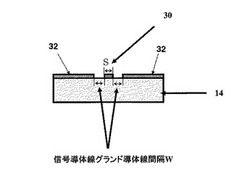

炭化珪素基板、半導体装置及び配線基板

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】オートドープを抑制して、均一な抵抗分布を有するシリコンエピタキシャルウェーハを効率的に製造できる方法を提供することを目的とする。

【解決手段】シリコン単結晶基板上にシリコン単結晶をエピタキシャル成長させて、エピタキシャル層を積層するシリコンエピタキシャルウェーハの製造方法において、抵抗率が0.5mΩ・cm以上20.0mΩ・cm以下で、ボロンがドープされている前記シリコン単結晶基板上に、成長速度を5μm/分以上15μm/分以下として、抵抗率が0.5Ω・cm以上2000Ω・cm以下である前記エピタキシャル層を成長させるシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リーク電流が増加することなく、オン抵抗を低くすることができる半導体装置を提供する。

【解決手段】基板の上に形成されたバッファ層21と、バッファ層21の上に形成された遷移金属がドープされている高抵抗層22と、高抵抗層22の一部または高抵抗層上に形成された低抵抗となる不純物元素がドープされた低抵抗領域122と、低抵抗領域122を含む領域上に形成された電子走行層23と、電子走行層23の上に形成された電子供給層25と、電子供給層25の上に形成されたゲート電極31、ソース電極32及びドレイン電極33を有する。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

p型化合物半導体層の形成方法

【課題】p型化合物半導体層の形成の際に、p型不純物と水素の結合を遮断するp型化合物半導体層の形成方法を、提供する。

【解決手段】

p型化合物半導体層の形成方法が開示される。この方法では、反応チェンバ内に、III族元素のソースガス、p型不純物のソースガス、及び水素を含有する窒素のソースガスを供給し、p型化合物半導体層を成長させる。また、p型化合物半導体層の成長が完了した後、III族元素のソースガス及びp型不純物のソースガスの供給を中断し、基板の温度が400〜900℃である間に、水素を含有する窒素のソースガスの供給を中断及び排出し、冷却ガスで常温まで冷却させる。これにより、基板の温度を冷却させる過程で、p型化合物半導体層に含まれたp型不純物に水素が結合することを防ぐことができる。

(もっと読む)

窒化物半導体装置の製造方法

【課題】高抵抗バッファ層の結晶品質の劣化を避けることができる窒化物半導体装置の製造方法を得る。

【解決手段】SiC基板1上に、III族原料として有機金属原料を用い、V族原料としてヒドラジン誘導体の有機化合物を用いたMOCVD法により、炭素濃度が1018cm−3以上に制御された窒化物半導体からなるAlN高抵抗バッファ層2を形成する。AlN高抵抗バッファ層2上に、AlN高抵抗バッファ層2よりも低い抵抗値を持つGaN電子走行層3とAl0.2Ga0.8N電子供給層4を形成する。

(もっと読む)

半絶縁性窒化物半導体ウエハ、半絶縁性窒化物半導体自立基板及びトランジスタ、並びに半絶縁性窒化物半導体層の成長方法及び成長装置

【課題】高い抵抗率(例えば、1×105Ωcm以上、1×1012Ωcm以下)、良好な抵抗率の均一性(例えば、ウエハ表面積の80%に相当するウエハ内周側の位置での抵抗率のバラツキが±30%以下)、及び良好な結晶性(例えば、X線(004)回折の半値幅が30〜300秒)を有する半絶縁性窒化物半導体ウエハ、半絶縁性窒化物半導体自立基板及びトランジスタ、並びに半絶縁性窒化物半導体層の成長方法及び成長装置を提供する。

【解決手段】窒化物半導体層の成長方法は、基板上にIII族原料GaClを連続的又は断続的に供給するとともに、窒素原料NH3と半絶縁性を付与する半絶縁性ドーパント原料Cp2Feとを交互に供給して基板上に半絶縁性窒化物半導体層を成長させる。

(もっと読む)

材料層を堆積するための装置および方法

【課題】プロセスガスから発生する材料層を基板ウェハ上に堆積するための装置および方法を提供する。

【解決手段】プロセスガスから発生する材料層を基板ウェハ上に堆積するための装置は、上方ドームと下方ドームと側壁とによって画定されるリアクタチャンバと、材料層の堆積の際に基板ウェハを保持するためのサセプタと、サセプタを取囲む予熱リングと、ライナーとを備え、その上に、予熱リングが、均一幅の隙間が予熱リングとサセプタとの間に存在するように中央位置に支持され、さらにライナーと予熱リングとの間に作用するスペーサを備え、当該スペーサは、予熱リングを中央位置に保ち、かつ予熱リングとライナーとの間に距離Δを発生する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】 エピタキシャル成長中における基板からエピタキシャル層へのオートドープ量を抑制し、抵抗分布及び膜厚分布の良好なエピタキシャルウェーハを得ることができるシリコンエピタキシャルウェーハの製造方法を提供することを目的とする。

【解決手段】 シリコン単結晶基板上にシリコン単結晶をエピタキシャル成長させて、エピタキシャル層を積層するシリコンエピタキシャルウェーハの製造方法において、抵抗率が0.5mΩ・cm以上10.0mΩ・cm以下であり、リンまたはヒ素がドープされている前記シリコン単結晶基板上に、成長速度を3μm/分以上15μm/分以下として、抵抗率が0.5Ω・cm以上2000Ω・cm以下である前記エピタキシャル層を成長させることを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

III族窒化物半導体光素子、III族窒化物半導体光素子を形成する方法、III族窒化物半導体膜を成長する方法及びエピタキシャル基板

【課題】p型III族窒化物半導体の電気特性を向上できるIII族窒化物半導体光素子を提供する。

【解決手段】窒化ガリウム系半導体領域15及び窒化ガリウム系半導体領域19は、基板13の主面13a上に設けられる。窒化ガリウム系半導体領域19は、p型ドーパントとしてマグネシウムを含むIII族窒化物半導体膜21を有しており、III族窒化物半導体膜21は、III族構成元素としてアルミニウムを含む。III族窒化物半導体膜21の酸素濃度は、1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の酸素濃度は、1.5×1018cm−3以下の範囲にある。また、III族窒化物半導体膜21の水素濃度は1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の水素濃度は1.5×1018cm−3以下の範囲にある。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】オン抵抗やリーク電流を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板上に、少なくとも、GaAs層、AlGaAs層からなるバッファ層、InGaAs層からなるチャネル層、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層、ノンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層、Se又はTeをドーパントとしたn型不純物を含有するInxGa(1-x)As層(但し0<x<1)からなるコンタクト層を積層したHEMT構造を有するIII−V族化合物半導体エピタキシャルウェハにおいて、その表面清浄度検査におけるHaze値が500ppm以下であるものである。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】コンタクト層に不純物として供給するTe、Seのメモリーの影響を小さくしつつ、コンタクト抵抗を低減し、かつ、特性変動や信頼性低下を抑制しつつ、電子供給層の不純物濃度を高め、オン抵抗を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板11上に、GaAs層、AlGaAs層からなるバッファ層12a,12b、n型不純物を含有するAlGaAs層13,17又はInGaP層若しくはSiプレナードープ層からなる電子供給層、InxGa(1-x)As層からなるチャネル層15、アンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層18、n型不純物を含有するInxGa(1-x)As層からなるコンタクト層20a、20bを積層したHEMT構造を有し、チャネル層のxを0.3≦x≦0.35とし、コンタクト層のxを0.55≦x≦0.60としたものである。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法

【課題】面内にわたって表面抵抗率を均一化し、得られるHEMT素子の製品抵抗のバラツキを低減した化合物半導体エピタキシャルウェハ及びその製造方法を提供する。

【解決手段】GaAsからなる基板1上に、少なくともAlGaAsからなるバッファ層3、AlGaAsからなる下部電子供給層4、GaAsもしくはInGaAsからなる電子走行層5、AlGaAsからなる上部電子供給層6、AlGaAsからなるショットキー層7、及びn型不純物を含有するGaAsからなるオーミックコンタクト層8が順次形成された化合物半導体エピタキシャルウェハ10において、オーミックコンタクト層8の外周部のキャリア濃度を中心部のキャリア濃度より高くしたものである。

(もっと読む)

半導体発光装置

【課題】半導体膜内部における電流拡散を阻害することなく半導体膜内部を伝搬する光の自己吸収を抑制することができる半導体発光装置を提供すること。

【解決手段】支持体上の反射電極と、反射電極上の第1クラッド層と、第1クラッド層上の発光層と、発光層の上に設けられ、凹部及び凸部からなるテラス構造を有し、凸部の頂面及び凹部の底面に凹凸形状の光取り出し構造が形成された第2クラッド層と、凸部の頂面上の表面電極と、を有し、第2クラッド層は、発光層上に、第1電流拡散層、第1電流拡散層上に設けられ凹部の底面の光取り出し構造を備える第1光取り出し層、第1光取り出し層上に設けられた第2電流拡散層、及び第2電流拡散層上に設けられ凸部の頂面の光取り出し構造を備える第2光取り出し層を含む積層構造を有し、第1光取り出し層及び第2光取出し層は、第1電流拡散層及び第2電流拡散層よりも小なる光吸収率と、第1電流拡散層及び第2電流拡散層よりも大なる抵抗値と、を有すること。

(もっと読む)

半導体膜の作製方法、半導体装置の作製方法、及び光電変換装置の作製方法

【課題】抵抗率の低い不純物元素を有する非晶質半導体を形成する。また、電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】プラズマCVD法により不純物元素を有する非晶質半導体を形成する方法において、パッシェンの法則で最小放電開始電圧を満たす圧力及び電極間隔において、パルス変調した放電開始電圧を電極に印加することより、抵抗率の低い不純物元素を有する非晶質半導体を形成する。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】高耐圧化した窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置200は、シリコン基板201上に形成されたバッファ層220と、バッファ層220上に形成された第1の窒化物超格子層204aと、第1の窒化物超格子層204a上に形成された活性領域層230とを備え、バッファ層220は、不純物がドープされた第2の窒化物超格子層204bと、第2の窒化物超格子層204b上に形成され、不純物がドープされた第1の窒化物半導体層205と、第1の窒化物半導体層205上に形成され、第1の窒化物半導体層205よりもAl組成及び不純物の濃度が高い第2の窒化物半導体層206とを有する。

(もっと読む)

薄膜の形成方法及び成膜装置

【課題】比較的低温でも埋め込み特性が良好なアモルファス状態の不純物含有のシリコン膜を形成することが可能な薄膜の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器14内で被処理体Wの表面に不純物含有のシリコン膜を形成する薄膜の形成方法において、処理容器内へシリコンと水素とよりなるシラン系ガスを該シラン系ガスが被処理体の表面に吸着するような状態で供給する第1のガス供給工程と処理容器内へ不純物含有ガスを供給する第2のガス供給工程とを交互に繰り返し行うことによりアモルファス状態で不純物含有のシリコン膜を形成する。これにより、比較的低温でも埋め込み特性が良好なアモルファス状態の不純物含有のシリコン膜を形成する。

(もっと読む)

光半導体装置の製造方法

【課題】 素子容量を抑制しつつリーク電流を抑制することができる光半導体装置の製造方法を提供する。

【解決手段】 光半導体装置の製造方法は、基板上に順に形成されたn型クラッド層、活性層、およびp型クラッド層に対して選択的にエッチング処理を施すことによってメサ構造を形成する工程と、前記メサ構造の側面から前記基板の前記メサ構造以外の平面部にかけて、前記平面部における厚さが5nm〜45nmのp型半導体層を形成する工程と、前記p型半導体層上に、前記メサ構造を埋め込む高抵抗半導体層を形成する工程と、を含み、前記平面部において、前記p型半導体層の厚みと前記p型半導体層のp型ドーパントの濃度との積は、2.5×1019nm/cm3以下である。

(もっと読む)

β−Ga2O3単結晶

【課題】バンドギャップがより大きく、紫外領域で発光する可能性があるβ−Ga2O3単結晶において、所定の抵抗率及びキャリア濃度を有するβ−Ga2O3単結晶を提供する。

【解決手段】β−Ga2O3単結晶において、Si濃度を1×10−5〜1mol%に変化させることにより、抵抗率が2.0×10−3〜8×102Ωcm、キャリア濃度が5.5×1015〜2.0×1019/cm3の範囲に制御するドーパントの添加濃度に応じて抵抗率を可変することができる。

(もっと読む)

1 - 20 / 59

[ Back to top ]