Fターム[5F045DB05]の内容

気相成長(金属層を除く) (114,827) | 半導体層の選択成長 (353) | 絶縁体マスク (266) | 埋込エピ層の形成 (22)

Fターム[5F045DB05]に分類される特許

1 - 20 / 22

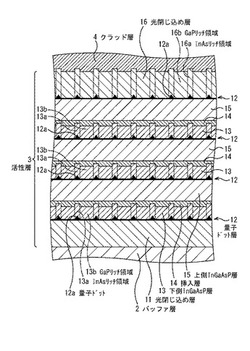

光半導体素子及びその製造方法

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

(もっと読む)

半導体レーザ及びその製造方法

【課題】半導体レーザ(ストライプ状の活性層)が高密度に配置された半導体レーザを提供すること。

【解決手段】互いに離間してストライプ状に設けられた、複数の活性層10と、活性層10のそれぞれに対応して、活性層10の上側に設けられた複数の電極12と、半導体からなり、活性層10の間の領域にそれぞれに設けられ、電極12よりも高い位置にその上面が位置する支持部40と、複数の電極12のうち1つと電気的に接続されるとともに、複数の支持部40によって支えられて、当該複数の支持部40の間に位置する電極12と離間した構造を備える配線16と、を備えることを特徴とする半導体レーザ。

(もっと読む)

発光ダイオード

【課題】格子欠陥が発生することを防止した発光ダイオードを提供する。

【解決手段】発光ダイオード10は、基板100と、第一半導体層120と、第二半導体層140と、活性層130と、第一電極150と、第二電極160と、を含む。第一半導体層、活性層、及び第二半導体層は、基板から離れる方向に沿って、基板に順次的に積層され、第一電極は、第一半導体層に電気的に接続され、第二電極は、第二半導体層に電気的に接続され、第一半導体層の基板と隣接する表面は、複数の空隙を含むパターン化されたカーボンナノチューブ層102である。第一半導体層のパターン化された表面が基板に接続することによって複数のキャビティが形成される。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】結晶欠陥の少ない高品質な単結晶炭化シリコン膜を形成することが可能な半導体基板及び半導体基板の製造方法を提供する。

【解決手段】単結晶シリコン11と、単結晶シリコン11の表面に形成された、開口部12hを有するマスク材12と、単結晶シリコン11の開口部12hから露出した部分に形成された炭化シリコン膜13と、炭化シリコン膜13及びマスク材12を覆って形成された単結晶炭化シリコン膜14と、を含み、マスク材12の粘度が950℃以上1400℃以下の温度範囲において105Pa・s以上1014.5Pa・s以下である。

(もっと読む)

窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置

【課題】窒化物半導体積層体の結晶欠陥密度が低減可能な窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置を提供する。

【解決手段】窒化物半導体の積層構造は、基板10、第1バッファ層12、第1結晶層14、第2バッファ層16、第2結晶層20とを備える。基板10には、段差部10dが形成されている。第1バッファ層12は、InAlGaNを含み、段差下面10bと段差側面10cとを覆う。第1結晶層14は、前記第1バッファ層12の上に設けられ、InAlGaNを含み、前記基板10の上面10aよりも上方に設けられた上面14aを有する。第2バッファ層16は、InAlGaNを含み、前記第1結晶層14の前記上面14aと前記基板10の前記上面10aとを連続して覆う。第2結晶層20は、前記第2バッファ層16を覆い、InAlGaNを含み、前記第1の面20aを有する。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置する第二ステップと、前記基板の結晶面にエピタキシャル層を成長させる第三ステップと、を含む。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】空隙の発生を抑制しつつ、迅速に開口を埋め込むことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】Siからなる金属膜202上に絶縁膜204が形成されたウエハ12であって、絶縁膜204の一部に開口部206が形成されこの開口部206に金属膜202が露出したウエハ12を処理室106内へ搬送し処理室106内へ少なくともDCSとCl2とを供給してウエハ12の金属膜202上に選択的に第1のSi膜252を形成し、処理室106内へ少なくともDCSを供給してウエハ12の絶縁膜204及び第1のSi膜252上に第2のSi膜254を形成する。

(もっと読む)

窒化ガリウム系エピタキシャル成長基板及びその製造方法並びにこの基板を用いて製造される電界効果型トランジスタ

【課題】Si基板内に形成される低抵抗層の抵抗率が、このGaN系エピタキシャル成長基板を利用して形成されるFETの動作特性に影響を与えることがない程度の大きさに形成されている。

【解決手段】Si基板10の主面とバッファ層60-1との間にストライプ状絶縁膜26が形成されている。このストライプ状絶縁膜が形成されていることによって、Si基板内に形成される低抵抗層11の抵抗率がこのGaN系エピタキシャル成長基板を利用して形成されるFETの動作特性に影響を与えることがない程度の大きさにすることが可能となるという効果が得られる。

(もっと読む)

光−電子デバイス

本発明は、電子デバイス用の、好ましくは、光電子デバイス用の、電流遮断構造を提供する。電流遮断構造が、n−型ルテニウムドープリン化インジウム(Ru−InP)層を備えた半導体材料配列と、第1p−型半導体材料層と、を備え、n−型Ru−InP層が、0.6μm未満の厚さである。半導体材料配列と、p−型半導体材料層と、が、電流遮断p−n接合を形成する。電流遮断構造が、他のn−型層および/または多数のn−型Ru−InP層および/または真性/ドープされていない層をさらに備えてよく、n−型Ru−InP層が、0.6μmよりも厚くてよい。  (もっと読む)

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

発光ダイオードの製造方法

発光ダイオードの製造方法であって、シリコン表面(1a)を有するキャリア基板(1)を形成するステップと、シリコン表面(1a)上に、成長方向(R)に一連の層(100)を堆積させるステップと、一連の層(100)上に発光ダイオード構造(16)を堆積させるステップと、を含んでおり、一連の層(100)が、窒化ガリウムを使用して形成されるGaN層(5)を含んでおり、一連の層が、窒化珪素を使用して形成されるマスキング層(12)を含んでおり、成長方向(R)においてGaN層(5)の少なくとも一部分の後ろにマスキング層(12)が続いている、方法、を提供する。 (もっと読む)

ヘテロ構造の製造方法

【課題】微細孔内にヘテロ構造を形成することができるヘテロ構造の製造方法を提供する。

【解決手段】基板1上にナノサイズの金属微粒子を形成し、次いで、該金属微粒子上に第一の物質をVLS成長法により選択的に成長させることによりナノワイヤである柱状構造を形成し、引き続き、前記柱状構造の高さよりも下まで前記基板1上に第二の物質4を充填した後、前記第一の物質と前記第二の物質4の反応性の違いを利用した選択エッチングにより前記第一の物質である柱状構造を除去して、微細孔4aを形成し、微細孔4a内に、前記第一の物質を成長させた温度より高い温度で、ヘテロ構造の結晶(7、8、9)を成長させる。

(もっと読む)

半導体基板、半導体装置及び半導体基板の製造方法

【課題】所望の電気的特性を得やすい半導体基板、半導体装置及び半導体基板の製造方法を提供すること。

【解決手段】半導体基板の製造方法は、第1エピタキシャル層を形成する第1エピタキシャル層形成工程S1と、第1エピタキシャル層にトレンチを形成するトレンチ形成工程S2と、第1エピタキシャル層及びトレンチ内にエピタキシャル層を、異なる成長速度を含む複数の成長条件を用いて、トレンチ内を埋めるように形成し、複数の成長条件のそれぞれにおいてエピタキシャル層に取り込まれるドーパント濃度を一定にするエピタキシャル層形成工程S3、S4、S5と備える。

(もっと読む)

半導体素子の製造方法

【課題】成長用基板の剥離をウェットエッチング処理によって容易に行うことができ、更に、光取り出し効率向上と半導体膜の機械的強度の確保を両立させた半導体素子の製造方法を提供する。

【解決手段】

複数の第1の空洞を含む第1空洞含有層を成長用基板上に形成する工程と、複数の第2の空洞を含み、互いに隣接する第2の空洞間の隔壁部の各々が第1の空洞の各々の上部に設けられた第2空洞含有層を第1空洞含有層上に形成する工程と、第2空洞含有層上に半導体層をエピタキシャル成長させる工程と、半導体層上に支持基板を接着する工程と、第1および第2の空洞の各々にエッチャントを流入させて、第1の空洞の各々と第2の空洞の各々とを結合させて成長用基板を半導体層から除去する工程と、を含む。

(もっと読む)

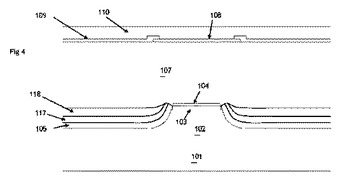

半導体素子の製造方法

【課題】成長用基板上に選択成長用のマスクを配した後、横方向成長法を用いて半導体層を形成する工程を含む半導体発光装置の製造方法において、従来よりも成長過程の早い段階で平坦な膜を得ることができる半導体素子の製造方法を提供する。

【解決手段】

成長用基板上を部分的に覆う選択成長用のマスクを成長用基板上に形成する。次に、成長用基板上のマスクで覆われていない非マスク部から半導体膜を横方向成長させてマスクを覆う貫通転位遮断層を形成する。次に、貫通転位遮断層の上に発光層を含むデバイス機能層をエピタキシャル成長させる。貫通転位遮断層を形成する工程は、常圧且つデバイス機能層の成長温度よりも低い温度雰囲気の下、互いに異なる成長速度で半導体膜の成長を行う第1ステップおよび第2ステップを交互に複数回実施する。

(もっと読む)

窒化物系半導体発光素子

【課題】光の外部取り出し効率を向上させ、かつ素子の駆動電圧を低減させることのできる窒化物系半導体発光素子を提供する。

【解決手段】支持基板上に形成された反射層と、反射層上方に順次積層されたp型窒化物系半導体層、発光層およびn型窒化物系半導体層とを含む窒化物系半導体発光素子であって、n型窒化物系半導体層上方に位置する光取り出し面に凹凸が形成されており、凹凸は、成長用基板上にn型窒化物系半導体層、発光層およびp型窒化物系半導体層を成長した後に成長用基板を除去したn型窒化物系半導体層面上にn型窒化物系半導体層と同じ結晶からなる凹凸を設けることにより形成された窒化物系半導体発光素子である。

(もっと読む)

光半導体素子及びその製造方法

【課題】 Ruドーピング半絶縁半導体層を用いた埋め込み型光半導体素子の実用化のため、水素の大量に存在する成長環境下においても、より絶縁性の高いRuドーピング半絶縁半導体層を再現よく、容易に形成する。

【解決手段】 Ruドーピング半絶縁半導体層の成長時に、化合物半導体の原料ガス、キャリアガスとは別に、ハロゲン原子を含有するガスを水素と同時に添加することで、Ruと水素との結合を抑制することで実現する。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、回折格子の形状が製造工程中に変化せず所望の形状とすることができる半導体素子の製造方法を提供することを目的とする。

【解決手段】基板上に光ガイド層を形成する工程と、該光ガイド層上にキャップ層を形成する工程と、該光ガイド層の一部が該回折格子を形成するように該光ガイド層と該キャップ層の一部に開口部を形成する工程とを備える。そして更に該基板を該キャップ層の成長温度未満かつ該キャップ層のマストランスポートが起こる温度以上に昇温し、該開口部において露出している該光ガイド層の側面を該キャップ層の一部で覆うマストランスポート工程と、該マストランスポート工程後に該基板上に該回折格子の埋め込み層を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体レーザ装置の製造方法

【課題】埋め込み再成長型の端面窓構造を形成する工程における不純物の拡散を抑制して、半導体レーザの出力特性の向上、及び出射端面の劣化を回避する。

【解決手段】基板11の上に第1クラッド層12、第1光ガイド層13、活性層14、第2光ガイド層15、及び第2クラッド層16を含む積層構造を結晶成長させる工程と、積層構造の一部をエッチングにより除去して開口部を形成する工程と、開口部に活性層より禁制帯幅が大きな材料からなる結晶を埋め込み成長させて埋め込み成長部19bを形成する工程と、光導波路を形成する工程と、埋め込み成長部をへき開面が通るようにへき開することにより、出射端面を形成する工程とを含む。埋め込み成長部を形成する工程において、結晶の成長を、開口部の側壁面から進行し、且つ開口部を除く領域の表面から進行し難い条件により行う。

(もっと読む)

1 - 20 / 22

[ Back to top ]