Fターム[5F045DB06]の内容

気相成長(金属層を除く) (114,827) | 半導体層の選択成長 (353) | 絶縁体以外のマスク (35)

Fターム[5F045DB06]に分類される特許

1 - 20 / 35

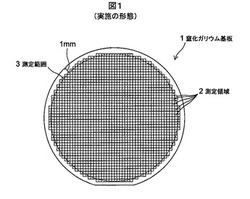

窒化ガリウム基板、発光素子、電界効果トランジスタ及びエピタキシャル膜の製造方法

【課題】特定の一部の領域にのみ加工歪みが存在する場合であっても、短時間で容易に歪みを評価することのできる方法による評価の結果合格した窒化ガリウム基板、その窒化ガリウム基板を含む発光素子もしくは電界効果トランジスタ、及びそのガリウム基板上に結晶を成長させるエピタキシャル膜の製造方法を提供する。

【解決手段】本発明の一態様によれば、窒化ガリウム基板1のバンドギャップに対応する波長のフォトルミネッセンスピーク強度を、窒化ガリウム基板1の表面の測定範囲3内において1mm×1mmの正方形の測定領域2ごとに測定したときの、全測定領域2におけるフォトルミネッセンスピーク強度の最小値が平均値の45%以上であり、測定領域2は測定範囲3内に隙間無く連続する、窒化ガリウム基板1が提供される。

(もっと読む)

発光ダイオードの製造方法

【課題】本発明は、発光ダイオードの製造方法に関する。

【解決手段】本発明の発光ダイオードの製造方法は、結晶成長のための前記結晶面を有する前記基板を提供する第一ステップと、前記基板の前記結晶面にカーボンナノチューブ層を設置する第二ステップと、前記基板の前記結晶面に第一半導体層、活性層及び第二半導体層を順に成長させる第三ステップと、前記第二半導体層の表面に第二電極を設置する第四ステップと、前記基板を除去する第五ステップと、前記第一半導体層の表面に第一電極を設置する第六ステップと、を含む。

(もっと読む)

半導体発光素子の製造方法

【課題】基板上に、面内と周縁部の膜厚の均一な塗布膜を形成することを目的とする。

【解決手段】単結晶ウエハ1と半導体層4と、その間の結晶格子の不整合を緩和するバッファ層3を備えた半導体基板の製造方法であって、前記単結晶ウエハの外周端部1aを被覆材2で被覆した後、前記バッファ層3を前記単結晶ウエハ1の一面側に形成する工程と、前記被覆材2を取り除いた後、前記半導体層4を前記バッファ層3上の一面側に形成すると共に、前記単結晶ウエハ1の外周端部1aから前記半導体層4の外周部4bにかけて前記半導体層4の構成材料からなる堆積物4aを堆積させる工程と、前記半導体層4上に塗布液をスピンコート法により塗布する工程と、を具備してなることを特徴とする半導体基板の製造方法を提供する。

(もっと読む)

窒化物半導体自立基板、窒化物半導体自立基板の製造方法、及び窒化物半導体デバイス

【課題】窒化物半導体単結晶の破壊の原因になる亀裂(クラック)が生じにくい窒化物半導体自立基板、窒化物半導体自立基板の製造方法、及び窒化物半導体デバイスを提供する。

【解決手段】直径が40mm以上、厚さが100μm以上の窒化物半導体単結晶を準備しS10,S20、前記窒化物半導体単結晶の表面と、裏面と、側面との全体を保護膜で被覆して被覆基板を形成するS30。前記被覆基板を1300℃より高い温度下において20時間以上の熱処理S40を施した後、前記被覆基板から前記保護膜を除去して窒化物半導体自立基板を形成するS50。これにより、直径が40mm以上、厚さが100μm以上であり、転位密度が5×106/cm2以下であり、不純物濃度が4×1019/cm3以下であり、最大荷重が1mN以上50mN以下の範囲内におけるナノインデンテーション硬さが19.0GPa以上である窒化物半導体自立基板。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

III族窒化物半導体自立基板の製造方法、III族窒化物半導体自立基板、III族窒化物半導体デバイスの製造方法及びIII族窒化物半導体デバイス

【課題】球面研磨等を施すことなく、自立基板表面における単一の結晶面の面積を再現性良く大きくすることができるIII族窒化物半導体自立基板の製造方法を提供する。

【解決手段】III族窒化物半導体自立基板50は、基板50表面がアズグロウンであり、基板50表面の半分以上の領域が、III族極性のC面からm軸方向若しくはa軸方向に、又はM面からc軸方向若しくはa軸方向に傾いたオフ角を有する単一の結晶面からなる。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

III族窒化物半導体発光素子及びその製造方法、並びにレーザダイオード

【課題】結晶性が高く、また、内部抵抗が低減され、優れた発光特性を有するIII族窒化物半導体発光素子及びその製造方法、並びにレーザダイオードを提供する。

【解決手段】エピタキシャル膜成長用の基板11上又は該基板11上に形成されたバッファ層(III族窒化物層)12上に、AlXGa1−XN(0<X≦1)からなる組成を有する下地層(ELO成長層)13が形成され、下地層13上に、III族窒化物半導体からなるn型半導体層14、発光層15及びp型半導体層16が順次積層されており、下地層13は、基板11又はバッファ層12上に形成された炭素材料からなるELO用マスクパターンを用いて形成されたものである。

(もっと読む)

半導体処理

半導体処理用のデバイス、方法、及びシステムがここで述べられている。半導体処理の幾つかの方法の実施形態は、構造体上にシリコン層を形成することと、シリコン層を通って構造体内に開口部を形成することと、抵抗可変材料がシリコン層上に形成されないように抵抗可変材料を開口部内に選択的に形成することとを含むことができる。 (もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】基板101と、基板101の主方位面の一部を覆うマスク材102と、基板101の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜103とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜103は、マスク材102の上に形成され、ダイヤモンド薄膜103の結晶方位は基板101の結晶方位とそろっている。ダイヤモンド基板101に存在する貫通転位104aは、マスク材102で覆われていない部分のダイヤモンド基板101の主方位面を介してダイヤモンド薄膜103まで貫通するが、貫通転位104bは、マスク材102によってダイヤモンド薄膜103への伝播が遮られるため、ダイヤモンド薄膜103の貫通転位密度は低下し、結晶性が向上する。

(もっと読む)

窒化物半導体発光素子とその製造方法

【課題】窒化物半導体発光素子のクラックの発生を防ぎ、かつ基板の掘り込み領域以外の領域上における窒化物半導体層の組成変動を抑制して、高い歩留まりで窒化物半導体発光素子を得る。

【解決手段】窒化物半導体発光素子は、掘り込み領域(16)が形成された主面を有する窒化物半導体基板(10a)と、掘り込み領域上に形成された結晶成長抑制膜(10b)と、結晶成長抑制膜(10b)および基板(10a)の主面を覆うように堆積された複数の窒化物半導体層(11)を含むことを特徴としている。

(もっと読む)

炭化珪素単結晶の製造方法

【課題】結晶欠陥をより抑制することが可能なSiC単結晶の製造方法を提供する。

【解決手段】CVD法によりエピタキシャル膜2を成長させると、成長させるエピタキシャル膜2の不純物濃度に応じて貫通転位3の成長方向を一定方向に規定できる。例えば、SiC基板1内に含まれていた貫通転位3は、エピタキシャル膜2内においてc軸に対する角度θが(11−22)面もしくは(11−22)面に対して±3°の範囲内、例えば[11−23]方向に平行もしくは[11−23]方向に対して±3°の範囲内の方向に向く。このため、この現象を利用し、エピタキシャル膜2の側面から貫通転位3を排出させることにより、エピタキシャル膜2の成長表面から貫通転位3をほぼ無くすことが可能となる。そして、このようなエピタキシャル膜2を種結晶として昇華法によりSiC単結晶4をバルク成長させれば、結晶欠陥をより抑制することが可能となる。

(もっと読む)

化合物半導体装置の製造方法

【課題】性能を確保しながらコストを低減することができる化合物半導体装置の製造方法を提供する。

【解決手段】基板1上に、外部に連通する開口部が設けられたn−GaN層4を形成し、その後、n−GaN層4上に、GaN層5、AlGaN層6、i−GaN層7、i−AlGaN層8、n−AlGaN層9及びn−GaN層10を形成する。次いで、KOH水溶液中において、n−GaN層4に紫外線を照射して、光電気化学エッチングによりn−GaN層4を溶解させる。

(もっと読む)

イオンの注入による窒化物半導体の形成方法及びこれを利用して製造した電子素子

【課題】本発明は、イオンの注入による窒化物半導体の形成方法及びこれを利用して製造した電子素子に関する。

【解決手段】本発明は、基板100の表面に1E17イオン/cm2超過、5E18イオン/cm2以下のドーズ量及び30〜50keVの注入エネルギーでライン/スペースパターンからなるイオン注入領域120を形成した後、金属窒化物薄膜130を水平成長させることにより、窒化物薄膜の格子欠陥を減少させ、よって電子素子の効率を向上させることができるようにする。

(もっと読む)

単結晶製造装置、それに用いる貴金属枠及び貴金属基板ホルダー

【課題】単結晶製造装置において、良質な単結晶を成長させると共に、繰り返し使用可能な枠および基板ホルダーを提供する。

【解決手段】気相法によって基板7上に単結晶10を成長させる単結晶製造装置において、貴金属枠5を配置し、貴金属枠5の枠内で単結晶10を成長させ、かつ、貴金属枠5の線膨張係数が、単結晶10の線膨張係数と比較して、±1.0×10−6(1/K)の範囲にあるものとする。また、基板7の単結晶成長面には、成長方向制御薄膜6を形成しておく。

(もっと読む)

III族窒化物半導体エピタキシャル基板およびその製造方法

【課題】垂直方向への貫通転位が抑制されて、結晶品質が優れたIII族窒化物半導体エピタキシャル基板を提供する。

【解決手段】基板1上に形成されたIII族窒化物層2上にAlxGa1−xN(0≦x≦1)なる組成のELO成長層4が形成されてなり、ELO(Epitaxial Lateral Overgrowth)成長層4は、III族窒化物層2上に形成された炭素からなるマスクパターン3を用いて形成されたIII族窒化物半導体エピタキシャル基板10。

(もっと読む)

シロキサンを含有するフォトパターン化可能な堆積阻害材料

基板を用意する工程、該基板に、オルガノシロキサン化合物を含むフォトパターン化可能な堆積阻害材料を適用する工程、そして該堆積阻害材料をパターン化する工程を含むパターン化薄膜を形成する原子層堆積法。該薄膜は該堆積阻害材料を有さない該選択された基板領域内だけに実質的に堆積される。 (もっと読む)

III族窒化物半導体の選択成長方法

【課題】III 族窒化物半導体の選択成長方法において、選択成長層のキャリア濃度を精度よく制御すること。

【解決手段】まず、n−GaN基板10上にn- −GaN層11、p−GaN層12を積層し、p−GaN層12表面をNiを堆積した基板とともに塩素系プラズマに曝し、プラズマ損傷層13を形成する(図1a)。次に、エッチングマスク14を形成し、p−GaN層12の一部をドライエッチングし(図1b)、SC1、SC2洗浄を行った後エッチングマスク14を除去する(図1c)。次に、プラズマ損傷層13を選択成長マスクとしてn- −GaN層17を選択成長させる(図1d)。プラズマ損傷層13を選択成長マスクとして用いるため、n- −GaN層17の成長中にSiがドープされることがなく、n- −GaN層17のキャリア濃度の制御を正確に行うことができる。

(もっと読む)

化合物半導体基板の製造方法

【課題】異種材料が埋め込まれた3−5族窒化物半導体を含む化合物半導体結晶を、厚さを大きくすることなしに結晶性よく基板上に成長させる、化合物半導体基板の製造方法を提供する。

【解決手段】成長基板11上に、成長基板11及び3−5族窒化物半導体を含む化合物半導体のいずれとも異なる異種材料が埋め込まれた窒化物半導体を含む窒化物半導体層13を設けて化合物半導体基板を製造する場合、異種材料としてタンタル、チタン、ジルコニウム、ハフニウム、ニオブ、プラチナ、バナジウム、パラジウム、またはそれらのいずれかを含む合金からなる金属材料を選択し、該金属材料による埋め込み部12Aを成長基板11上に形成し、埋め込み部12Aによって横方向成長を促進させつつ3−5族窒化物半導体を含む化合物半導体をエピタキシャル結晶成長させ、これにより、成長基板11の上に3−5族窒化物半導体を含む化合物半導体エピタキシャル結晶を積層する。

(もっと読む)

III族窒化物半導体微細柱状結晶の製造方法およびIII族窒化物構造体

【課題】III族窒化物半導体からなる微細柱状結晶を選択的に成長させることにより、III族窒化物半導体微細柱状結晶の位置および形状を制御する。

【解決手段】微細柱状結晶の製造方法が、基板表面の所定領域に、金属窒化物または金属酸化物からなる表面を有する膜を形成する工程と、前記膜および前記基板表面の境界近傍であって、前記膜の周縁部と前記基板表面とが接する部分を含む領域を成長促進領域として、前記基板表面に成長原料を導き、少なくとも前記成長促進領域上に、III族窒化物半導体からなる微細柱状結晶を成長させる工程とを含む。

(もっと読む)

1 - 20 / 35

[ Back to top ]