Fターム[5F045HA04]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 前処理(膜形成が後) (762) | エッチング (407) | ウェットエッチ (118)

Fターム[5F045HA04]に分類される特許

1 - 20 / 118

半導体装置の製造方法

【課題】 半導体装置において、欠陥を減少させ、静電気放電に対する保護能力を高める。

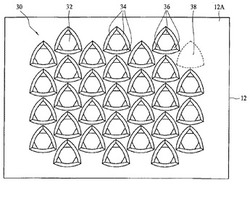

【解決手段】 上面12Aおよび上面12Aに配置された複数のバンプ30を備えた基板1であって、バンプ30の各々が、上面12Aに対して実質的に平行な頂面32および頂面32と上面12Aとの間の複数の壁面34を有するものである基板12、および基板12上に配置されたエピタキシャル層であって、基板12の上面12Aおよびバンプ30の壁面34に実質的に同じ結晶方位を有するエピタキシャル層を備える。また、別の態様において、エピタキシャル層は、基板12上に配置され、実質的に単一の結晶方位を有し、実質的に空隙なく、基板12の上面12Aおよびバンプ30の壁面34を被覆するものであってよい。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

窒化物半導体積層構造体の製造方法

【課題】基板の両面に窒化物半導体層を形成するに際し、基板に被着した堆積物の除去が容易な窒化物半導体積層構造体の製造方法を提供する。

【解決手段】窒化物半導体積層構造体の製造方法では、第1および第2の面11a、11bと第1熱膨張係数α1を有する基板11の第2の面11bに、第1保護膜31を形成する。第1保護膜31が形成された基板11の第1の面11aに、第1熱膨張係数α1と異なる第2熱膨張係数α2を有する第1窒化物半導体層12を形成する。第1窒化物半導体層12に、第2保護膜34を形成する。第1保護膜31を除去し、基板11の第2の面11bを露出させる。露出した基板11の第2の面11bに、第2熱膨張係数α2に略等しい第3熱膨張係数α3を有する第2窒化物半導体層13を形成する。第2保護膜34を除去し、第1窒化物半導体層12を露出させる。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】(0001)面に対して4°以下のオフ角θ1で傾斜したSi面が主面4とされたSiC基板2と、SiC基板2の主面4に形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、SiC基板2の主面4のオフ方向Dを、[11−20]軸方向および[01−10]軸方向に対して15°+/−10°の角度θ2で傾斜した方向にする。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

光集積素子の製造方法

【課題】バットジョイント構造を構成する第1及び第2の半導体積層部上に成長する半導体層に生じる結晶欠陥を低減する。

【解決手段】エッチングマスク30を用いて第1の半導体積層部20にエッチングを施す工程と、Alを含む光吸収層42、及び光吸収層42上に設けられるInPクラッド層44を有する第2の半導体積層部40を、エッチングマスク30を用いて選択的に成長させる第1の再成長工程と、エッチングマスク30を除去するマスク除去工程と、第1及び第2の半導体積層部20,40上に第3の半導体積層部を成長させる第2の再成長工程とを行う。第1の再成長工程において、InPに対してエッチング選択性を有するInP系化合物半導体を含むキャップ層46を第2の半導体積層部40上に更に成長させる。マスク除去工程の前に、エッチングマスク30上に生じたInP系堆積物Deを除去する。

(もっと読む)

半導体発光素子、ウェーハ、および窒化物半導体結晶層の製造方法

【課題】再現性よく光取り出し効率を向上させることができる半導体発光素子、ウェーハ、および窒化物半導体結晶層の製造方法を提供する。

【解決手段】本発明の実施態様によれば、第1半導体層と、発光層と、第2半導体層と、低屈折率層と、を備えた半導体発光素子が提供される。前記第1半導体層は、光取り出し面を形成する。前記発光層は、前記第1半導体層の上に設けられ活性層を有する。前記第2半導体層は、前記発光層の上に設けられている。前記低屈折率層は、前記第1半導体層の屈折率よりも低い屈折率を有し、前記光取り出し面を部分的に覆う。

(もっと読む)

発光ダイオード用基板及び発光ダイオード

【課題】高い光取出し効率を実現でき、かつ、製造が容易で低コストな発光ダイオード用基板及び発光ダイオードを提供する。

【解決手段】表面sに発光層7を含む半導体層3が形成される発光ダイオード用基板であって、サファイア基板からなり、表面sには、発光層7が発光する光を乱反射するランダムに配置された凹凸が形成され、かつ、凹凸は結晶方位を反映して形成されており、凹凸の高さが1μm以上5μm以下であり、表面のX線回折ロッキングカーブ半値幅が60秒以下である。

(もっと読む)

IV族基板表面上での窒化物半導体素子の層構造

【課題】IV族基板表面の混合結晶上に結晶性を向上させたIII族窒化物層構造を有する窒化物半導体素子を提供する。

【解決手段】立方晶のIV族基板材料のIV族基板表面を有する基板上にエピタキシャル堆積されている、III族窒化物層構造を有する窒化物半導体素子であって、IV族基板表面が、C2対称性の単位格子を有するが、C2対称性より高度の回転対称性の単位格子は有さない{nml}表面[式中、n、mはゼロ以外の整数であり、かつl≧2]であるようにする。

(もっと読む)

立方晶炭化珪素膜の製造方法

【課題】横方向結晶成長における横方向成長速度が縦方向成長速度と同等の成長速度を維持することにより、等方的に立方晶炭化珪素を成長させることができ、より広い低欠陥領域を有する立方晶炭化珪素膜を形成させることのできる立方晶炭化珪素膜の製造方法を提供する。

【解決手段】シリコン基板2の表面2aに立方晶炭化珪素層11を形成する工程と、立方晶炭化珪素層11を選択除去し、結晶成長領域の結晶方位面が{100}面となる所望のパターンの立方晶炭化珪素シード層11aを形成する工程と、この立方晶炭化珪素シード層11a上に立方晶炭化珪素を成長させる工程と、を有する。

(もっと読む)

炭化珪素単結晶の製造方法

【課題】p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶の製造方法を提供する。

【解決手段】縦型MOSFETのドレインリークなどのリークを引き起こす転位は貫通らせん転位であるということに基づき、Alイオンの注入および活性化アニール後に溶融KOHエッチング等を行うことにより、リーク部に相当する場所に非常に深いエッチピット1bを形成する。そして、その表面に、エッチピット1bの側壁部に成長した部分同士が互いに接触する条件にてSiC成長層4をエピタキシャル成長させることで、SiC成長層4に転位が引き継がれないようにする。これにより、貫通らせん転位1aが存在しない表面を有するSiC成長層4を得ることが可能となる。したがって、p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶を製造することができる。

(もっと読む)

シリコンウェーハのエピタキシャル成長方法

【課題】シリコンウェーハとエピタキシャル層との界面におけるボロン量を抑えるのに好適なエピタキシャル成長方法を提供する。

【解決手段】シリコン単結晶をスライス11して得られたスライスウェーハをラッピング又は研削11し化学エッチング12し鏡面研磨13し洗浄14した後保管16されたボロンがウェーハに付着したシリコンウェーハ上にエピタキシャル成長する方法において、保管16されたシリコンウェーハをH2O−H2O2−NH4OHの混合液で洗浄17し、洗浄17したシリコンウェーハをエピタキシャル成長装置内に搬入18し、搬入18したシリコンウェーハの表面に1000〜1200℃の温度で塩化水素ガスを流して、エッチング取り代が0.1〜0.5μmとなるようにウェーハ表面の気相エッチング19を行い、続いて成長装置内に原料ガスをキャリアガスとともに流して気相エッチングされたウェーハ表面にエピタキシャル層を形成20する。

(もっと読む)

半導体装置の製造方法

【課題】 ピンチオフ特性を改善しまたはチャネル層の移動度を向上させ電気的特性の良好な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層20を形成する工程と、前記GaN系半導体層に開口部28を形成する工程と、前記開口部の側面に電子走行層22および電子供給層26を形成する工程と、前記電子供給層の前記開口部側の側面にゲート電極32を形成する工程と、前記GaN系半導体層上にソース電極30を形成する工程と、前記GaN系半導体層の前記ソース電極と相対する面に接続するドレイン電極34を形成する工程と、を具備する半導体装置の製造方法。

(もっと読む)

SiCエピタキシャルウェハ

【課題】三角欠陥及び積層欠陥が低減され、キャリア濃度及び膜厚の均一性が高く、ステップバンチングフリーのSiCエピタキシャルウェハを提供する。

【解決手段】本発明のSiCエピタキシャルウェハは、0.4°〜5°のオフ角で傾斜させた4H−SiC単結晶基板上にSiCエピタキシャル層を形成したSiCエピタキシャルウェハであって、前記SiCエピタキシャル層の表面の三角形状の欠陥密度が1個/cm2以下であることを特徴とする。

(もっと読む)

半導体ウェハの製造方法

【課題】半導体ウェハの外周領域におけるクラック発生を抑制できる半導体ウェハの製造方法を提供する。

【解決手段】本発明に係る半導体ウェハの製造方法は、シリコンからなり且つ中央領域と外周領域とを有する半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体からなる化合物半導体層5と、を備える半導体ウェハの製造方法であって、

前記半導体基板1の前記外周領域に設けられたテーパ部12の上に前記化合物半導体層5が成長することを阻止する成長阻止層4を形成するステップと、

前記成長阻止層4が形成された前記半導体基板の少なくとも前記中央領域上に前記化合物半導体層5を成長させるステップと、を備えることを特徴とする。

(もっと読む)

1 - 20 / 118

[ Back to top ]