Fターム[5F046PA03]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 光の吸収膜、反射膜 (454) | 吸収膜 (382) | 酸化膜 (16)

Fターム[5F046PA03]に分類される特許

1 - 16 / 16

積層構造体

【課題】エッチング層の膜厚変動に対して露光範囲の大きさのばらつきが少なく、インプリント原版へのレーザーによる精密露光を可能とする積層構造体を提供することを目的とする。

【解決手段】本発明の積層構造体は、波長300nm以上700nm以下の範囲における消衰係数Xが0.5以上10以下である基材11と、基材11の上に設けられた光吸収層と、光吸収層12の上に設けられたエッチング層13と、エッチング層13の上に設けられたレジスト層14と、を備えることを特徴とする。

(もっと読む)

パターン形成方法

【課題】微細化したホール又はラインのパターンを、従来よりも容易に形成する製造方法を提供する。

【解決手段】被加工膜(2)上に第1のカーボン膜(3)と第1のARL(4)を順次堆積し、第1のARLをパターニングする工程、第2のカーボン膜(6)と第2のARL(7)を順次堆積し、第2のARLをパターニングする工程と、第2のARLをマスクとして第2のカーボン膜を除去する工程と、露出した第1のARLとをマスクとして、第1のカーボン膜を除去する工程と、残存している第1及び第2のカーボン膜をマスクとして被加工膜のエッチングを行う工程とを備えている。

(もっと読む)

CDバイアスの減少したシリコン含有反射防止コーティング層のエッチング方法

【課題】 本発明は、基板上のシリコン含有反射防止コーティング(ARC)層内の特徴部位をエッチングする方法に関し、より詳細にはCDバイアスを減少させながらシリコン含有反射防止コーティング(ARC)層内の特徴部位をエッチングする方法に関する。

【解決手段】 基板上の反射防止コーティング(ARC)層を乾式現像する方法が記載されている。当該方法は、多層マスクを有する基板をプラズマ処理システム内に設ける工程を有する。続いてリソグラフィプロセスを用いて前記リソグラフィ層内に特徴部位のパターンが形成される。その後前記特徴部位のパターンは、ドライプラズマエッチングプロセスを用いて、前記リソグラフィ層から前記シリコン含有ARC層へ転写される。入れ子構造と孤立構造との間の限界寸法(CD)バイアスのオフセットは減少する。

(もっと読む)

乾式または液浸リソグラフィを用いる45nmフィーチャサイズでの、フォトレジスト材料の崩壊およびポイゾニングの解消

90nm以下の範囲内のフィーチャサイズを有する半導体デバイスを製作するための方法および構造が提供される。本発明の一実施形態では、基板を処理する方法であって、基板の表面上に反射防止被覆層を堆積させること、反射防止被覆層上に接着促進層を堆積させること、および接着促進層上にレジスト材料を堆積させることを含む方法が提供される。本発明の別の実施形態では、誘電体基板と、誘電体層上に堆積された非晶質炭素層と、非晶質炭素層上に堆積された反射防止被覆層と、反射防止被覆層上に堆積された接着促進層と、接着促進層上に堆積されたレジスト材料とを含む、半導体基板構造が提供される。  (もっと読む)

(もっと読む)

液浸リソグラフィーにおけるパターン崩壊を防止するためのプラズマ表面処理

【課題】 浸漬現像後のフォトレジストを乾燥した場合にフォトレジストマスクの崩壊を減少させる方法の提供。

【解決手段】 特徴部サイズが縮小するのにつれて、フォトレジストマスクをすすぐために用いられる水の毛管力が、ARCに対するフォトレジストの接着力より大きい点に近づく。毛管力が接着力を超える場合、水が乾くのにつれて水が隣接の特徴部を共に引っ張るためにマスクの特徴部が崩壊してしまう。フォトレジストを堆積させる前にARCの上に密封酸化物層を堆積させることによって、接着力が毛管力を超えることができ、フォトレジストマスクの特徴部は崩壊することができない。

(もっと読む)

ホールパターンの形成方法および半導体装置の製造方法

【課題】ホールパターンの疎密に依存することなく解像限界以下のホールパターンを形成する方法を提供することを目的とする。

【解決手段】半導体基板101上に形成した加工対象層102に微細なホールパターン55を形成するホールパターンの形成方法であって、前記加工対象層102上に、カーボン膜層103、中間マスク層104、フォトレジスト層105を順次積層して3層構造体を形成する3層構造体形成工程と、前記中間マスク層104にホールパターン50をパターニングする中間マスク層パターニング工程と、サイドウォール用酸化膜形成工程と、前記サイドウォール用酸化膜106からなるサイドウォール部116を形成するサイドウォール部形成工程と、前記加工対象層102に前記微細なホールパターン55をパターニングする加工対象層パターニング工程とを有することを特徴とするホールパターンの形成方法を用いることにより、上記課題を解決できる。

(もっと読む)

微細パターンの形成方法、パターン保護材料と半導体装置

【課題】複数のパターンを合成して微細パターンを形成する方法において、プロセスを簡易化し、低コストで実施できる方法を提供する。

【解決手段】第1のパターンを形成する工程と、保護膜を形成する工程と、第2のパターンを保護膜上に形成する工程と、第2のパターンをマスクとして、保護膜と、保護膜により保護されたパターンをドライエッチングする工程と、保護膜を除去する工程とを備え、保護膜の形成工程から保護膜の除去工程までの工程を、単数回または複数回実施する。

(もっと読む)

レジスト下層膜用組成物及びその製造方法

【課題】レジスト膜との密着性に優れ、レジストパターンの再現性を向上させるとともに、現像等に用いられるアルカリ液及びレジスト除去時の酸素アッシングに対して耐性を有するレジスト下層膜を形成することができ、且つ、保存安定性に優れたレジスト下層膜用組成物を提供する。

【解決手段】本レジスト下層膜用組成物は、下記[A−1]、[B]及び[C]のシラン化合物由来のポリシロキサン(例えば、[A−1]、[B]及び[C]のシラン化合物の混合物の加水分解物及び/又はその縮合物等)を含有する。

[A−1];R1bR2cSi(OR3)4−aで表されるシラン化合物

[B];R4eR5fSi(OR6)4−dで表されるシラン化合物

[C];R7gSi(OR8)4−gで表されるシラン化合物

(もっと読む)

シロキサンポリマーを含む反射防止膜組成物

本発明は、フォトレジスト用の下層を形成するための、酸発生剤及び新規シロキサンポリマーを含む新規反射防止膜組成物であって、前記シロキサンポリマーが、少なくとも一種の吸光性発色団及び次の構造(1)

[式中、mは0または1であり、W及びW’は、独立して、環状エーテルをポリマーのケイ素に連結する原子価結合または接続基であり、そしてLは、水素、W’及びWから選択されるか、あるいはL及びW’は、環状エーテルをポリマーのケイ素に連結する環状脂肪族連結基を一緒になって構成する]

で表される少なくとも一種の自己架橋性官能基を含む、前記反射防止膜組成物に関する。また本発明は、前記新規反射防止膜組成物の上にコーティングされたフォトレジストに像を形成する方法にも関し、良好なリソグラフィの結果を供する。更に本発明は、少なくとも一種の吸光性発色団及び構造(1)の少なくとも一種の自己架橋性官能基を含む、新規のシロキサンポリマーにも関する。  (もっと読む)

(もっと読む)

反射防止膜及び露光方法

【課題】液浸リソグラフィ技術において、露光光一層斜めに入射する場合であっても、レジスト層とシリコン半導体基板との界面における反射率を充分に低減することができる反射防止膜を提供する。

【解決手段】2層構造反射防止膜は、190〜195nmの波長を有し、開口数が0.93乃至1.2である露光系にてレジスト層を露光する際に用いられる、レジスト層とシリコン半導体基板の表面に形成されたシリコン酸化膜との間に形成され、反射防止膜を構成する上層、下層の複素屈折率N1,N2を、N1=n1−k1i,N2=n2−k2iとし、上層、下層の膜厚をd1,d2とし、[n10,k10,d10,n20,k20,d20]の値の組合せとして所定の組合せを選択したとき、n1,k1,d1,n2,k2,d2が、以下の関係式を満足する。{(n1−n10)/(n1m−n10)}2+{(k1−k10)/(k1m−k10)}2+{(d1−d10)/(d1m−d10)}2+{(n2−n20)/(n2m−n20)}2+{(k2−k20)/(k2m−k20)}2+{(d2−d20)/(d2m−d20)}2≦1

(もっと読む)

コーティング組成物

【課題】反射防止および液浸リソグラフィー用途において有用な組成物を含む、マイクロリソグラフィーのための新規物質を提供する。

【解決手段】一態様において、1以上のケイ素、アンチモン、アルミニウム、イットリウム、セリウム、ランタン、スズ、チタン、ジルコニウム、ハフニウム、インジウムまたは亜鉛化合物を含む成分を含有するコーティング組成物が提供される。別の態様においては、複数の個別の粒子を含有するコーティング組成物が提供される。本発明の好ましいコーティング組成物は、反射防止の目的、特に下層をなすフォトレジストコーティング層を伴う場合に有用であり、並びに液浸リソグラフィーにおけるバリア層に有用である。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フォト工程のマージンを向上させること、パターン不良を防止すること、及びフォトマスクのアスペクト比を減らしてフォトマスク崩壊などの不良を防止することが可能なフラッシュメモリ素子の製造方法の提供。

【解決手段】所定の下部パターンが形成された半導体基板上に反射防止及びエッチング停止用膜を形成する段階と、前記反射防止及びエッチング停止用膜上に絶縁膜を形成する段階と、前記絶縁膜上にフォトレジストを形成する段階と、前記フォトレジストをパターニングする段階と、前記パターニングされたフォトレジストをマスクとして前記絶縁膜と前記反射防止及びエッチング停止用膜をエッチングしてトレンチを形成する段階とを含む、フラッシュメモリ素子の製造方法を提供する。

(もっと読む)

パターン形成方法および半導体装置の製造方法

【課題】 被エッチング膜の微細パターンを形成する工程において、半導体基板上に堆積された被エッチング膜をより微細に高精度でパターニングする。

【解決手段】 半導体基板上に被エッチング膜を堆積する工程と、被エッチング膜上にSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜を堆積する工程と、有機無機ハイブリッド膜のパターンを形成する工程と、有機無機ハイブリッド膜の表面部を酸化層に変換する工程と、酸化層を選択的に除去して、有機無機ハイブリッド膜パターンを所定寸法にする工程と、所定寸法にされた有機無機ハイブリッド膜パターンをマスクとして被エッチング膜をエッチングする工程とを含む。

(もっと読む)

低温かつ低堆積レートでTEOSキャップ層を形成する方法

本発明は、限界寸法が50nm以下のポリシリコンラインフィーチャをパターニングするためのカーボンハードマスク層のために、二酸化シリコンのキャップ層を形成する方法を開示する。このために、低温のプラズマ支援型CVDプロセスが用いられ、このプロセスにおいては、堆積速度を低く維持して層厚の制御性と二酸化シリコン層の光学特徴とを向上させることができる。  (もっと読む)

(もっと読む)

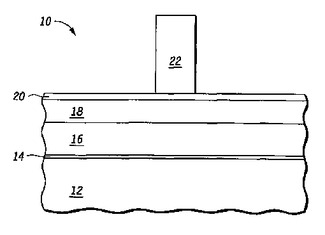

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

スピンオンフォトパターン形成性中間層誘電性材料の使用及びそれを利用する中間半導体素子構造体

フォトパターン形成性塗布材料がこれまでに用いられなかった波長で半導体素子構造体の形成に用いられことを可能とするキャップ層。該フォトパターン形成性塗布材料を半導体基板へ層として塗布する。該キャップ層及びフォトレジスト層がそれぞれ該フォトパターン形成性層上に形成される。該キャップ層は放射線を吸収または反射し、そして該フォトパターン形成性層を該フォトレジスト層のパターン化に用いられた第1波長の放射線から保護する。該フォトパターン形成性塗布材料は第2波長の放射線に露光されると二酸化ケイ素系材料へ変換される。 (もっと読む)

1 - 16 / 16

[ Back to top ]