Fターム[5F048AB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | 論理回路 (1,440)

Fターム[5F048AB03]の下位に属するFターム

Fターム[5F048AB03]に分類される特許

161 - 180 / 845

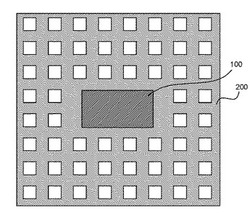

半導体集積回路

【課題】アニールプロセス時において、アニール温度の温度むらを低減することを目的とする。

【解決手段】 複数のトランジスタが形成された第1領域100と、第1領域100の周囲に配置され、複数のダミートランジスタが形成された第2領域200とを備え、第2領域200に形成された複数のダミートランジスタのピッチpが、複数のトランジスタを形成する際に用いるフラッシュランプ光の中心波長λc以下である。さらに、第2領域のダミートランジスタの素子形成領域の幅が、ダミートランジスタのピッチの半分以下。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、及び電子機器

【課題】積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。また、固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】第1の半導体ウェハ31と、第2の半導体ウェハ45とを、基板間配線68で接続する構成とする。基板間配線は、第1の半導体ウェハ31表面の第1の多層配線層に形成される接続孔66と、第2の半導体ウェハ45表面の第2の多層配線層に形成された貫通接続孔65とに、導電材料が埋め込まれて形成されている。そして、貫通接続孔65は接続孔66の直径よりも大きく形成されている。これにより、貫通接続孔65の構内に導電材料を埋め込む際のボイドの発生を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、従来の製造方法と比較し、同一ウエハまたは製品上において複数のデバイス耐圧帯と良好なオン抵抗をもったLDMOSを備えた半導体装置およびその製造方法を提供することを目的とするものである。

【解決手段】 第1電界緩和用酸化膜24と第2電界緩和用酸化膜25と素子分離用LOCOS酸化膜17の膜厚を別々に最適化することにより、同一ウエハにおいて複数のデバイス耐圧と良好なオン抵抗を実現する。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

薄膜回路構造及びその製造方法並びに有機EL装置

【課題】回路構造のスペースを小さくして画素の微細化を達成できる、薄膜回路構造及びその製造方法を提供する。

【解決手段】基材1上の面内方向Xに、ゲート電極2、ゲート絶縁膜3、酸化物半導体膜4、ソース電極5s及びドレイン電極5dで少なくとも構成された隣り合う2以上の薄膜トランジスタ10A,10Bを有する薄膜回路装置12であって、前記2以上の薄膜トランジスタ10A,10Bは、共通するゲート絶縁膜3を有するとともに、ゲート絶縁膜3の下に第1の酸化物半導体膜4Aが設けられた第1の薄膜トランジスタ10Aと、ゲート絶縁膜3の上に第2の酸化物半導体膜Aが設けられた第2の薄膜トランジスタ10Bとを有するようにして、上記課題を解決した。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

トランスミッションゲート及び半導体装置

【課題】様々な入力電圧に対応して高S/N特性を実現できるトランスミッションゲートを提供する。

【解決手段】入力電圧Vinをドレインから入力され、電圧(Vin−Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するPMOSトランジスタ11と、PMOSトランジスタ11と等しいゲート長とゲート幅とゲート酸化膜厚と閾値電圧の絶対値とを有し、入力電圧Vinをドレインから入力され、電圧(Vin+Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するNMOSトランジスタ12と、を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、および、リソグラフィマスクの製造方法

【課題】リソグラフィを用いて形成される半導体装置を高性能化させる。

【解決手段】互いに同じ材質からなる第1導体パターンPE1および第1ダミー導体パターンDM1を含む第1の層L1と、第2導体パターンPE2を含む第2の層L2とがシリコン基板SUB1上に積層されている。第2導体パターンPE2は、第1導体パターンPE1または第1の層L1より下層の導電部と、コンタクトプラグCP1によって電気的に接続されている。第1ダミー導体パターンDM1のうち、コンタクトプラグCP1と重なる部分には、それよりも断面積の大きい孔部HL1が形成されている。そして、コンタクトプラグCP1は孔部HL1内を通って配置されることで、第1ダミー導体パターンDM1と接触しないようにして形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

半導体装置

【課題】放電効率の向上と、通常動作時の電位変動の伝達の抑制とを両立させることができる静電気保護素子を有する半導体装置を提供すること。

【解決手段】第1電源電位配線と第1接地電位配線との間にて、電気的に接続された第1回路、及びダイオード接続されたMOSトランジスタを有する第1保護素子と、第2電源電位配線と第2接地電位配線との間にて、電気的に接続された第2回路、及びダイオード接続されたMOSトランジスタを有する第2保護素子と、前記第1接地電位配線と前記第2接地電位配線との間に2つのMOSトランジスタが互いに逆バイアス状態になるように並列にダイオード接続された第3保護素子と、を備え、前記第3保護素子における2つのMOSトランジスタの閾値電圧は、前記第1保護素子及び前記第2保護素子における各MOSトランジスタの閾値電圧よりも大きく設定されている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】チップ面積を縮小しつつ、高信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置は、第1、第2配線S1,S2を有する第1回路部210と、第3、第4配線S3、S4を有する第2回路部220と、それらの間に設けられ、第1回路部210から第2回路部220に向かう方向に直交する方向に沿って隣接する第1、第2トランジスタTR1、TR2を有する中間部230と、を備え、第1トランジスタTR1の一方の拡散層DA1の第1接続領CA1内の高濃度領域CAI1は第1配線S1に、他方の拡散層DB1は第3配線S3に接続される。第1接続領域CA1とゲートG01との距離は、第2接続領域CA2とゲートG02との距離よりも長い。第1トランジスタTR1の一方の拡散層DA1の第1接続領域CA1とゲートG01との間には、第1接続領域CA1よりも幅が狭い延在領域EA1が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

161 - 180 / 845

[ Back to top ]