Fターム[5F048AB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | 論理回路 (1,440)

Fターム[5F048AB03]の下位に属するFターム

Fターム[5F048AB03]に分類される特許

141 - 160 / 845

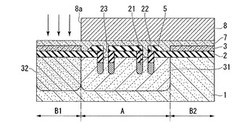

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン抵抗とメモリ回路とを混載した半導体装置において、メモリの情報の保持時間を長くして、かつ書込・読出時間を短くする。

【解決手段】容量素子400はメモリセルを構成しており、第1トランジスタ200は、ソース及びドレインとなる第1拡散層226が容量素子400に接続している。シリコン抵抗素子300はシリコン層からなる。第1拡散層226はシリサイド層を有していない。また第1ゲート電極230は、金属層232及びシリコン層234を積層した積層構造を有している。そして第1ゲート電極230は、素子分離膜50上に位置する領域の少なくとも一部にシリサイド層235を有しており、かつ第1拡散層226に挟まれた領域にはシリサイド層を有していない。そしてコンタクト513は、シリサイド層235を介して第1ゲート電極230に接続している。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置のESD耐量を向上する。

【解決手段】半導体集積回路装置70には、電源回路1、内部回路2、電流源3、2入力NAND回路4、コンデンサC1、ダイオードD1、出力トランジスタMDT1、端子Pin、端子Pvcc、端子Pvo、及び端子Pvssが設けられる。電流源3、コンデンサC1、及び2入力NAND回路4は、端子PVoに(+)ESDが印加されたとき、2入力NAND回路4の出力側のノードN3の信号レベルを“High”レベルにして、出力トランジスタMDT1をオンさせてESDの電荷を低電位側電源Vss側に逃がす。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

SeOI上の疑似インバータ回路

【課題】メモリアレイのワードライン・ドライバ回路として使用できる、大きくなく、低消費電力の回路を提供する。

【解決手段】半導体・オン・インシュレータ(SeOI)基板上に形成された回路であって、電源電位を印加する為の第1、第2の端子間に第2のチャネル型のトランジスタと直列の第1のチャネル型のトランジスタを含み、トランジスタの各々が薄層におけるドレイン領域およびソース領域と、ソース領域とドレイン領域間に延びるチャネルと、チャネルの上方に配置されたフロント・コントロール・ゲートとを備え、各トランジスタが、トランジスタのチャネルの下方のベース基板に形成され、かつトランジスタの閾値電圧を調整する為にバイアスされうるバック・コントロール・ゲートを有し、トランジスタのうちの少なくとも1つが閾値電圧を十分に調整するバックゲート信号の作用の下、空乏モードで動作するように構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、製造歩留まりを向上できる技術を提供する。

【解決手段】給電領域に位置するCGシャント部の選択ゲート電極CGの半導体基板1の主面からの第2高さd2が、メモリセル形成領域の選択ゲート電極CGの半導体基板1の主面からの第1高さd1よりも低くなるように、CGシャント部の選択ゲート電極CGを形成する。

(もっと読む)

静電気保護回路及び集積回路

【課題】静電気保護用の抵抗を使用せずに静電気放電から保護することのできる静電気保護回路及び集積回路を提供する。

【解決手段】端子P1が複数のトランジスター21に接続され、端子P2が入出力パッドに接続されており、所定範囲のレベルの電気信号に対して端子P1と端子P2との間を通すトランスミッションゲート10Aを備え、トランスミッションゲート10Aは、前記所定範囲外のレベルの電気信号を前記所定範囲のレベルの電気信号に変更可能なクランプダイオード14Aを有する。

(もっと読む)

半導体装置の作製方法及び電気光学装置

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用

いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いて

SOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体

基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との

密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

141 - 160 / 845

[ Back to top ]