Fターム[5F048AB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | 論理回路 (1,440)

Fターム[5F048AB03]の下位に属するFターム

Fターム[5F048AB03]に分類される特許

101 - 120 / 845

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子特性の安定性を向上できる半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法は、シリコン基板101の表面に第1の酸化膜103を形成する工程と、周辺回路領域A2内にあるシリコン基板101の所定箇所に不純物を注入し、この所定箇所上の第1の酸化膜103を除去し、この所定箇所上に第2の酸化膜112を形成する工程と、メモリセル領域A1内の第1の酸化膜103にトンネルウィンドウを形成し、このトンネルウィンドウ内で露出したシリコン基板101上にトンネル酸化膜116を形成し、トンネル酸化膜116を覆うメモリセル用ポリシリコン膜118を形成する工程と、第2の酸化膜112を形成する前記工程の後にメモリセル用ポリシリコン膜118上にONO膜119を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】本発明は、接続不良を抑制したコンタクト形成方法を備える半導体装置を提供するものである。

【解決手段】半導体装置は、配線層を備える第1の回路領域と、第1の回路領域の上に形成された絶縁膜と、絶縁膜の上に形成され、シリサイド膜を備える第2の回路領域と、配線層上に設けられ、配線層と電気的に接続された下部コンタクトと、下部コンタクト上に設けられ、下部コンタクトと前記シリサイド膜とを電気的に接続する上部コンタクトとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物の偏析に起因する、ドレイン領域と空乏層との間のリーク電流の発生を抑制することが可能な半導体素子を含む半導体装置を提供する。

【解決手段】本半導体装置は、主表面を有する半導体基板SUBと、主表面上に形成された、論理回路を構成するコアトランジスタと、入出力回路を構成するI/Oトランジスタとを備える。主表面からI/On型トランジスタのn型不純物領域NRの最下部までの距離は、主表面からコアn型トランジスタのn型不純物領域NRの最下部までの距離より長い。主表面からI/Op型トランジスタのp型不純物領域PRの最下部までの距離は、主表面からコアp型トランジスタのp型不純物領域の最下部までの距離より長い。主表面からI/On型トランジスタのn型不純物領域の最下部までの距離は、主表面からI/Op型トランジスタのp型不純物領域の最下部までの距離より長い。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく、高耐圧トランジスタへのイオン注入を的確に実行することを可能にする。

【解決手段】

第1素子形成領域(AA1)のうち、第1トランジスタ(Tr1)のゲート電極が形成されるべき第1領域(R1’)の直上に位置するマスク材(M1)の第1部分(H1’)を除去する一方、第1部分(H1’)以外の第1素子形成領域(AA1)にはマスク材(M1)を残存させる。一方、第2素子形成領域(AA2)のうち、第2トランジスタ(Tr2)のゲート電極が形成されるべき第2領域(R1)の直上に位置するマスク材の少なくとも第2部分(H1)と、第2トランジスタ(Tr1)のソース/ドレイン拡散領域が形成されるべき第3領域(R2、R3)の直上に位置するマスク材の少なくとも第3部分(H2,H3)とを除去してマスク材の開口を形成する。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

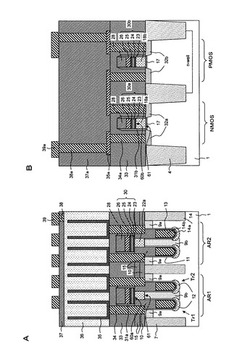

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

固体撮像装置およびその製造方法

【課題】製造コストの低減に対して有利な固体撮像装置を提供すること。

【解決手段】実施形態の固体撮像装置は、フォトダイオード1-1と、第1導電型の第1、第2不純物拡散層206-10,206-12と、第1、第2トランジスタ2-1,3-1とを備える。フォトダイオード1-1は画素の一部を構成する。第1不純物拡散層206-10は、フォトダイオード1-1間を分離する。第1トランジスタ2-1は、第1不純物拡散層206-10上に設けられ、画素の一部を構成すると共に、フォトダイオード1-1に接続される。第2不純物拡散層206-12は、その底部の深さが第1不純物拡散層206-10の底部の深さに一致する。第2トランジスタ3-1は、第2不純物拡散層206-12上の第3不純物拡散層210上に設けられ、画素の一部を構成すると共に、第1トランジスタ2-1に接続される。第2不純物拡散層206-12内の不純物の濃度勾配は、第1不純物拡散層206-10内の不純物の濃度勾配と等しい。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

101 - 120 / 845

[ Back to top ]