Fターム[5F048AB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | 論理回路 (1,440) | インバータ回路 (545)

Fターム[5F048AB04]に分類される特許

161 - 180 / 545

半導体集積回路、半導体集積回路の駆動方法、表示装置および電子機器

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、電源電位と接続された出力ノードと、出力ノードと電源電位より低電位である接地電位との間に直列に接続された第1のnチャネル型トランジスター、第2のnチャネル型トランジスターおよび第3のnチャネル型トランジスターを有し、第1のnチャネル型トランジスターの一端は、接地電位に接続され、他端は、第2のnチャネル型トランジスターの一端に接続され、ゲート端子は、入力ノードに接続され、第2のnチャネル型トランジスターの他端は、第3のnチャネル型トランジスターに接続され、ゲート端子は、電源電位と接地電位との間に位置する第1中間電位に接続され、第3のnチャネル型トランジスターの他端は出力ノードに接続され、ゲート端子は電源電位に接続されている。

(もっと読む)

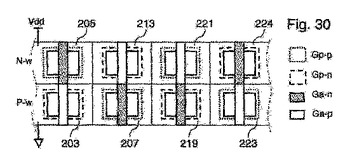

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置及びその製造方法を提供する。

【解決手段】BOX層1上のSOI層2に形成された部分空乏型のトランジスター10と、ダイオード20とを備え、トランジスター10は、SOI層2上に絶縁膜13を介して形成されたゲート電極14と、ゲート電極14の両側下のSOI層2に形成されたN型のソース15a又はドレイン15bとを有し、ダイオード20は、SOI層2の浅い部分に形成されたP型不純物層21と、SOI層2の深い部分に形成されたN型不純物層22と、を有する。P型不純物層21と、N型不純物層22は深さ方向に積層されており、P型不純物層21の側面とN型不純物層22の側面はそれぞれトランジスター10のボディ領域2に接している。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

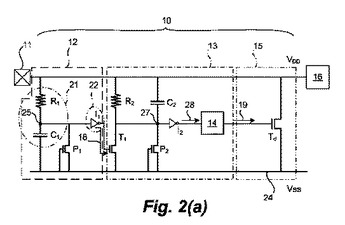

二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路

【課題】回路を構成する二重ゲート電界効果トランジスタの動作モードを、回路組み上げ後に適宜変更できるようにした二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路を提供する。

【解決手段】二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路は、二重ゲート電界効果トランジスタX1(21)の第1ゲートG1に第1の入力信号in1を加え、第2ゲートG2に選択回路11aを接続し、その選択回路11aに第1の入力信号in1と第2の入力信号in2を加え、選択回路11aにより第1の入力信号in1または第2の入力信号in2を選択して第2ゲートG2に加える。第2ゲートG2に切り替えて入力される入力信号に応じて、3端子動作又は4端子動作を行わせる。

(もっと読む)

半導体装置

【課題】回路動作の安定性を高め、消費電力の低減を可能とした半導体装置を提供する。

【解決手段】フローティングボディ型のPD−SOI−MOSFET21〜26を有する分周回路を備え、この分周回路の動作時は、MOSFET22、23,24、26の各ゲート(G)に固定電圧が印加されてMOSFET22、24がオンすると共に、MOSFET23、26がオフする。また、MOSFET21、25の各ゲート(G)に振幅電圧が印加されて、MOSFET21、25がオン、オフを繰り返す。このように動作する分周回路において、MOSFET23、26の閾値電圧の絶対値は、例えばチャネルドープにより、MOSFET21、25の閾値電圧の絶対値よりも大きく設定されている。

(もっと読む)

絶縁ゲート型電界効果トランジスタ回路

【課題】温度変化による動作特性の低下を抑制する電界効果トランジスタ回路を提案する。

【解決手段】本発明の例に係る絶縁ゲート型電界効果トランジスタ回路は、拡散層をそれぞれ備える第1のソース/ドレイン4S,4Dと、チャネル領域上に設けられる第1のゲート絶縁膜2と、前記第1のゲート絶縁膜2上に設けられる第1のゲート電極3とを有する第1の電界効果トランジスタTrと、半導体基板1とショットキー接合を形成する金属層をそれぞれ備える第2のソース/ドレイン14S,14Dと、チャネル領域上に設けられる第2のゲート絶縁膜12と、第2のゲート絶縁膜12上に設けられる第2のゲート電極13と、を具備し、第1のドレイン4Dと第2のドレイン14Dとが並列に接続される。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

標準セル、標準セルライブラリおよび半導体集積回路

【課題】ゲートもしくはダミーゲートのゲート長が不規則な標準セルにおいて、特性のばらつきを抑制する。

【解決手段】本発明の標準セルでは、他のトランジスタと異なるゲート長を有するトランジスタの両隣のトランジスタのうち少なくとも一方のトランジスタは常にオフ状態とする。これにより、ゲート仕上がり寸法がばらついても標準セルの動作には影響を与えないので、標準セルの特性のばらつきを抑制することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性及び信頼性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】絶縁物(絶縁性酸化物、絶縁性窒化物、若しくは酸窒化シリコン、酸窒化アルミニウムなど)、代表的にはSiO2を含む酸化物半導体ターゲットを用いて成膜を行い、酸化物半導体層の膜厚方向におけるSi元素濃度が、ゲート電極に近い側からゲート電極に遠い側に増加する濃度勾配を有する半導体装置を実現する。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11を直列又は一のpMOSトランジスタ12を備えた並列回路に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21を直列又は一のnMOSトランジスタ22を備えた並列回路に接続した第2の回路ブロック2とを備え、前記第1の回路ブロック1と前記第2の回路ブロック2との接続点Sを出力端子Voutに接続するとともに、全ての前記pMOSトランジスタ11,12のゲート及び全ての前記nMOSトランジスタ21,22のゲートを共通の入力端子Vinに接続する半導体回路。

(もっと読む)

半導体装置

【課題】Pチャンネル型MOSトランジスタをOFFさせる時に、駆動信号生成回路内のプルアップトランジスタと他の素子に流れる貫通電流を抑制できる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、従来の半導体装置のプルアップトランジスタ20に代えて、NAND素子7を設けた。その結果、プルアップトランジスタ20を排除したことから、プルアップトランジスタ20に起因する従来の半導体装置において課題であった、Pチャンネル型MOSトランジスタ1のOFF時に駆動信号生成回路内のプルアップトランジスタ20と他の論理素子とに生じる貫通電流を抑制できる。

(もっと読む)

半導体集積回路

【課題】本発明は、メモリ回路部と非メモリ回路部を有する集積回路に関し、論理回路素子に対するソフトエラーとしてのSET(Single Event Transient)を効果的に抑制できる、集積回路を提供する。

【解決手段】論理回路ブロック202に含まれるNMOSトランジスタのチャネルが形成される第2導電型半導体領域101のP型濃度が、SRAMブロック201内のN型の(駆動)トランジスタN1,N2のチャネルが形成される第2導電型半導体領域101のP型濃度より低い。このため、論理回路ブロック202において、より容易に寄生バイポーラトランジスタがオンし、SETの発生要因となるドレイン電位低下を防止する。そのため、回路的負担増なしにSETを効果的に抑制できる。

(もっと読む)

半導体集積回路装置

【課題】従来のパワースイッチと比較して、高速動作を行う活性状態と、内部論理状態は保持しているが低リーク状態である非活性状態を実現し、その二つの状態間の遷移を高速かつ低雑音かつ低電力を実現する。

【解決手段】第1の外部電源電圧(VDD)を与える第1電源線と第2の外部電源電圧(VSS)を与える第2電源線間に、複数の回路からなる内部回路ブロックと電源電圧を制御するパワー制御回路を具備し、制御回路は出力MOSFET(MPP)を具備し、出力MOSFETはゲートとソースが等電圧であっても一定のオフ電流が流れるものであって、出力MOSFET(MPP)の閾値電圧は、内部回路MOSFETのそれよりも小さい。

(もっと読む)

半導体装置の保護回路およびバッファ回路

【課題】ESDサージ耐圧を高め、微細化に対応可能な保護回路を提供する。

【解決手段】ESD保護MOSトランジスタは、四角形状に形成されたドレイン領域10と、ドレイン領域10の2つの頂点部に形成されたゲートコンタクト領域41と、ドレイン領域10の残る2つの頂点部に形成されたサブコンタクト領域21と、ゲートコンタクト領域41を互いに接続しドレイン領域10を取り囲むように形成されたゲート配線44と、ドレイン領域10の辺部に形成されたゲート配線44より外側に配設されたソース領域30と、を備える。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

立ち上がり時間検出器および放電継続回路を有する静電放電保護回路

本発明の方法および素子は静電放電(ESD)保護回路を含む。この回路は、入力信号のスルーレートを検出することができ、かつ入力信号のスルーレートがしきい値よりも大きいかどうかを判定することができる立ち上がり時間依存活性化回路を含む。ESD事象の場合、立ち上がり時間依存活性化回路はトリガ信号を発生する。加えて、立ち上がり時間依存活性化回路は、ESD消散回路にさらに結合されるESD消散継続時間制御回路に結合される。この配置は、トリガ信号によってESD消散継続時間制御回路が活性化され、ESD消散継続時間制御回路は応答して活性化信号を生成し、活性化信号は、ESD消散回路を活性化し、ESD消散回路が活性状態のままであり続ける時間の長さを制御することを可能にする。ESD消散回路は、ESDエネルギーを被保護内部回路外へ経路変更するシャントを含む。ESD消散継続時間制御回路は、被保護回路を損傷することなくESDエネルギーを放電するのに十分な期間にわたってエネルギーの分流を保つようにさらに構成される。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

161 - 180 / 545

[ Back to top ]