Fターム[5F048BA01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 単層基板 (3,772)

Fターム[5F048BA01]に分類される特許

3,761 - 3,772 / 3,772

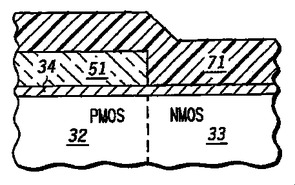

デュアルメタルゲートデバイスの形成方法

異種金属により形成されるデュアルメタルゲートを備えるMOSトランジスタ(10)を形成する方法を提供する。HfO2のようなゲート誘電体(34)を半導体基板(31)の上に堆積させる。次に、犠牲層(35)をゲート誘電体(34)を覆うように堆積させる。犠牲層(35)をパターニングして、基板(31)の第1領域(32)(例えばpMOS)の上のゲート誘電体(34)が露出し、かつ基板(31)の第2領域(33)(例えばnMOS)の上のゲート誘電体(34)が犠牲層(35)によって保護されたままになるようにする。第1ゲート導体材料(51)を残りの犠牲領域(35)の上に、かつ露出したゲート誘電体(34)の上に堆積させる。基板(31)の第2領域(33)の上の第1ゲート導体材料(51)がエッチングにより全て除去されるように第1ゲート導体材料(51)をパターニングする。第1ゲート導体材料(51)を取り除く際に、第2領域(33)上の犠牲層(35)は、下層の誘電体材料(34)にダメージが加わるのを防止するように機能することができる。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】近年、MOSトランジスタのウェル(基板)に順方向バイアス電圧を印加することが注目されているが、温度変化に対して最大限の順方向バイアス電圧を得ることが難しく、そのための回路構成や占有面積も問題になってきている。

【解決手段】第1導電型(p+;n+)のソース電極Sおよびドレイン電極Dとゲート電極Gとを有し、第2導電型(n;p)のウェル10;20に形成されてなるMISFET1;2を備える半導体集積回路装置であって、前記ウェル10;20の電位Vbp;Vbnを、前記MISFET1;2のソース電極Sおよび該ウェル10;20により形成されるダイオード11;21に対して所定電流Ibp;Ibnを順方向に流すことにより生成する基板バイアス回路110;111〜113を備えるように構成する。

(もっと読む)

信号伝送システム

【課題】 できるだけ従来のシステム構成と部品構成を肯定しながら、数十GHz帯のディジタル高速信号を通すための信号伝送技術を提供する。

【解決手段】 電子回路全体に渡るトランジスタの論理回路、メモリ回路に含まれるドライバ1とレシーバ2の構成において、ドライバ1は信号伝送線路3を通じてレシーバ2に、電源・グランド伝送線路4を通じて電源Vddにそれぞれ接続される信号伝送システムであって、ドライバ1およびレシーバ2は全て実質的差動入力、差動出力とし、ドライバ1の実質的差動出力の出力端では電源またはグランドへの接続を有することなく、またレシーバ2は実質的差動入力の信号の電位差を検知することで受信し、さらに信号伝送線路3は分配配線がない、構造とする。

(もっと読む)

半導体集積回路

【課題】 本発明の目的は、高速・低消費電力の半導体集積回路を提供することにある。

【解決手段】 動作状態にある回路と待機状態にある回路を混在するようにして、回路毎にバックゲート電圧を設定可能にする。

【効果】 待機時には小電流とし低消費電力性を得て、動作時には大電流として高速性を得ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

SOI基板の作製方法

【課題】 バックゲート電極を有するSOI基板を貼り合わせ法により形成する場合に、段差平坦化用polySi層の形成を不要とし、また、貼り合わせの歩留まりを向上させ、製造コストを低下させる。

【解決手段】基板貼り合わせ法によるSOI基板の作製方法において、第1の半導体基板1に段差を形成し、段差の形成面上に、所定の深さの開孔部8を有する研磨ストッパー用絶縁膜3を形成し、研磨ストッパー用絶縁膜3上にpolySiを堆積して開孔部8にpolySiを充填し、さらにディッシング防止用酸化膜9を形成し、これを平坦化することによりバックゲート電極BGを形成し、この平坦化面上に第2の半導体基板7を貼り合わせ用酸化膜10を介して貼り合わせることにより、バックゲート電極BGを有するSOI基100Aを作製する。

(もっと読む)

半導体装置

【課題】 フィールドスルー電荷補償機能を備えるアナログスイッチにおいて、半導体製造工程の誤差によらず、スィッチング用のMOSトランジスタのフィールドスルー電荷を安定に補償し、アナログスイッチ動作時の入出力間の誤差を低減できる構造を実現する。

【解決手段】 入力端子INと出力端子OUTの間に同一サイズの2つのトランジスタ1a、1bを、電気的に並列に、また物理的には相対するように配置し、トランジスタ1a、1bの入力端子IN側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ2を配置し、トランジスタ1a、1bの出力端子OUT側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ3を配置し、製造工程の誤差によって、位置ずれが発生しても、トランジスタ1a、1bのソース側の寄生容量の総和および、ドレイン側の寄生容量の総和が不変であるようにし、トランジスタ1a、1bのスィッチング動作に伴うフィールドスルー電荷の補償が、設計通りにできるようにした。

(もっと読む)

半導体装置

【課題】 消費電力が小さく、かつ動作速度が速い半導体装置を提供する。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

(もっと読む)

半導体集積回路装置

【課題】順方向基板バイアスを印加する場合に、動作温度の上昇にともなうリーク電流の増加を防止する。

【解決手段】順バイアス制御回路FBBが出力するバイアス信号は電流クランプ回路CLMPを通してCMOS回路LSIの基板へ供給される。電流クランプ回路CLMPは不純物濃度の低い拡散層を利用して構成され、温度変化に対して不変な定電流を供給する。

【効果】CMOS回路の低電圧駆動時、動作速度を順バイアスにより向上するとともに、温度上昇時、順バイアス印加にともなうリーク電流の増加を抑制し、高速かつ高信頼性を持った半導体集積回路装置を実現する。

(もっと読む)

半導体装置とその製造方法

【課題】 高耐圧MOSトランジスタの微細化を図る。

【解決手段】 P型ウエル3上にゲート酸化膜9を介して形成されたゲート電極27Fと、前記ゲート電極27Fから離間されて形成される高濃度のN型ソース・ドレイン層15と、前記ソース・ドレイン層15を取り囲むように形成され、前記ゲート電極27F下方に形成されたP型ボディ層18で分断された低濃度のN型のソース・ドレイン層10とを具備したことを特徴とする。

(もっと読む)

エンベディッドアレイを備えた半導体装置及びその製造方法並びに記録媒体

【課題】僅かな開発期間延長で、エンベディッドアレイ中のトランジスタの不要領域を削除することにより消費電力を低減する。

【解決手段】(S1)基本セルが格子状に配列されたエンベッディッドアレイを備えた半導体集積回路を設計して製造し、(S2)製造された半導体集積回路の動作が要求仕様を満たすかどうかを試験し、(S4)該動作が要求仕様を満たす場合に、コンタクトホールのレイアウトデータに基づき基本セルの不使用領域を検出して削除することにより該エンベディッドアレイのレイアウトパターンデータを修正し、(S5)修正されたレイアウトパターンのマスクを作成し、(S6)該マスクを修正前のマスクと置き換えて、不使用領域が削除された半導体集積回路を製造する。

(もっと読む)

3,761 - 3,772 / 3,772

[ Back to top ]