Fターム[5F048BA05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997) | 3層以上 (202) | 1エピ層と2エピ層が異型 (57)

Fターム[5F048BA05]に分類される特許

1 - 20 / 57

半導体装置

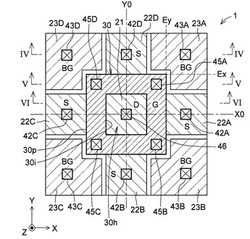

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置

【課題】サージ耐量を大きくすることが可能な半導体装置を提供する。

【解決手段】複数のフィールドプレート17b〜17eをセル部の輪郭に沿う平行方向を長手方向としてセル部から外周耐圧部の外周側に向かって複数本並べられて配置された平行部30と、該平行部30それぞれから斜め方向に延設された連結部33とを有した構成とし、平行部30と連結部33とが交互に接続されることにより、一方向に向かって階段状に形成された構造とする。そして、平行部30には、ツェナーダイオードが逆方向に直列接続されたツェナーダイオード対を複数段形成したツェナーダイオード群18a〜18eを備え、複数本並べられて配置された平行部30それぞれに備えられたツェナーダイオード対の段数がセル部に近い側からセル部の外周に向かって増やされるようにする。

(もっと読む)

双方向スイッチ及びその製造方法

【課題】トレンチゲート構造で共用ドレインを有する2つのMOS型トランジスタから構成される双方向スイッチのオン抵抗の低減を図る。

【解決手段】N型ウエル層2に複数のトレンチ3を形成する。次に前記複数のトレンチ3に挟まれたN型ウエル層2に1列おきにP型ボディ層6を形成する。複数のP型ボディ層6にはN+型第1ソース層7とN+型第2ソース層9を交互に形成する。N+型第1ソース層7を挟む1対のトレンチ3のそれぞれに第1ゲート電極5a、N+型第2ソース層9を挟む1対のトレンチ3のそれぞれに第2ゲート電極5bを形成する。第1ゲート電極5aが形成されたトレンチ3のP型ボディ層6側と反対側の側壁と第2ゲート電極5bが形成された同様の側壁に挟まれたN型ウエル層2を電界緩和層としてのN型ドレイン層11aとする。該N型ドレイン層11aを双方向スイッチのオン電流の流れる電流経路とする。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量保護ダイオードを採用した静電破壊防止用保護ダイオードからなる半導体装置において、半導体基板の表面に電圧制限素子としてのツェナーダイオード形成のための占有面積を不要とする。

【解決手段】P+型半導体基板1にP+型埋め込み拡散層1bを形成する。次に、その上をノンドープの第1エピタキシャル層4aで被覆する。次に、該第1エピタキシャル層4a上にN型の高比抵抗の第2エピタキシャル層4bを形成する。該第2エピタキシャル層4bをP+分離層6で第1保護ダイオード形成領域50と第2保護ダイオード形成領域51に分離する。第1保護ダイオード形成領域50の第1エピタキシャル層4aの表面から第1エピタキシャル層4a及び第2エピタキシャル層4bに延在するN+型埋め込み層2等を形成する。P+型埋め込み拡散層1bから延在するP+型這い上がり層1cとN+型埋め込み層2でツェナーダイオードTD等を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SUBの表面に、ソース領域SOおよびドレイン領域DRを有する高耐圧横型MOSトランジスタが完成される。そのトランジスタを平面視において取り囲む溝DTRが半導体基板SUBの表面に形成される。そのトランジスタ上を覆うように、かつ溝DTR内に中空SPを形成するようにトランジスタ上および溝DTR内に絶縁膜IIAが形成される。層間絶縁膜IIにトランジスタのソース領域SOおよびドレイン領域DRの各々に達するコンタクトホールCHが形成される。

(もっと読む)

半導体装置の製造方法

【課題】 一般的なエピタキシャルウエーハを用いて、部分SOI基板を用いた場合と同様、更にはより広範な種類のパワー素子等の縦型素子構造を組み込んだ半導体素子を安価に製造することのできる半導体装置の製造方法を提供する。

【解決手段】 P型シリコン単結晶基板に、N型エピタキシャル層と半導体エピタキシャル層を形成する工程と、半導体エピタキシャル層に半導体素子とトレンチを形成する工程と、半導体素子が形成された側の表面に保持基板を貼り合わせる工程と、N型エピタキシャル層に正電圧を印加して、N型エピタキシャル層をエッチストップ層として電気化学的エッチングによりP型シリコン単結晶基板を除去する工程と、露出した表面に絶縁膜を形成する工程と、絶縁膜のうち、縦型素子とする半導体素子が形成された領域に対応する位置の絶縁膜を除去する窓明けを行う工程と、窓明け部に、裏面電極を形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】ハイサイド素子として用いても誤動作が少なく、かつ耐圧を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が形成されている。p-エピタキシャル領域EP1の主表面側には、p-エピタキシャル領域EP2が形成されている。p-エピタキシャル領域EP2の主表面側には、n型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにフローティング電位のn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。

(もっと読む)

制御可能なサージ電流耐性を有するパワースイッチング素子

半導体スイッチング素子は、ワイドバンドギャップパワートランジスタと、前記パワートランジスタと並列に接続されたワイドバンドギャップサージ電流トランジスタと、前記サージ電流トランジスタを駆動するように構成された駆動トランジスタを含む。前記半導体スイッチング素子の、オン状態での出力電流のほぼすべては、前記パワートランジスタのドレイン−ソース電圧が第一の電圧範囲内にあるときには、前記パワートランジスタのチャネルを通って流れる。当該第一の電圧範囲は、例えば、通常動作中に期待されるドレイン−ソース電圧に対応し得る。その一方で、前記半導体スイッチング素子は、さらに、オン状態で、前記パワートランジスタのドレイン−ソース電圧が第二の(より高い)電圧範囲内にあるときには、出力電流が、前記サージ電流トランジスタ、および前記パワートランジスタのチャネルの両方を通って流れるように構成される。 (もっと読む)

半導体装置及び電力変換装置

【課題】静電容量と抵抗の値が異なる複数のスナバ回路を用意する必要がなく、且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置及び電力変換装置を提供する。

【解決手段】アノード端子300とカソード端子400からなる一対の接続端子と、一対の接続端子間に接続されたユニポーラ動作する還流ダイオード100と、一対の接続端子間に還流ダイオード100と並列接続され、少なくともキャパシタ210と抵抗220を含む半導体スナバ回路200と備え、半導体スナバ回路200のキャパシタ210と抵抗220の値が可変である。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 素子分離絶縁膜の微細化、及びMOSトランジスタの性能向上を図る。

【解決手段】

第1のMOSトランジスタと第2のMOSトランジスタを有する半導体装置において、第1のMOSトランジスタ11が形成される半導体基板100の第1の領域10と、第1の領域10に隣接され、かつ第2のMOSトランジスタ21が形成される半導体基板100の第2の領域20と、第1領域10と第2領域20の間に形成された第1の素子分離絶縁膜30と、第1領域10に形成された複数層の半導体エピタキシャル層12とを有し、第1の素子分離絶縁膜30のアスペクト比が6.7以上である半導体装置。

(もっと読む)

窒化ガリウム半導体装置およびその製造方法

【課題】回路全体の小型化を実現し、高温環境下で使用することができる窒化ガリウム半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1の表面には、絶縁層2、アンドープの第1GaN層3、AlGaN層4がこの順で積層されている。第1GaN層3とAlGaN層4の界面には、2次元電子ガスで形成された表面障壁層5が形成されている。AlGaN層4の表面層には、第1GaN層3に達し、かつ貫通しない程度の凹部(第1凹部)が形成されている。このような半導体基板1に、第1高耐圧トランジスタ110および制御回路120が一体的に形成されている。第1高耐圧トランジスタ110は、第1凹部およびAlGaN層4の表面に形成されている。また、制御回路120は、第1凹部の一部に形成されたnチャネルMOSFETと、AlGaN層4の表面に形成されたデプレッション型nチャネルMOSFETとで構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

電気回路のスイッチング装置

【課題】逆方向電流を阻止する機能を有するIGFETの逆方向耐圧の向上が要求されている。

【解決手段】スイッチング装置(10)は、逆方向電流を阻止するショットキダイオードD3を内蔵する主IGFET(11)と、保護スイッチ手段(12)と、保護スイッチ制御手段(13)とを有する。保護スイッチ手段(12)は主IGFET(11)のドレイン電極Dとゲート電極Gとの間に接続されている。保護スイッチ制御手段(13)は、主IGFET(11)に逆方向電圧が印加された時に保護スイッチ手段(12)をオンにする。これにより、主IGFET(11)が逆方向電圧から保護される。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

1 - 20 / 57

[ Back to top ]