Fターム[5F048BA20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 複数MOSの素子電極が同一平面でないもの (501) | 一部のMOSを絶縁膜上に形成 (199)

Fターム[5F048BA20]に分類される特許

141 - 160 / 199

シリコン−ゲルマニウム立体構造CMOS上の局所配線の製造方法

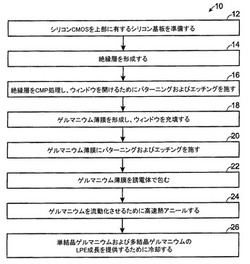

【課題】シリコン−ゲルマニウム立体構造CMOSにおいて、シリコンCMOS素子とゲルマニウムCMOS素子との間の局所配線を容易に形成する。

【解決手段】シリコンCMOS素子を有するシリコン基板を準備し(12)、該素子の上部に絶縁層を形成する(14)。上記絶縁層を部分的に開口し(16)、その上にゲルマニウム薄膜を形成する(18)。アニール処理により、上記薄膜のゲルマニウムを流動化する(24)。これにより、開口部に上記ゲルマニウムが流れ込み、該ゲルマニウムと上記シリコン基板および上記シリコンCMOS素子との間に接点が形成される。さらに冷却することで、上記ゲルマニウムがLPE成長により結晶化される(26)。そして、単結晶のゲルマニウム上にゲルマニウムCMOS素子を形成する。

(もっと読む)

半導体装置、集積回路、及び電子機器

【課題】起点部より成長させてなる結晶粒を有する半導体膜を用いたデバイスを3次元配置してなり、いずれの層に配置されたデバイスにおいても所望のデバイス特性を得ることができる半導体装置、及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、表面に複数の微細孔G11,G12を有する起点部層211と、前記微細孔G11,G12を起点として形成された略単結晶粒を含む半導体膜201,202を用いて形成されたデバイス形成層212とを備えたデバイス層101上に、同様の構成を具備したデバイス層102,103を積層してなり、前記デバイス層101〜103に属する前記微細孔(例えば微細孔G21)は、隣接して配置された他の前記デバイス層101〜103に属する前記微細孔(例えば微細孔G11,G31)から平面視で離間した位置に形成されている。

(もっと読む)

集積回路およびその形成方法(標準的直交回路のためのハイブリッド配向構造)

【課題】 標準的直交回路のためのハイブリッド配向構造のためのデバイス及び方法を提供する。

【解決手段】 本発明の実施形態の集積回路は、第1結晶配向を有する第1領域及び第2結晶配向を有する第2領域を含むハイブリッド配向基板(600)を備える。第1領域の第1結晶配向は、第2領域の第2結晶配向に平行でも垂直でもない。集積回路は、第1領域上の第1型デバイス(620)及び第2領域上の第2型デバイス(630)をさらに備え、ここで第1型デバイス(620)は、第2型デバイス(630)に平行又は垂直であり、第1型デバイス(620)は、互いに直交する第1電流(621)及び第2電流(622)を含み、第1(621)及び第2(622)電流のキャリア移動度は互いに等しい。具体的には、第1型デバイスはp型電界効果トランジスタ(PFET)を含み、第2型デバイスはn型電界効果トランジスタ(NFET)を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】チップ面積及び製造コストの増大を抑制しつつ、レーザ照射用の冗長回路を備えた半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の能動層として、本来の機能を有する回路を形成する工程と、前記第1の能動層に絶縁層を形成する工程と、前記絶縁層上に、微細孔を形成する工程と、前記微細孔が形成された絶縁層上に半導体層を形成する工程と、前記半導体層に対してレーザ照射による熱処理を行うことで、前記微細孔を起点として略単結晶化された結晶粒を形成する工程と、前記略単結晶化された結晶粒を用いて第2の能動層としてのレーザリペア用の冗長回路を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法、フォトマスク及び半導体装置

【課題】SBSI法によりSOI構造を形成する場合には、単結晶SiGe層501とSi層601とをエピタキシャル成長させた後、単結晶SiGe層501を選択的にエッチング除去することで単結晶Si層601のみを残し、単結晶Si層601とSi基板100との間を熱酸化層で埋めてSOI構造を形成する。単結晶Si層601周辺には多結晶Si層602が形成される。SiGe層501を形成すべき領域に不純物が添加されていると単結晶SiGe層501及び単結晶Si層601に欠陥が侵入し単結晶Si層601の品位を低下させる。

【解決手段】トランジスタのチャネルとなる部分を囲み単結晶Si層601が形成される領域よりも少し大きい領域が露出するようにレジストを残しイオン注入を行う。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】SBSI法によりSOIトランジスタを形成する場合に、支持体の側面開口部と平行な向きからのイオン注入に対しては支持体によりSOIトランジスタのチャネル領域がマスクされてしまうため斜めイオン注入を行っても不純物イオンはSOIトランジスタのチャネル領域には到達しない。そのため、例えばチャネル幅を広くとれる構造として、SOIトランジスタのチャネルの方向と支持体とを平行に配置した場合、寄生トランジスタの影響を抑制することが困難となり、SOIトランジスタのリーク電流が大きくなってしまうという問題点があった。

【解決手段】SOIトランジスタのチャネル部周縁部を開口し、中央部へのイオン注入を防ぐための第1不純物添加阻止層を形成した後イオン注入法を用いてチャネル部周縁部に生じる寄生トランジスタの閾値を上昇させて寄生トランジスタ起因のリーク電流を抑制する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑制しつつ、絶縁層上に配置された厚膜半導体層と薄膜半導体層とを同一基板上に形成する。

【解決手段】絶縁層12上に配置された半導体層13の薄膜SOI形成領域R1に第1半導体層21および第2半導体層22を選択的に形成し、第2半導体層22を半導体層13上で支持する支持体27を形成してから、第1半導体層21をエッチング除去して、半導体層13と第2半導体層22との間に空洞部30を形成し、半導体層13および第2半導体層22の熱酸化を行うことにより、半導体層13と第2半導体層22との間の空洞部30に埋め込み絶縁層31を形成する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】SOI構造とバルク構造とが混載された半導体基板上に形成された半導体装置を、チップサイズを増大させずに得る。

【解決手段】半導体基板10を所定の深さまでエッチングして得られた第1の領域にエピタキシャル成長にて形成され、半導体基板10の底面からの高さが半導体基板10の表面の高さと実質的に同一である半導体層60と、半導体基板10と半導体層60との間に埋め込まれた埋め込み絶縁層240と、半導体層60内の各々の素子領域間、及び、半導体層60と半導体基板10との間、を水平面内で素子分離する素子分離体と、を有する半導体基板10上に形成された半導体装置。

(もっと読む)

半導体素子の製造方法

【課題】 リセスゲート領域の素子分離構造上部にエピタキシャル層を形成し、SOIチャンネル構造の半導体素子を設計することによりチャンネル領域にイオン注入濃度を低減させ、素子のリフレッシュ、tWR及びLTRAS特性を改良することができる半導体素子の製造方法を提供する。

【解決手段】 本発明は半導体素子の製造方法に関し、特にリセスゲート領域の素子分離構造上部にエピタキシャル層を形成し、SOIチャンネル構造の半導体素子を設計することによりチャンネル領域にイオン注入濃度を低減させ、素子のリフレッシュ、tWR及びLTRAS特性を改良することができる技術である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOI構造とバルク構造との平坦性を確保しつつ、SOI構造とバルク構造とを同一基板上に形成する。

【解決手段】第2半導体層3を半導体基板1上で支持する選択酸化膜6をバルク領域R1およびSOI形成領域R2の周囲に形成した後、溝7を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、第1半導体層2をエッチング除去し、半導体基板1と第2半導体層3との間に空洞部8を形成し、導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部8内に埋め込み絶縁層9を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップサイズを低減しつつ、SOI構造とバルク構造とを同一基板上に混載する。

【解決手段】半導体基板101にはSOI形成領域R1およびバルク領域R2が設けられ、SOI形成領域R1には埋め込み絶縁層111を介して半導体層104が半導体基板101上に形成され、ゲート電極113aにて区切られたアクティブ領域107の端部には、埋め込み絶縁層111上に配置されたドレイン層114aが形成され、ゲート電極113bにて区切られたアクティブ領域107の端部には、埋め込み絶縁層111上に配置されたソース層114cが形成され、ゲート電極113cにて区切られたアクティブ領域107の端部には、半導体基板101に配置されたソース層114dが形成され、ゲート電極113a〜113cに囲まれたアクティブ領域107には、共通ソース/ドレイン層114bが配置されている。

(もっと読む)

半導体装置

【課題】基板に対して急速な加熱、冷却を行っても、基板上のSOI領域あるいはSON領域とシリコン領域との熱吸収効率の違いから生じる温度差の影響を低減でき、基板に結晶欠陥が発生するのを防止できる半導体装置を提供する。

【解決手段】半導体基板上には、シリコン領域23Bが形成され、このシリコン領域23Bを囲むように、半導体基板上に絶縁膜及び空洞のいずれか一方を介在してSOI領域22が形成されている。さらに、半導体基板上には、SOI領域22を囲むように、シリコン領域23Aが形成されている。

(もっと読む)

半導体集積回路装置

【課題】 完全空乏型SOIデバイス構造を有するパワーマネージメント半導体装置やアナログ半導体装置において、ESD保護素子がESD破壊強度を充分に確保しつつ内部素子のESD保護を可能とする構造を提供する。

【解決手段】 半導体薄膜層上に形成される完全空乏型SOICMOSのNMOSドレインは、一辺がソースに対向するように形成されるのに対し、ESD入出力保護素子となるNMOS保護トランジスタを半導体支持基板上に形成し、N型保護トランジスタのドレインはソースの周囲を囲うようにして形成され、ソース周囲からドレインまでの最短距離は常に一定とすることで、ESD破壊強度を充分に確保し、かつESDノイズに弱い完全空乏型SOICMOSデバイスの入出力保護、特に出力保護を可能にする構造とした。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込み絶縁層上に形成された半導体層の結晶欠陥を低減しつつ、SOI構造とバルク構造とを同一基板上に形成する。

【解決手段】Pウェル2およびNウェル12上を避けるようにしてSOI形成領域R1、R11を半導体基板1に配置するとともに、Pウェル2およびNウェル12にはバルク領域R2、R12をそれぞれ配置し、SOI形成領域R1、R11には、Nチャンネル電界効果型SOIトランジスタおよびPチャンネル電界効果型SOIトランジスタをそれぞれ形成し、バルク領域R2、R12には、Nチャンネル電界効果型バルクトランジスタおよびPチャンネル電界効果型バルクトランジスタをそれぞれ形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、アナログ回路とデジタル回路とを同一基板上に混載する。

【解決手段】半導体基板11上にアナログ回路を形成した後、凹部32が形成された絶縁膜31をアナログ回路上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34にデジタル回路を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、サリサイド化された素子と非サリサイド化された素子とを同一基板上に混載する。

【解決手段】シリサイド層19a、19b、19cが設けられたソース/ドレイン層17a、17bおよびゲート電極14を半導体基板11に形成した後、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34に非サリサイド素子を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PチャンネルトランジスタとNチャンネルトランジスタとを異なる半導体層上に混載することにより、伝播遅延の増大を抑制しつつ、全体のプロセス長さを大幅に短縮する。

【解決手段】半導体基板11上にNチャンネルトランジスタ(Pチャンネルトランジスタ)を形成した後、凹部32が形成された絶縁膜31をNチャンネルトランジスタ(Pチャンネルトランジスタ)上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34にPチャンネルトランジスタ(Nチャンネルトランジスタ)を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、外部インターフェース回路が搭載された集積回路の低電圧化を図る。

【解決手段】半導体基板11上に集積回路を形成した後、凹部32が形成された絶縁膜31を集積回路上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34に外部インターフェース回路を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】キャリアの異なる2種類のトランジスタについてエクステンション層の構造を最適化することにより、2種類のトランジスタについて不純物の拡散を同等に抑制した半導体装置およびその製造方法を提供する。

【解決手段】pMOSトランジスタは、半導体基板1上にゲート絶縁膜4を介して形成されたゲート電極5と、ゲート電極5の両側における半導体基板1上に形成され、p型不純物を含有するp型エクステンション層11pとを有する。nMOSトランジスタは、半導体基板1上にゲート絶縁膜4を介して形成されたゲート電極5と、ゲート電極5の両側における半導体基板1上に形成され、n型不純物を含有するn型エクステンション層とを有する。p型エクステンション層11pは、n型エクステンション層11nに比べて厚く形成されている。

(もっと読む)

薄層SOIトランジスタに埋め込まれた歪み層ならびにその形成法

埋め込み絶縁層(103、203)を介して深いリセス(111、211)を形成し、歪み半導体材料(112、212)を再成長させることで、強化された歪み生成メカニズムがSOIのようなトランジスタ(100、200)に提供される。したがって、歪みはさらにアクティブ層の全体にわたって埋め込まれた歪み半導体材料により実効的に生成され、これにより、2つのチャネル領域が画定され得るトランジスタデバイスの性能を実質的に向上させることができる。  (もっと読む)

(もっと読む)

141 - 160 / 199

[ Back to top ]