Fターム[5F048BA20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 複数MOSの素子電極が同一平面でないもの (501) | 一部のMOSを絶縁膜上に形成 (199)

Fターム[5F048BA20]に分類される特許

61 - 80 / 199

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】格子定数が異なる複数種類の半導体素子やスピン機能素子を同一の基板上の同一の層上に混載することが可能な半導体装置の製造方法を提供しようとする。

【解決手段】シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜に開口部を設け、前記シリコン基板の一部を露出させる工程と、前記露出したシリコン基板及び前記絶縁膜上にGeを含むアモルファスの第1の半導体層を形成する工程と、前記第1の半導体層を第1の方向に延伸した構造に加工する工程と、前記第1の方向に延伸した第1の半導体層に熱処理を加えて、前記開口部から離れるにしたがってSiの濃度が減少する第1のSi1-xGex(0≦x≦1)層を形成する工程と、を含む。

(もっと読む)

半導体装置

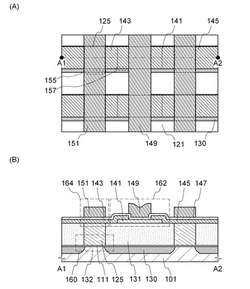

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

共通基板上にカラムIII−VトランジスタとともにシリコンCMOSトランジスタを有する半導体構造

半導体構造は、ある結晶方位を有するシリコン基板(12)と、シリコン基板(12)の上方に配置された絶縁性層(18/22)と、絶縁性層の上方に配置され、基板の結晶方位とは異なる結晶方位を有するシリコン層(20)と、シリコン基板上に配置され、基板と同じ結晶方位を有するカラムIII−Vトランジスタデバイス(34)とを有する。一実施形態では、カラムIII−Vトランジスタデバイスが、基板と接触する。別の実施形態では、デバイスは、GaNデバイスである、または基板の結晶方位が<111>であり、シリコン層の結晶方位が<100>である。一実施形態では、CMOSトランジスタが、シリコン層内に配置される。一実施形態では、カラムIII−Vトランジスタデバイスが、カラムIII−Nデバイスである。一実施形態では、カラムIII−Asデバイス、カラムIII−Pデバイス、またはカラムIII−Sbデバイスが、<100>シリコン層の上面上に配置される。  (もっと読む)

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングトランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチングトランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半導体装置である。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

HOT(hybridorientationtechnology)を選択的エピタキシーに関連して用いて移動度を改善する方法およびそれに関連する装置

半導体装置が、第1の基板(102、202)と、第1の基板の第1の部分の上に位置し、埋め込み層(104、204)によって第1の基板から分離される第2の基板とを含む。この半導体装置はまた、第1の基板の第2の部分の上に位置し、第2の基板から隔離されるエピタキシャル層(108、220)を含む。この半導体装置はさらに、少なくとも部分的に第2の基板内に形成される第1のトランジスタ(116)と、少なくとも部分的にエピタキシャル層内またはその上に形成される第2のトランジスタ(128)とを含む。第2の基板およびエピタキシャル層は、異なる電子および正孔移動度を有するバルク特性を有する。トランジスタの少なくとも1つは、少なくとも約5Vの1つまたは複数の信号を受け取るように構成される。第1の基板は第1の結晶面方位を有し、第2の基板は第2の結晶面方位を有し得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 固相エピタキシャル成長によって、所望の面方位を有する結晶を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、第1の面方位を有するシリコン基板11上の一部に、アモルファス層13を形成する工程と、そのアモルファス層13にマイクロ波を照射し、前記アモルファス層13を第1の面方位を有する結晶層とする工程とを有していることを特徴とする半導体装置の製造方法を提供することができる。

(もっと読む)

61 - 80 / 199

[ Back to top ]