Fターム[5F048BA20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 複数MOSの素子電極が同一平面でないもの (501) | 一部のMOSを絶縁膜上に形成 (199)

Fターム[5F048BA20]に分類される特許

41 - 60 / 199

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

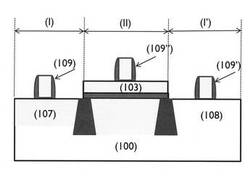

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン層又はシリコン基板に補償ドープのために不純物を注入する必要がなく、安定的に高調波歪を低減する。

【解決手段】第1絶縁層20は、シリコン基板10上に形成されており、当該シリコン基板10に接している。また、配線40は、第1絶縁層20上に形成されている。ここで、第1絶縁層20下の不純物濃度は、2.0×1014cm−3以下である。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】本発明は、接続不良を抑制したコンタクト形成方法を備える半導体装置を提供するものである。

【解決手段】半導体装置は、配線層を備える第1の回路領域と、第1の回路領域の上に形成された絶縁膜と、絶縁膜の上に形成され、シリサイド膜を備える第2の回路領域と、配線層上に設けられ、配線層と電気的に接続された下部コンタクトと、下部コンタクト上に設けられ、下部コンタクトと前記シリサイド膜とを電気的に接続する上部コンタクトとを有する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン層の表面平坦性を向上できる半導体装置の製造方法を提供する。

【解決手段】本実施形態によれば、半導体装置の製造方法は、基板上に非晶質シリコン膜を形成する工程と、前記非晶質シリコン膜を結晶化して多結晶シリコン膜を形成する工程と、プラズマドーピング法を用いて、前記多結晶シリコン膜にイオンを注入する工程と、前記イオンを注入した前記多結晶シリコン膜の表面を研磨する工程と、を備える。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

41 - 60 / 199

[ Back to top ]