Fターム[5F048BA20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 複数MOSの素子電極が同一平面でないもの (501) | 一部のMOSを絶縁膜上に形成 (199)

Fターム[5F048BA20]に分類される特許

181 - 199 / 199

集積回路およびその製造方法

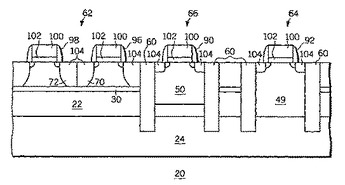

集積回路およびその製造方法が提供されている。集積回路(20)は、その結晶方位が<100>である第1領域(64、66)とその結晶方位が<110>である第2領域(66、64)を有するバルクシリコン基板(24)を含む。シリコンオンインシュレータの層(62)はバルクシリコン基板の一部を覆う。少なくとも1つの電界効果トランジスタ(96、98)はシリコンオンインシュレータの層(62)上に形成され、少なくとも1つのPチャネル電界効果トランジスタ(90、92)はその結晶方位が<110>である第2領域(66、64)に形成され、少なくとも1つのNチャネル電界効果トランジスタ(90、92)はその結晶方位が<100>である第1領域(64、66)に形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 複数のMOSFETを異なる面方位を有する基板上に形成する。

【解決手段】 半導体装置の基板を、第1面方位を有する第1シリコンと、第1シリコンの一部に形成された埋め込み絶縁膜と、埋め込み絶縁膜上に形成された、第2面方位を有する第2シリコンとを有するものとする。そして、第1シリコン上に、第1ゲート電極を含む第1トランジスタを形成し、第2シリコン上に、第2ゲート電極を含む第2トランジスタを形成する。このとき、第1シリコン膜表面と、第2シリコン膜表面との高さの差は、第1ゲート電極又は第2ゲート電極のゲート長よりも小さいものとする。あるいは、ここで、第1ゲート電極表面の第1シリコン表面からの高さは、第2ゲート電極表面の第1シリコン表面からの高さと同じであるようにする。

(もっと読む)

基板の製造方法

【課題】平坦性が向上されたSOI領域とバルク領域とを有する基板を提供する。

【解決手段】パターンドSOI基板100の製造プロセスにおいてバルク領域103にあらかじめエッチングによって段差を作り、パターンドSOI基板100を形成する工程において、シリコン基板104表面の段差を低減することで、シリコン基板表面の段差が発生するために確保することが困難であった露光時のフォーカスマージンを確保する。

(もっと読む)

ファセットチャンネルを有する半導体素子及びその製造方法

【課題】ファセットチャンネルを有する半導体素子を提供し、その製造方法をも提供する。

【解決手段】半導体素子は第1及び第2活性領域を有する半導体基板を備える。前記第1及び第2活性領域はそれぞれ第1及び第2主表面を有し、前記第1及び第2主表面は第1結晶方位を有する。前記第2主表面から成長したファセットエピタキシャル半導体構造が提供される。前記ファセットエピタキシャル半導体構造は第2結晶方位を有する少なくとも1つのファセットを備える。前記第1主表面及び前記ファセットエピタキシャル半導体構造上にゲート誘電層が提供される。前記第1主表面上の前記ゲート誘電層上に第1ゲート電極が配置され、前記ファセットエピタキシャル半導体構造上の前記ゲート誘電層上に第2ゲート電極が配置される。また、前記半導体素子の製造方法をも提供する。

(もっと読む)

複数のスタックしたハイブリッド方位層を含む半導体装置および半導体装置の形成方法

第1結晶方位を有する基板18を含む半導体装置が提供される。基板18上には第1絶縁層14が重なり、第1絶縁層14上には複数のシリコン層が重なる。第1シリコン層42は、第2結晶方位および結晶面を有するシリコンを含む。第2シリコン層25は、第2結晶方位と、第1シリコン層42の平面に対して実質的に直角である結晶面を有する。正孔移動度は(110)面においてより高いので、半導体装置のパフォーマンスは、特定の結晶面方位を有するシリコン層を選択することで高めることができる。

さらに、半導体装置の形成法が提供される。第1結晶方位を有し、第1絶縁層14が上に形成された第1シリコン基板18と、第1絶縁層14上に重なる、第2結晶方位および結晶面を有する第1シリコン層19とを含むシリコン・オン・インシュレータ構造は、第2シリコン基板20に結合される。第2シリコン基板20は第2結晶方位および結晶面を有し、第2絶縁層24がその上に形成される。第2シリコン基板20は、水素イオンを第2シリコン基板20に注入することで生成される線欠陥22を含む。第2シリコン基板20の結晶面は、第1シリコン層19の結晶面に対して実質的に直角に方向付けられる。第2シリコン基板20は線欠陥22に沿って分離されるとともに除去され、第2絶縁層24および第2シリコン層25がシリコン・オン・インシュレータ構造上に残る。次に、シリコン・オン・インシュレータ構造を異なる結晶方位からなるシリコン層にまで選択的にエッチングし、エッチングした領域に選択的エピタキシャルシリコン層を成長させ、その後、シリコン・オン・インシュレータ構造を化学機械研磨によって平坦化することによって、異なる結晶方位を有する複数のデバイスを単一のプレーナシリコン・オン・インシュレータ構造上に形成することができる。  (もっと読む)

(もっと読む)

自己整合ダブルゲートデバイス及びその形成方法

【課題】デバイス性能を向上させるだけでなく、製造工程を簡素化する新しいデバイス構造とダブルゲートデバイス形成工程を提供する。

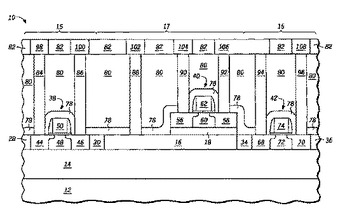

【解決手段】ダブルゲートデバイスの形成方法において、約30nm未満の厚さを有している埋込絶縁層14が第1基板上12に形成される。第2基板は埋込絶縁層上に形成される。パッド層は第2基板を覆うように形成される。マスク層はパッド層を覆うように形成される。第1溝は、パッド層,第2基板,埋込絶縁層を貫いて、基板12内に延びるように形成される。第1溝は、第1分離部26で充填される。第2溝は、第1分離部26内に形成され、導電材料で充填される。MOS型トランジスタは第2基板上に形成される。下部ゲート50は、埋込絶縁層の下に形成され、第2基板上に形成された上部ゲート36に対して自己整合される。

(もっと読む)

複合表面配向基板をもつトレンチ・キャパシタ

【課題】 複合表面配向基板をもつトレンチ・キャパシタを形成する方法を提供する。

【解決手段】 複合表面配向をもつ単一のチップ上に、ディープ・トレンチ・キャパシタ記憶デバイス及び論理デバイスを形成する方法が開示される。この方法は、(100)表面配向シリコン上のn型相補型金属酸化膜半導体(CMOS)デバイスSOIアレイ及び論理トランジスタ、並びに(110)表面配向シリコン上のp型CMOS論理トランジスタを含んだ、高性能なシステム・オン・チップ(SoC)を製造することを可能にする。さらに、この方法は、複合表面配向SOI及びバルク基板の内部にシリコン基板トレンチ・キャパシタを作成することを可能にする。アレイ・マスクの開口及びシリコンのエピタキシャル成長のためのパターン付けが、同じステップで同じマスクを用いて達成される点で、コスト節減が実現される。

(もっと読む)

基板の製造方法および半導体装置の製造方法

【課題】第2半導体層の側壁に絶縁膜を形成して、第1半導体層の結晶方位を引き継いだエピタキシャル成長層を形成することで、結晶方位(100)の半導体層と結晶方位(110)の半導体層を同一基板上に結晶欠陥を抑制して形成することを可能とする。

【解決手段】第1半導体層11と絶縁層12と第2半導体層13とを順に積層した基板を用い、第2半導体層13上に酸化膜エッチング時の耐性と耐酸化性とを有するマスク層15を形成する工程と、第1領域のマスク層15から絶縁層12までを第1半導体層11上に残して第2領域の第1半導体層11を露出させる工程と、第1半導体層11表層と第2半導体層13の露出した側壁を酸化する工程と、マスク層15をエッチングマスクに用いて酸化層21を除去し、第1半導体層11を露出させる工程と、露出された第1半導体層11上にエピタキシャル成長層17を形成する工程とを備えた製造方法である。

(もっと読む)

結晶方向の異なるシリコン層を備えたシリコン−オン−インシュレータ半導体デバイスと、シリコン−オン−インシュレータの半導体デバイスを形成する方法

第1の結晶方位を有する基板12と、この基板12を覆う絶縁層40を含む半導体デバイスが提供される。この絶縁層を覆って、複数のシリコン層16、30が形成される。第1シリコン層16は、第1の結晶方位を有するシリコンを含み、第2シリコン層30は、第2の結晶方位を有するシリコンを含む。加えて、基板12と、この基板12を覆うシリコン層16と、基板12とシリコン層16と間に設けられた第1絶縁層14を含むシリコン−オン−インシュレータ構造を提供する半導体デバイスを形成する方法が提供されている。シリコン層16および第1絶縁層14の一部を取り除くことでシリコン−オン−インシュレータ構造の第1領域を形成し、基板層12の一部24をさらす。選択的エピタキシャルシリコン30は、開口部に成長される。開口部22で成長されたシリコン30に第2絶縁層40が形成され、開口部22で成長されたシリコン30と基板12との間に絶縁層40が提供される。  (もっと読む)

(もっと読む)

FINFETと一体化した平坦基板デバイス及びその製造方法

【課題】 FINFETと一体化した平坦基板デバイス及びその製造方法を提供すること。

【解決手段】 フィン型電界効果トランジスタ(FinFET)と一体化した平坦基板デバイス(100)、及び、その製造方法は、基板(103)と、基板(103)上の埋め込み分離層(105)と、埋め込み分離層(105)上の半導体層(115)と、を含むシリコン・オン・インシュレータ(SOI)ウエハ(101)を含む。構造体(100)は、さらに、埋め込み分離層(105)上のFinFET(130)と、基板(103)に一体化された平坦型電解効果トランジスタ(FET)(131)と、を含み、FETゲート(127)は、FinFETゲート(125)に対して高さの違いは極くわずかである。構造体(100)は、さらに、基板(103)に構成された逆型ウェル領域(104、106、108、110)を含む。一実施形態においては、構造体(100)は、さらに、基板(103)に構成された浅いトレンチ分離領域(111)を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】正孔または電子の移動度を高めるとともに、NMOS領域とPMOS領域との表面の段差を抑制することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明は、NMOS領域AとPMOS領域Bとを同一の基板11に備えた半導体装置であって、NMOS領域Aの基板11上に設けられるとともに、基板11の表面と異なる面方位を有する歪みSi層21と、PMOS領域Bの基板11上に設けられるとともに、基板11の表面と同じ面方位を有する歪み層からなる歪みSiGe層31とを備えたことを特徴とする半導体装置およびその製造方法である。

(もっと読む)

液晶パネル用基板及び液晶パネル

【課題】アモルファスシリコンTFTを用いた画素領域に、多結晶シリコンTFTを用いたドライバ領域とを一枚の基板に形成することができる液晶パネル用基板及び液晶パネル並びにその製造方法を提供する。

【解決手段】第1の基板10上の画素領域12に、アモルファスシリコンTFT30を形成し、端子となる部分を露出させて第1の電極露出部22とする。第2の基板100を用いて、駆動回路14,16の能動素子である多結晶シリコンTFTと、それに接続された第2の電極配線群を含む被転写層140を形成し、端子となる部分を露出させて第2の電極露出部141とする。この第1,第2の電極露出部22,141が導通する位置関係にて、第1の基板10上に被転写層140を接合した後、被転写層140より第2の基板100を除去する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 半導体層の結晶品質を良好に保ちつつ、互いに異なる膜厚を有する半導体層を絶縁層上に形成する。

【解決手段】 厚膜半導体領域R2の第1単結晶半導体層12a、12bをエッチング除去するとともに、薄膜半導体領域R3の第1単結晶半導体層12c、12dをエッチング除去し、厚膜半導体領域R2の第2単結晶半導体層13aおよび薄膜半導体領域R3の第2単結晶半導体層13cが消失するまで、半導体基板11、第2単結晶半導体層13a〜13dおよび支持体16の熱酸化を行うことにより、厚膜半導体領域R2の第2単結晶半導体層13bおよび薄膜半導体領域R3の第2単結晶半導体層13d下に絶縁層を形成する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 互いに異なる膜厚を有する絶縁層上に半導体層を形成する。

【解決手段】 第2単結晶半導体層13a、13b間の第1単結晶半導体層12a、12bを除去することにより、第2単結晶半導体層13a、13b間に空洞部17を形成した後、厚膜化BOX層領域R2の第2単結晶半導体層13aが消失するまで、半導体基板11、第2単結晶半導体層13a、13bおよび支持体16の熱酸化を行うことにより、第2単結晶半導体層13b下に絶縁層18を形成し、厚膜化BOX層領域R2と薄膜化BOX層領域R3とで第2単結晶半導体層13b下の絶縁層18の膜厚を異ならせる。

(もっと読む)

半導体集積回路装置

【課題】 完全空乏型SOIデバイス構造を有するパワーマネージメント半導体装置やアナログ半導体装置において、ESD保護素子がESD破壊強度を充分に確保しつつ内部素子のESD保護を可能とする構造を提供することを目的とする。

【解決手段】 半導体薄膜層上に形成される完全空乏型SOICMOSのNMOSのゲート電極の導電型がN型であるのに対し、ESD入出力保護素子となるNMOS保護トランジスタを半導体支持基板上に形成し、ゲート電極の導電型をP型とすることで、ESD破壊強度を充分に確保し、かつESDノイズに弱い完全空乏型SOICMOSデバイスの入出力保護、特に出力保護を可能にする構造とした。

(もっと読む)

特徴の異なる結晶性半導体領域を有する基板の形成技術

第1結晶性半導体領域104a内に誘電領域111を形成することによって、単一基板上に異なるタイプの結晶性半導体領域が与えられる。その後、この誘電領域111上には、第2結晶領域152aがウェハ接合技術によって位置決めされる。好ましい実施形態では、誘電領域とともに、第1結晶領域にアイソレーション構造が形成されてもよい。特に、結晶方向の異なる結晶性半導体領域が形成されてもよく、高度なフレキシビリティと、現在利用されているCMOSプロセスとの互換性が維持される。  (もっと読む)

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

ローカルSOIを備えた半導体装置を形成するための方法

半導体・オン・インシュレータ・トランジスタ45が、バルクのシリコン基板12から形成される。活性領域は基板12上に画定され、単結晶である酸素リッチ型シリコン層は活性領域の頂部面に形成される。この酸素リッチ型シリコン層の上に、シリコンのエピタキシャル層が成長する。シリコンのエピタキシャル層が形成された後に、酸素リッチ型シリコン層が、該エピタキシャル層の少なくとも一部を単結晶シリコンとして残した状態にてシリコン酸化物24に変換される。これは、高温水蒸気をエピタキシャル層に適用することにより実施される。得られたものがトランジスタ45を形成するのに有用なシリコン・オン・インシュレータ構造体10であり、該トランジスタにおいて、ゲート誘電体26が残りの単結晶シリコン上に存在し、該ゲート28はゲート誘電体26上に存在し、かつ、ゲート28の下側にある残りの単結晶シリコン内にチャネル36が存在する。  (もっと読む)

(もっと読む)

スタック状テンプレート層の局部的なアモルファス化及び再結晶化によって形成される、選択された半導体結晶配向を有するプレーナ型基板

【課題】 異なる配向の半導体が共通のBOX層上に配置された、プレーナ型ハイブリッド配向半導体基板構造体を形成するための、より簡単で優れた方法を提供すること。

【解決手段】 異なる結晶配向の半導体層を有するプレーナ型基板を製造するための、スタック状テンプレート層の局部的なアモルファス化及び再結晶化を用いる方法が提供される。本発明の方法を用いて構築されるハイブリッド配向半導体基板構造体、及び、デバイスの性能を高めるために異なる表面配向上に配置された少なくとも2つの半導体デバイスを含む種々のCMOS回路と一体化されたこうした構造体が提供される。

(もっと読む)

181 - 199 / 199

[ Back to top ]