Fターム[5F048BA20]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 複数MOSの素子電極が同一平面でないもの (501) | 一部のMOSを絶縁膜上に形成 (199)

Fターム[5F048BA20]に分類される特許

81 - 100 / 199

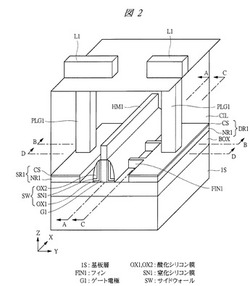

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置の製造方法

【課題】 一般的なエピタキシャルウエーハを用いて、部分SOI基板を用いた場合と同様、更にはより広範な種類のパワー素子等の縦型素子構造を組み込んだ半導体素子を安価に製造することのできる半導体装置の製造方法を提供する。

【解決手段】 P型シリコン単結晶基板に、N型エピタキシャル層と半導体エピタキシャル層を形成する工程と、半導体エピタキシャル層に半導体素子とトレンチを形成する工程と、半導体素子が形成された側の表面に保持基板を貼り合わせる工程と、N型エピタキシャル層に正電圧を印加して、N型エピタキシャル層をエッチストップ層として電気化学的エッチングによりP型シリコン単結晶基板を除去する工程と、露出した表面に絶縁膜を形成する工程と、絶縁膜のうち、縦型素子とする半導体素子が形成された領域に対応する位置の絶縁膜を除去する窓明けを行う工程と、窓明け部に、裏面電極を形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィントランジスタの素子分離膜中にボイドが発生しにくい構造の半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の基準面103及び第1の基準面103よりも高い位置に設けられた第2の基準面104を有するシリコン基板100を備えている。シリコン基板100の上には、互いに間隔をおいて、上面が第2の基準面103よりも高い位置にあり、フィントランジスタを構成するフィン121及びフィン122が形成されている。第1の基準面103の上には、上面がフィン121及びフィン122の上面よりも低い位置にある第1の素子分離膜131Aが形成されている。第1の基準面103を挟んで隣接する2つのフィン121の間隔は、第2の基準面104を挟んで隣接する2つのフィン122の間隔よりも広い。

(もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上10−1に、チャネル長方向が<−110>方向に沿って配置される絶縁ゲート型電界効果トランジスタpMOSと、前記半導体基板における素子分離領域の溝内に埋め込まれ、正の膨張係数を有し、前記絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加える第1素子分離絶縁膜11−1とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置

【課題】本発明は、SOI基板を用い、1枚の基板上に実際の装置に独立して適用可能なドライバ機能を搭載した半導体装置を提供することを目的とする。

【解決手段】支持シリコン基板31の上面に酸化膜32が積層され、該酸化膜32の上面に活性シリコン層33が積層されたSOI基板30、30a、30bに形成された半導体装置50、50a〜50dであって、

前記SOI基板30、30a、30bの表面40は、前記支持シリコン基板31が露出した支持シリコン基板露出領域41と、前記活性シリコン層33が形成された活性シリコン層領域42、43とを有し、

前記支持シリコン基板露出領域41又は前記活性シリコン層領域42、43の一方には出力回路10、10a〜10eが形成され、他方には該出力回路10、10a〜10eを駆動制御する制御回路20、20a〜20dが形成されたことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

照度センサおよびその製造方法

【課題】SOI構造の半導体基板に形成された1チップ化された照度センサの感度のバラツキを抑制する手段を提供する。

【解決手段】シリコン基板と、シリコン基板上に形成された埋込み酸化膜と、埋込み酸化膜上に形成されたシリコン半導体層とを有する半導体基板に形成された照度センサであって、シリコン半導体層に形成された信号処理回路と、シリコン基板に形成された可視光感光素子とを備え、可視光感光素子の受光部上の採光部の周囲のシリコン半導体層に、遮光膜を設ける。

(もっと読む)

半導体構造の製造方法およびこの方法により得られる半導体構造

好ましい実施形態において、本発明は、半導電性支持体と、支持体の一部分上に配置された絶縁層と、絶縁層上に配置された半導電性表層とを有する半導体構造を提供する。表層と、絶縁層により覆われていない基板の半導電性バルク領域の露出部分とに電子デバイスが形成され得る。本発明はまた、連続した絶縁層上に配置された半導電性表層を含み、半導電性支持体上に両層が配置された基板から始まり、基板の露出された半導電性バルク領域を形成するように基板の少なくとも1つの選択領域を変形することによって、このような半導体構造を作製する方法を提供する。 (もっと読む)

半導体装置

【課題】大型絶縁基板に非単結晶Si半導体素子と単結晶Si半導体素子とを形成し、高性能なシステムを集積化した半導体装置を製造する場合に、単結晶Si部分の製造工程を簡略化し、かつ大型絶縁基板に転写した後、高精度のフォトリソグラフィなしに微細な単結晶Si半導体素子の素子分離を実現し得る半導体基板、半導体装置、及びそれらの製造方法を提供する。

【解決手段】チャネル領域17、ソース領域4及びドレイン領域5を含む活性層6を有し、ウエル構造及びチャネルストップ領域を有しない単結晶Siウエハ8と、単結晶Siウエハ8上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極2と、活性層6の周囲の単結晶Siウエハ8上に形成された、ゲート絶縁膜3よりも膜厚の厚いLOCOS酸化膜7と、ゲート電極2及びLOCOS酸化膜7上に形成された平坦化絶縁膜1を有する。

(もっと読む)

改良されたキャリア移動度を有するマルチゲート半導体デバイスの製造方法

【課題】フィンベース半導体デバイスにおいて、最適なキャリア移動度を有するデバイスを提供する。

【解決手段】基板を提供する工程であって、基板510は、少なくとも第1キャリア移動度増加パラメータを有する第1半導体層551と、第1半導体層の上の埋め込み絶縁層530と、埋め込み絶縁層の上の少なくとも第2キャリア移動度増加パラメータを有する第2半導体層520とを含み、第2キャリア移動度増加パラメータは第1キャリア移動度増加パラメータとは異なる工程と、基板の第1活性領域と第2活性領域を形成する工程であって、第1活性領域は、第2活性領域から電気的に分離される工程と、を含む。

(もっと読む)

半導体装置の製造方法及び混成トランジスタ用半導体装置の製造方法

【課題】MOSトランジスタの寄生抵抗の低減化を図るとともに、ソース・ドレイン領域及びエクステンション部を構成するエピタキシャル成長領域の安定化を図った半導体装置の製造方法を得る。

【解決手段】ポリシリコンゲート5の側面にオフセット部をオフセットスペーサ用酸化膜31及びオフセットスペーサ用窒化膜32の2層構造で形成し、さらにその側面にサイドウォール用酸化膜33及びダミーサイドウォール用窒化膜を形成した後、当該ダミーサイドウォール用窒化膜を熱燐酸を用いて除去する。その結果、選択エピ成長領域12とポリシリコンゲート5との間に段差部19が形成される。そして、ポリシリコンゲート5、上記酸化膜及び窒化膜31〜33をマスクとして、ゲート外SOI領域3e、選択エピ成長領域11及び12にExt用不純物22及びHalo用不純物23を順次注入,拡散する。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】製造コストを低減しつつ、高速動作が可能な回路を有する半導体装置の作製方法を提供することを課題の一とする。または、該半導体装置を提供するための半導体基板の作製方法を提供することを課題の一とする。または、該半導体装置を用いた電子機器を提供することを課題の一とする。

【解決手段】基板上に非単結晶半導体層を形成した後、非単結晶半導体層の一部の領域上に単結晶半導体層を形成する。これにより、非単結晶半導体層を用いて大面積が必要とされる領域(例えば、表示装置における画素領域)の半導体素子を形成し、単結晶半導体層を用いて高速動作が求められる領域(例えば、表示装置における駆動回路領域)の半導体素子を形成することができる。

(もっと読む)

81 - 100 / 199

[ Back to top ]