Fターム[5F048BB08]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | シリサイド (1,994)

Fターム[5F048BB08]に分類される特許

1,981 - 1,994 / 1,994

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

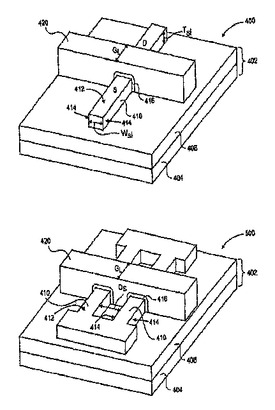

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

格子不整合エピタキシャル拡張領域ならびにソースおよびドレイン領域を有するひずみチャネルCMOSトランジスタ構造体およびその製造方法

【課題】n型電界効果トランジスタ(NFET)およびp型電界効果トランジスタ(PFET)がそれぞれ、第1の半導体の単結晶層内に配置されたチャネル領域を有し、PFETのチャネル領域には第1の大きさの応力が加えられているが、NFETのチャネル領域にはその大きさの応力が加えられていない構造体およびその製造方法を提供すること。

【解決手段】この応力は、第1の半導体とは格子不整合の第2の半導体の層によって加えられる。この第2の半導体の層は、PFETのソースおよびドレイン領域ならびに拡張領域の上の、PFETのチャネル領域から第1の距離のところに形成されており、この第2の半導体の層は、NFETのソースおよびドレイン領域の上の、NFETのチャネル領域からより大きな第2の距離のところにも形成されており、またはNFETには全く形成されていない。

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】 高耐圧MOSトランジスタの微細化を図る。

【解決手段】 P型ウエル3上にゲート酸化膜9を介して形成されたゲート電極27Fと、前記ゲート電極27Fから離間されて形成される高濃度のN型ソース・ドレイン層15と、前記ソース・ドレイン層15を取り囲むように形成され、前記ゲート電極27F下方に形成されたP型ボディ層18で分断された低濃度のN型のソース・ドレイン層10とを具備したことを特徴とする。

(もっと読む)

1,981 - 1,994 / 1,994

[ Back to top ]