Fターム[5F048BC11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | ソース・ドレイン下に絶縁層 (58)

Fターム[5F048BC11]に分類される特許

1 - 20 / 58

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

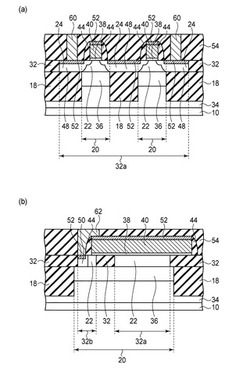

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】 固相エピタキシャル成長によって、所望の面方位を有する結晶を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、第1の面方位を有するシリコン基板11上の一部に、アモルファス層13を形成する工程と、そのアモルファス層13にマイクロ波を照射し、前記アモルファス層13を第1の面方位を有する結晶層とする工程とを有していることを特徴とする半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】柱状半導体層の周囲にゲート電極が形成される縦型トランジスタにおいては、各々の縦型トランジスタのゲート長より大きいゲート長を持つトランジスタを形成することが困難である。

【解決手段】基板上に形成された第1の拡散層上に2個の柱状半導体層によって形成された縦型トランジスタが隣接して形成されており、それらの縦型トランジスタは共通なゲート電極を備え、第1の柱状半導体層の上部に形成された第1の上部拡散層はソース電極に接続され、第2の柱状半導体層の上部に形成された第2の上部拡散層はドレイン電極に接続され、2個の縦型トランジスタが直列に接続されることによって、各々の縦型トランジスタの2倍のゲート長を持つトランジスタとして機能することを特徴とする半導体装置を提供する。

(もっと読む)

フローティングボディー効果を利用した磁気抵抗メモリセル、これを含むメモリ素子及びその動作方法

【課題】高集積の磁気抵抗メモリ素子に必要な選択トランジスタの電流駆動能力をフローティングボディー効果によって向上させた磁気抵抗メモリセル、これを含む磁気抵抗メモリ素子及びその動作方法を提供する。

【解決手段】磁気抵抗メモリセルは、磁気トンネル接合素子及び選択トランジスタを含む磁気抵抗メモリセルであり、選択トランジスタは、第1導電型の半導体層101;半導体層101上にゲート絶縁膜22を介して形成されたゲート電極20;半導体層101内に相互離隔して形成され、第2導電型を持つ第1及び第2拡散領域40;を含む。ここで、第1及び第2拡散領域40の間の半導体層101の一部が電気的にフローティングされたボディー領域103に形成される。本発明によれば、フローティングボディー効果を利用した高性能の選択トランジスタを適用することで、磁気抵抗メモリ素子の高集積化を達成することができる。

(もっと読む)

半導体装置

【課題】歪みシリコン技術を用いて効果的に駆動力を向上させた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板上に形成された半導体層と、前記半導体層内にソース・ドレイン領域およびチャネル領域を有するトランジスタと、前記半導体基板と前記半導体層の間の、前記チャネル領域の下方に形成され、前記チャネル領域に歪みを発生させる応力を内包した絶縁膜と、を備える。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置

【課題】ドレイン・オン電流値のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。また、本発明は、ドレイン電流のスイッチング比のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。

【解決手段】複数本のカーボンナノチューブをチャネルに用いる電界効果型トランジスタを二つ以上用いている半導体装置において、前記電界効果型トランジスタのドレイン・オン電流値のばらつきがσ1(オン電流値の標準偏差を平均値で割ったもの)のとき、各電界効果型トランジスタチャネルのカーボンナノチューブの本数Nが、N>31×σ1-1なる式(1)の関係を満たすことを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗をさらに低減する疑似SOI構造の半導体装置の提供。

【解決手段】第1および第2のゲート側壁絶縁膜23WA〜23WDをマスクに、前記側壁絶縁膜のそれぞれ外側に、第1および第2の凹部21TA〜21TDを形成する工程と、前記側壁絶縁膜のそれぞれ外側に、第1および第2のダミー側壁膜を形成する工程と、前記ダミー側壁膜23DA〜23DDをマスクに、前記シリコン基板のうち、前記凹部における露出部分を酸化し、それぞれ第1および第2のシリコン酸化膜を形成する工程と、前記凹部に第1および第2のシリコン膜を充填する工程と、前記シリコン膜上に金属膜を堆積し、熱処理することにより、シリサイド領域が側壁絶縁膜の外端を超えて、前記ゲート電極23A,23B直下の領域近傍にまで到達するようにシリサイド領域を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタの小型化、及びそれに伴って増加する寄生抵抗、寄生容量を低減すること。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成されるドレイン又はソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成されるソース又はドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部とを接続するシリサイド層が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】縦型MOSトランジスタの高集積化、高性能化。

【解決手段】基板上の絶縁膜上に平面状半導体層及び複数の平面状半導体層上の柱状半導体層を形成し、平面状半導体層を素子に分離し、平面状半導体層に不純物領域を形成し、その後に表面の少なくとも一部に絶縁膜を形成し、絶縁膜上に導電膜を形成し、絶縁膜及び前記導電膜をエッチバックし、柱状半導体層側面の絶縁膜及び導電膜を所望の長さに形成し、ゲート電極を形成し、導電膜及び絶縁膜を選択的にエッチングにより除去し、ゲート電極及び前記ゲート電極から延在するゲート配線を形成し、複数の柱状半導体層の各々に対応する複数のMOSトランジスタのうち、第1のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部とを接続する第1のシリサイド層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型MOSトランジスタの小型化、それに伴い増加する寄生抵抗、寄生容量の低減。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成される第1のドレイン/ソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成される第2のソース/ドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1又は第2のMOSトランジスタの第2のソース/ドレイン領域の上面の面積は、第1又は第2のMOSトランジスタの柱状半導体層のそれぞれの上面の面積よりも大きく、第1のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部と第2のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部とを接続するシリサイド層が形成される。

(もっと読む)

1 - 20 / 58

[ Back to top ]