Fターム[5F048BE09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077) | ウェルに電圧印加 (892)

Fターム[5F048BE09]に分類される特許

161 - 180 / 892

半導体装置およびその製造方法

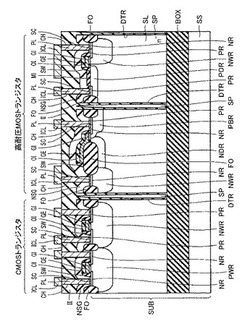

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置、及びその製造方法

【課題】半導体デバイスにおいて、ラッチアップ耐性を維持するとともに、チップ面積を縮小する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、トレンチ2が形成されたシリコン基板(Nウェル8、Pウェル9)と、トレンチ2の側面からシリコン基板表面にかけて、ウェルと同じ導電型で、当該ウェルより高濃度で形成された不純物領域(N型ウェルコンタクト拡散層領域4、P型ウェルコンタクト拡散層領域6)と、を備える。

(もっと読む)

半導体装置

【課題】ショットキー電極を設けなくても閾値が低く、高耐圧化が可能な半導体装置を提供する。

【解決手段】N+型のカソード層1が、カソード電極100に接合して形成され低不純物濃度のN型のドリフト層2が、カソード層1に接合して形成され、複数のトレンチ4a、4bが、ドリフト層2の上面に所定の間隔を隔てて配列され、埋め込み電極5a、5bが、トレンチ4a、4bの内部に、絶縁膜6a、6bを介してそれぞれ形成され、トレンチ間領域7隣り合うトレンチ間に形成され、高不純物濃度のP+層31および高不純物濃度のN+層32を交互に配列してアノード電極200に接合させたユニバーサルコンタクト層3が、トレンチ間領域7に接合して形成される。トレンチ間領域7の熱平衡状態のポテンシャルが調整されて、ドリフト層2の熱平衡状態のポテンシャルとの差が、使用する半導体材料のバンドギャップに依存するビルトイン電圧よりも低い。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

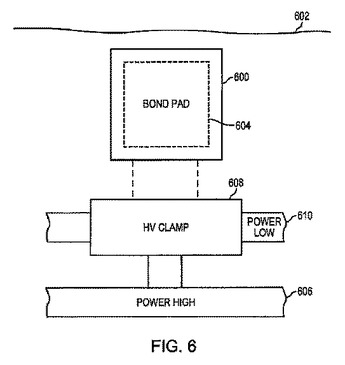

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の大きな増加なく、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護素子を得ることを目的とする。

【解決手段】 素子分離にシャロートレンチ構造を有するESD保護素子を有する半導体装置において、ESD保護素子は、中央に外部接続端子からの信号を受けるN型の領域が配置され、外部接続端子からの信号を受けるN型の領域の側面ならびに底面を囲むようにP型の領域が配置され、P型の領域の側面および底面を囲むように埋め込みN型の領域が配置され、埋め込みN型の領域の周囲にP型の基板端子領域が配置され、P型の基板端子領域の周囲にトレンチ分離領域が配置された半導体装置とした。

(もっと読む)

半導体装置及びその製造方法

【課題】高性能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の一態様は、Si基板1a上に形成された絶縁層1bと、前記絶縁層上に形成された第1のSOI層1cと、前記第1のSOI層により形成されたバックゲート電極1c'と、前記バックゲート電極上に形成されたバックゲート絶縁層7aと、前記バックゲート絶縁層上に形成された第2のSOI層3と、前記第2のSOI層上に形成されたフロントゲート絶縁層と、前記フロントゲート絶縁層上に形成されたフロントゲート電極10と、前記第2のSOI層に形成されたソース領域及びドレイン領域それぞれの不純物層と、前記バックゲート電極に電気的に接続された第1の配線16aと、前記フロントゲート電極に電気的に接続された第2の配線16bと、を具備することを特徴とする半導体装置である。

(もっと読む)

スイッチング装置

【課題】寄生容量が低減し、ラッチアップ耐性が向上したスイッチング装置を提供する。

【解決手段】半導体層と、前記半導体層の表面に選択的に形成され、ソース領域とドレイン領域とが表面に選択的に形成された第1のウェル領域と、前記半導体層と前記第1のウェル領域との間に形成された第2のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された、第1の入出力端子と、前記ドレイン領域に接続された、第2の入出力端子と、前記第1の入出力端子と前記第2のウェル領域との間に接続された第1の容量素子と、前記第1の容量素子とグランド電位との間に接続された第2の容量素子と、を備えたことを特徴とするスイッチング装置が提供される。

(もっと読む)

トランジスタ型保護素子および半導体集積回路

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、エミッタ領域5B、第1コレクタ領域6B、第2コレクタ領域8Bおよび抵抗性接続領域9を有する。第1および第2コレクタ領域6B,8Bは、エミッタ領域5Bと所定の距離以上だけ離れ、お互いの間も互いに離れており、その間が抵抗性接続領域9によって接続されている。抵抗性接続領域9は薄膜抵抗層によって代替できる。

(もっと読む)

半導体装置、二次電池保護装置および半導体装置の製造方法

【目的】特性が改善された半導体装置および充放電制御装置を提供することにある。また、低コストであり生産性が向上された半導体装置の製造方法を提供することである。

【解決手段】トレンチ3の両側壁に形成する2つのMOSFETにおいて、1つのMOSFETの第1pベースピックアップ領域41の配置間隔を別のMOSFETの第2pベースピックアップ領域51の配置間隔に比べて広くする。

前記第1pベースピックアップ領域41および第2pベースピックアップ領域51を形成する際のレジストマスク63をトレンチ3に隣接する第1pベース領域4および第2pベース領域を覆うように形成して、不純物のイオン注入を行う。

(もっと読む)

静電気放電保護回路

【課題】サージ放電用のMOSトランジスタの駆動能力を向上できる静電気放電保護回路を提供する。

【解決手段】この静電気放電保護回路によれば、静電気検知部3は、電源端子1とGND端子2との間に上限電圧Vmaxを超える電圧が発生したときに、第1のゲート制御部4を通電状態にして、第1の配線11からNMOSトランジスタ7のゲートへ電流を流す。これにより、ゲート電圧が上昇してNMOSトランジスタ7がオンすることでサージ電圧が放電し、第1の配線11の電圧が下降する。一方、電源端子1とGND端子2との間の電圧が上限電圧Vmax以下のときに第1のゲート制御部4を非通電状態にするので、NMOSトランジスタ7のゲートから第1のゲート制御部4を経由して第1の配線11へ電流が逆流することを防止でき、NMOSトランジスタ7のゲート電圧の降下を防止できる。

(もっと読む)

半導体装置

【課題】アバランシェ耐量のマージンが小さいスイッチング素子のジャンクション又はチャネルの温度が上昇した場合であっても、過電圧を印加されたときの降伏によってスイッチング素子が破壊されるのを防止することが可能な半導体装置を提供する。

【解決手段】縦型のMOSFETからなる保護トランジスタ20は、半導体基板2の一面にゲート電極23及びソース電極22を、他面にドレイン電極21を形成してある。出力トランジスタ10が形成された半導体基板1の一面に存するソース電極12と、半導体基板2の一面とを導電性の接着剤6で接着して、ソース電極12にソース電極22及びゲート電極23を電気的に接続し、熱的に密結合させる。ドレイン電極11,21同士はリード線32で接続する。高温の場合、保護トランジスタ20は、閾値が0V以下に低下してオンし、出力トランジスタのアバランシェ電流の一部又は全部を分担する。

(もっと読む)

半導体装置の製造方法

【課題】 ダイオードとIGBTを有する半導体装置において、量産時にダイオードの特性、及び、IGBTの特性にばらつきが生じ難い半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体ウェハの下面の半導体層のうちIGBT領域の部分を薄くすることで、IGBT領域の半導体ウェハの厚みをダイオード領域の半導体ウェハの厚みよりも薄くして半導体ウェハの下面に段差を形成する段差形成工程と、段差形成工程後に、半導体ウェハの下面側から半導体ウェハの下面全体に荷電粒子の照射を行って、IGBT領域に照射された荷電粒子が半導体ウェハを通過する一方でダイオード領域に照射された荷電粒子が半導体ウェハに停止することで、ダイオード領域内の半導体ウェハに結晶欠陥密度のピークを形成する結晶欠陥形成工程とを含む。半導体ウェハの下面の半導体層のうちIGBT領域の部分を薄くすることは、半導体ウェハに素子構造を形成する方法と同様の方法で行うことができ、その精度は高い。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置

【課題】耐圧を確保すると共に、回路を構成する面積の増大を抑えることのできる半導体装置の静電保護回路を提供する。

【解決手段】静電保護回路は、第1の導電型のウエル64内に形成された第2の導電型の領域であるドレイン68を一部の外部端子に接続され、ゲート74と第1の導電型のウエル64内に形成された第2の導電型の領域であるソース66を共通接続された第1のMOSトランジスタと、第1の導電型のウエル84内に形成された第2の導電型の領域であるドレイン88を第1のMOSトランジスタのゲートとソースに共通接続され、ゲート94と第1の導電型のウエル84内に形成された前記第2の導電型の領域であるソース86を電源端子56に共通接続された第2のMOSトランジスタとを有し、それぞれのMOSトランジスタは、ドレインをコレクタとしウエルをベースとし、ソースをエミッタとする寄生トランジスタを形成する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

161 - 180 / 892

[ Back to top ]