Fターム[5F048CA01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | バイポーラトランジスタの構造 (853) | ウェル内に形成 (89)

Fターム[5F048CA01]に分類される特許

1 - 20 / 89

半導体装置の製造方法

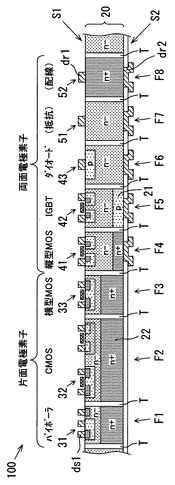

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

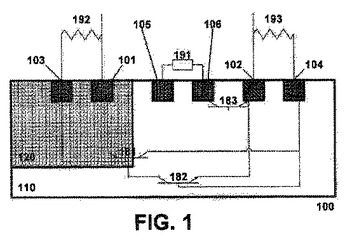

高保持電圧デバイス

高保持電圧(HVO静電放電(ESD)保護回路が、シリコン制御整流器(SCE)デバイスと、SCRデバイスの保持電圧を高める、SCRデバイスのアノードとカソードとの間の長さ(LAC)内に設置された補償領域とを備える。補償領域は、負のフィードバック機構をSCRデバイスに導入することで、SCRのループゲインに影響を及ぼし、高保持電圧で回生フィードバックに達しうる。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】従来に比べて更に保護能力を高めた保護素子を含む半導体装置を提供する。

【解決手段】P型ウェル2内にはP型領域4,N型領域5aが、N型ウェル3内にはP型領域7a,N型領域8がそれぞれ形成され、両ウェル2及び3にまたがってN型領域6が形成されている。N型領域5aはN型ウェル3より不純物濃度が高く、N型領域6,8はそれよりも更に高い。P型領域7aはP型ウェル2より不純物濃度が高く、P型領域4はそれよりも更に高い。N型領域5aの上層には、不純物濃度がN型領域5aより高く、N型領域6,8と同程度のN型ドープトポリシリコン膜11がN型領域5aに接触して形成されている。P型領域7aの上層には、不純物濃度はP型領域7aより高く、P型領域4と同程度のP型ドープトポリシリコン膜12がP型領域7aに接触して形成されている。

(もっと読む)

半導体装置

【課題】製造後に電流増幅率hFE特性を変化させることができるバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】P型半導体層1に、N型拡散層からなるコレクタ3、P型拡散層からなるベース5、N電型拡散層からなるエミッタ7が形成されてバイポーラトランジスタが形成されている。そのバイポーラトランジスタはベース5上及びコレクタ3にゲート絶縁膜9を介してゲート電極11を備えている。コレクタ3にはコレクタ配線13が接続されている。ベース5にはベース配線15が接続されている。エミッタ7にはエミッタ配線17が接続されている。ゲート電極11にはゲート電極配線19が接続されている。配線13,15,17,19は互いに電気的に絶縁されている。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

半導体装置

【課題】ESD耐量の高い半導体装置を提供する。

【解決手段】半導体基板表面に設けられた半導体基板よりも不純物濃度が高いPW層24と、半導体基板表面にPW層24と接して設けられた半導体基板よりも不純物濃度が高いNW層23と、PW層24内の半導体基板表面に設けられたPW層24よりも不純物濃度が高いp+ベース層5と、NW層23内の半導体基板表面に設けられたNW層よりも不純物濃度が高いn+コレクタ2層と、p+ベース層5とn+コレクタ層2の間に位置しPW層24内の半導体基板表面に設けられたPW層24よりも不純物濃度が高いn+エミッタ層6と、n+コレクタ層2とPW層24の間にn+コレクタ層2と接して設けられたn+コレクタ層2より不純物濃度が低くNW層23より不純物濃度が高いn±層10を有する半導体装置とした。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体集積回路

【課題】寄生容量が小さく、かつ、信号波形の歪み発生を防止または抑制した保護素子をIC内に実現する。

【解決手段】内部回路2と、その保護素子3とを同一半導体基板に有する。保護素子3は、アノード同士が共通接続されて浮遊ノードを形成した2つのダイオードD1,D2を有し、これがウェル・イン・ウェル構造に形成されている。このウェル・イン・ウェル構造は、浮遊ゲートを形成するP型ウェルと、P型ウェルを包含し、一方のダイオードのカソードと同電位のN型ウェルと、P型ウェル内に形成された、他方のダイオードのカソードと同電位の第1のN型領域と、を有して構成されている。

(もっと読む)

CMOSデバイスの製造方法

【課題】 CMOSデバイスのプロセスで、副産物的に作成できる縦型PNPトランジスタ等のバイポーラトランジスタに有効利用する。

【解決手段】 N―MOSトランジスタは、P型ウエル32−1にドレイン領域37、ソース領域38、及びチャネルストッパー39として形成される。P−MOSトランジスタは、半導体基板31−1の表面に、ドレイン領域40、ソース領域41、及びチャネルストッパー42として形成される。チャネルストッパー42と同時に、すなわち同じ工程で、p型ウェル32−2にはバイポーラトランジスタを形成するベース領域43が形成される。また、P−MOSトランジスタのドレイン/ソース領域40,41と同時に、バイポーラトランジスタのエミッタ領域49及びコレクタ領域の電極取り出し部48が形成される。

(もっと読む)

半導体装置

【課題】制御電極層のない素子のレイアウトサイズを増加させることなく、CMPによる平坦化での過研磨を防ぐことができる半導体装置を提供すること。

【解決手段】半導体基板上に配されるとともに拡散層で構成された拡散層抵抗7と、拡散層抵抗7の外周を囲むように配されるとともに拡散層で構成されたPウェルコンタクト6と、Pウェルコンタクト6の外周を囲むように配されるとともに拡散層で構成されたNウェルコンタクト4と、を備えた抵抗セルを有する半導体装置であって、Pウェルコンタクト6及びNウェルコンタクト4は、それぞれ複数に分断されており、隣り合うPウェルコンタクト6間の領域に制御電極層9bが配されてPウェルコンタクト6と制御電極層9bが交互に配置され、隣り合うNウェルコンタクト4間の領域に制御電極層9aが配されてNウェルコンタクト4と制御電極層9aが交互に配置されている。

(もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

半導体装置とその製造方法

【課題】 エミッタ注入効率が大きく、差動増幅回路の入力トランジスタとして利用可能で、かつBi−CMOSプロセスにおいてMOSトランジスタと同一基板上に搭載することが可能なバイポーラトランジスタの構造とその製造方法を提供する。

【解決手段】 半導体基板1上に第二導電型の深いウェル層2が形成され、深いウェル層2よりは浅い所定の深さで第一導電型の埋め込み層3が形成され、バイポーラトランジスタのエミッタ領域が、第一導電型の埋め込み層3の上に、第二導電型のウェル層4、及びMOSトランジスタのソース・ドレイン領域と同時形成される高濃度の第二導電型の不純物層15の2層構造として形成されている。

(もっと読む)

1 - 20 / 89

[ Back to top ]