Fターム[5F048CA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | バイポーラトランジスタの構造 (853) | 単層基板上に形成 (54)

Fターム[5F048CA02]に分類される特許

1 - 20 / 54

基準電圧回路及び半導体基板

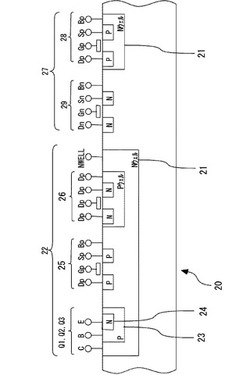

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】 サブ素子部のコンタクト部において、電流集中が生じ難い半導体装置を提供する。

【解決手段】 メイン素子部20とサブ素子部40が形成されている半導体基板12を有する半導体装置であって、半導体基板12の上面のうち、メイン素子部20の上面にはメイン電極66が形成されており、サブ素子部40の上面には互いに分離されている複数のコンタクト部69を介して半導体基板12と導通しているサブ電極68が形成されており、前記複数のコンタクト部69は、第1方向に沿って伸びる直線状に形成されているとともに、前記第1方向と直交する第2方向に沿って配列されており、前記複数のコンタクト部69が形成されている領域のうちの前記第2方向の少なくとも一方の端部近傍において、各コンタクト部69の第1方向の長さが、その端部から前記領域の中央に向かうにつれて長くなっている。

(もっと読む)

半導体装置

【課題】ESD耐量の高い半導体装置を提供する。

【解決手段】半導体基板表面に設けられた半導体基板よりも不純物濃度が高いPW層24と、半導体基板表面にPW層24と接して設けられた半導体基板よりも不純物濃度が高いNW層23と、PW層24内の半導体基板表面に設けられたPW層24よりも不純物濃度が高いp+ベース層5と、NW層23内の半導体基板表面に設けられたNW層よりも不純物濃度が高いn+コレクタ2層と、p+ベース層5とn+コレクタ層2の間に位置しPW層24内の半導体基板表面に設けられたPW層24よりも不純物濃度が高いn+エミッタ層6と、n+コレクタ層2とPW層24の間にn+コレクタ層2と接して設けられたn+コレクタ層2より不純物濃度が低くNW層23より不純物濃度が高いn±層10を有する半導体装置とした。

(もっと読む)

サージ保護素子

【課題】 ブレークダウン電圧を調整可能であり、かつ、小型なサージ保護素子を提供する。

【解決手段】 半導体基板12の表面に露出している第1導電型の第1領域26と、半導体基板12の表面に露出しており、第1領域26と隣接している第2導電型の第2領域24と、半導体基板12の表面に露出しており、第2領域24と隣接しており、第2領域24によって第1領域26から分離されている第1導電型の第3領域22と、第1領域26の表面に形成されている第1電極32と、第3領域の表面に形成されている第2電極30と、第1電極32と第2領域24の間の第1領域26の表面に形成されている絶縁膜34と、絶縁膜34上に形成されているブレークダウン制御電極36を有していることを特徴とするサージ保護素子20。

(もっと読む)

静電気保護素子

【課題】表示パネル駆動用の半導体集積装置に適した、保持電圧が高い静電保護素子を提供する。

【解決手段】静電保護素子は、P型半導体基板1の表面側に形成されたNウェル領域2と、Nウェル領域の上に形成された第1のP型高濃度不純物領域8と、P型半導体基板の表面上に形成されたN型高濃度不純物領域5と、Nウェル領域とP型半導体基板1との境界を跨いでNウェル領域と前記P型半導体基板との双方に接触して形成された第2のP型高濃度不純物領域6とを備えている。すなわち、第2のP型高濃度不純物領域6がP型半導体基板1と接触するため、P型半導体基板1におけるP型不純物の濃度が高くなり、従って静電気保護素子の保持電圧が高くなる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】同一の半導体基板上に数種類のトランジスタを簡易なプロセスによって形成する半導体装置の製造方法の提供。

【解決手段】LDMOS領域100とオフセットドレインMOS領域200とに、同時に、第2導電型の第1ウェル30を形成する工程と、LDMOS領域100の第1ウェル30と、CMOS領域100とに、同時に、第1導電型の第2ウェル32を形成する工程と、CMOS領域300に、第2導電型の第2ウェル34を形成する工程と、オフセットドレインMOS領域200に第1導電型のオフセット層22を形成する工程とを含み、第1ウェル30は、第2ウェル32,34よりも深いウェルであり、第2ウェル32,34は、高エネルギーイオン注入法によって形成されたレトログレードウェルである、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

半導体装置

【課題】絶縁ゲートバイポーラトランジスタのスイッチング特性および低オン抵抗を維持しつつ耐圧特性を改善しかつ占有面積を低減する。

【解決手段】絶縁ゲートバイポーラトランジスタ(IGBT:2)のターンオフ時のホール流入を抑制するPチャネルMOSトランジスタ(PQ)のゲート電極ノード(6)に対し、IGBTのオフ状態時においてゲート絶縁膜に印加される電圧を緩和する電圧緩和素子(1)を設ける。

(もっと読む)

半導体装置、及び該半導体装置を用いたエネルギー伝達装置

【課題】ドレイン電極をソース電極に対して負バイアスすることがあっても、半導体集積回路においてラッチアップが発生することを防止できるエネルギー伝達装置、及び該エネルギー伝達装置を実現可能な半導体装置を提供する。

【解決手段】第1の半導体基板に形成された半導体装置24と、第2の半導体基板の表面に形成された第2導電型の逆電流防止層、及び第2の半導体基板中に形成され逆電流防止層を覆う第1導電型のウェル層を含む逆電流防止ダイオード41を備えた半導体集積回路48と、直流電圧源52と、変圧器60とを備え、変圧器60は、半導体装置24及び直流電圧源52と直列に接続される一次巻線53と、負荷と接続される第1二次巻線54とを含み、変圧器60の第1二次巻線54から負荷へ電力が供給されるように構成されている。半導体装置24の第2ドレイン電極(TAP電極)は、半導体集積回路48の逆電流防止層と電気的に接続している。

(もっと読む)

半導体装置およびその製造方法

【課題】 CMOS製造プロセスを使用しても、バイポーラトランジスタの適切な駆動能力や温度特性を得ることが可能な半導体装置を提供する。

【解決手段】 縦型バイポーラトランジスタ90aとMOSトランジスタ90bからなる構成であって、縦型バイポーラトランジスタの少なくともベース領域は、エッチングにより表面から掘り下げることでMOSトランジスタ90bのウェル20b深さよりも浅くなっている。このためバイポーラトランジスタに必要とされる特性を独立さえて作り込むことが可能である。

(もっと読む)

金属−絶縁体転移(MIT)素子の自己発熱防止回路、及びその防止回路用の集積素子の製造方法

MIT素子の自己発熱問題を解決できるMIT素子の自己発熱防止回路、及びその防止回路用の集積素子の製造方法を提供する。該自己発熱防止回路は、所定の臨界温度以上で急激なMITが発生し、電流駆動素子に連結されて電流のフローを制御するMIT素子と、MIT素子に連結されて、MIT以後にMIT素子の自己発熱を制御するトランジスタと、MIT素子及びトランジスタに連結された抵抗素子と、を備える。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】1つの半導体基板に少なくとも両面電極素子を含む複数の素子が形成された構成において、素子特性の異なる複数の素子を集積でき、且つ、割れを抑制することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板と、半導体基板における複数の素子形成領域をそれぞれ取り囲むとともに、半導体基板を貫通して複数の素子形成領域を互いに絶縁分離する絶縁分離トレンチと、複数の素子形成領域のそれぞれに構成される素子と、を備える半導体装置において、互いに厚さの異なる複数の厚さ領域を半導体基板に構成した。そして、複数の厚さ領域のうち、最も厚さの薄い領域を含む少なくとも2つの厚さ領域に素子形成領域をそれぞれ形成し、素子として少なくとも両面電極素子を含み、この両面電極素子が少なくとも最も厚さの薄い領域に形成される構成とした。

(もっと読む)

半導体装置及びその駆動方法

【課題】低電源で駆動でき、しかも高利得が得られる半導体装置及びその駆動方法を提供する。

【解決手段】第1半導体領域11及び第2半導体領域10が接合面30a,30bで隣り合い、電位障壁を構成するpn接合体と、前記接合面の近傍で前記第1半導体領域11に絶縁体12を介して接続される第1電極22と、前記第1半導体領域11に接続される第2電極21と、前記第2半導体領域に接続される第3電極20と、を備える。前記第2電極21と前記第3電極20との間に順方向バイアスを印加すると、前記接合面に対応して前記電位障壁が低下する。前記第1電極22と前記第2電極21との間に電位差を与えることにより、前記電位障壁が変化し、前記第1半導体領域11は、前記絶縁体13との境界の表層に、表面近傍領域が、駆動電流を流すチャネル31として形成される。その結果、半導体装置は、トランジスタとして駆動され得る。

(もっと読む)

1 - 20 / 54

[ Back to top ]