Fターム[5F048DA28]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | ゲート側壁(サイドウォール) (5,329) | 材料 (3,524) | 多結晶Si (29)

Fターム[5F048DA28]に分類される特許

1 - 20 / 29

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】本発明の目的は、さらに精度良く微細な複数のメモリセルと、高性能な複数のトランジスタと、を形成しつつ、複数の工程を1つの工程に集約させることを可能にする、不揮発性半導体記憶装置とその製造方法を提供するものである。

【解決手段】シリコン基板上に、ゲート絶縁膜用膜と浮遊ゲート電極膜用膜とゲート電極間絶縁膜用膜と制御ゲート電極膜用膜と、を積層し、制御ゲート電極膜用膜をエッチングして、同一の幅を有する複数の制御ゲート電極膜を形成する。この複数の制御ゲート電極膜の任意の数のもの毎を、それぞれトランジスタ単位となし、各トランジスタ単位におけるゲート電極間絶縁膜と浮遊ゲート電極膜とゲート絶縁膜とを形成する。各トランジスタ単位において、複数の制御ゲート電極膜に沿って形成したコンタクトホールに、コンタクトを埋め込んで、トランジスタを形成する。

(もっと読む)

電気的にプログラムされたソース/ドレイン直列抵抗を有するMOSトランジスタ

【課題】高速度MOSFETを形成するための半導体デバイス技術が要請されている。

【解決手段】トランジスタゲートサイドウォールスペーサ(27)に埋め込まれた導電層(24)を形成することによって高速MOSトランジスタ(32)は、用意される。この埋め込まれた導電層(24)は、トランジスタ(32)のゲート電極(18)とソース/ドレイン領域(28)から電気的に絶縁している。埋め込まれた導電層(24)は、ソース/ドレイン伸長領域(30)を覆うように配置され、ソース/ドレイン領域(28)直列抵抗を低くすることでソース/ドレイン伸長領域内に電荷を蓄積する。

(もっと読む)

同一ウェハ上に様々なトランジスタを集積するための方法および装置

【課題】メモリセルや、高電圧トランジスタや、高性能トランジスタなどの、異なるタイプのトランジスタを、同一基板上に形成することが可能なフラッシュメモリ等の半導体装置を提供する。

【解決手段】高電圧トランジスタは、誘電膜20で覆われた第1のポリシリコン層22により形成される。誘電膜20上の第2のポリシリコン層24は、トランジスタのゲート22上に側壁スペーサ24を形成するためにエッチングされる。側壁スペーサ24は、ソースおよびドレイン32を形成し、そして、サブリソグラフィックな軽度にドープされたドレイン34を画定するために使用される。スペーサ24を取り除いた後、下地の誘電膜20は、軽度にドープされたドレイン34を保護することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧の絶対値が互いに異なる複数のMISトランジスタが用いられる場合において、しきい値電圧の絶対値が大きい方のMISトランジスタの駆動電流の低下を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】第2のnMISトランジスタT2nのしきい値電圧は、第1のnMISトランジスタT1nのしきい値電圧よりも大きく、第2のnMISトランジスタT2nが有する第2のnMIS高誘電率膜H2nにおけるランタン原子濃度およびマグネシウム原子濃度の和は、第1のnMISトランジスタT1nが有する第1のnMIS高誘電率膜H1nにおけるランタン原子濃度およびマグネシウム原子濃度の和よりも小さい。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

複数のトランジスタゲートの形成方法、および少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートの形成方法

少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートを形成する方法は、異なる幅を有する基板上に第一および第二のトランジスタゲートを形成するステップを含み、第一の幅は第二の幅よりも狭い。材料は、第一および第二のゲート上を含む基板上に堆積される。エッチングチャンバー内で、材料は、第一および第二のゲートの双方の上からエッチングされ、第一のゲートの導電性材料を露出し、第二のゲート上に支持された材料の厚さを減少させ、材料によって被覆された第二のゲートをそのまま残す。エッチング後に、エッチングチャンバー内のそのままの位置で、基板は少なくとも300℃の基板温度で金属を含むプラズマに対して暴露され、第二のゲートの仕事関数と比較して、第一のゲートの仕事関数を改変するために、第一のゲートへと金属を拡散させる。  (もっと読む)

(もっと読む)

半導体装置の作製方法

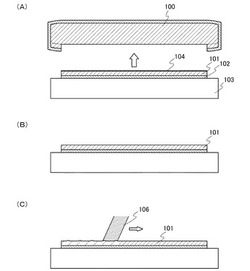

【課題】ガラス基板と単結晶半導体基板とを貼り合わせてSOI基板を作製する際の縞状の模様(むら)の発生を抑制することを目的の一とする。又は、上記むらの発生を抑えて高品位な半導体装置を提供することを目的の一とする。

【解決手段】単結晶半導体基板に加速されたイオンを照射して単結晶半導体基板に脆化領域を形成し、単結晶半導体基板に形成された絶縁層の表面の、単結晶半導体基板の周縁部に対応する領域に、凹部又は凸部を形成し、絶縁層を介して、単結晶半導体基板とベース基板とを貼り合わせ、熱処理を施すことにより、脆化領域において単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を形成し、単結晶半導体層をパターニングして半導体素子を形成する際に、周縁部に対応する領域の単結晶半導体層を除去する。

(もっと読む)

半導体装置の作製方法

【課題】結晶粒の大きさばらつきを低減し、均質な半導体膜を提供することを目的の一とする。又は、均質な半導体膜を提供すると共に、低コスト化を図ることを目的の一とする。

【解決手段】非晶質半導体膜を形成したガラス基板を、結晶化に必要な温度以上の処理雰囲気内に導入することにより、処理雰囲気からの熱伝導による急速加熱を行って、非晶質半導体膜を結晶化させる。より具体的には、例えば、あらかじめ処理雰囲気の温度を結晶化に必要な温度まで上昇させた後、半導体膜が形成された基板を上記処理雰囲気に投入する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】良好な結晶性を有し、S値において高性能な半導体素子を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再単結晶化し、結晶欠陥を修復する。次いで、n型トランジスタとなる島状単結晶半導体層にフォトマスクを用いてチャネルドープし、次いで該フォトマスクを用いて島状単結晶半導体層をエッチバックし、p型トランジスタとなる島状単結晶半導体層の膜厚より薄くなるようにする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、これらの問題を解決するためになされたもので、半導体装置の微細化に影響することなく、同一基板上で異なる極性の領域において各々の特性を向上させる処理が可能な半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明による半導体装置の製造方法は、第1領域全体と第2領域全体とを全面に覆うサイドウォール下地膜9を形成する工程と、サイドウォール下地膜9上であって第1ゲート構造および第2ゲート構造の側面にサイドウォール膜10を形成する工程と、第1領域全体と第2領域全体とを全面に覆うカバー膜11を形成する工程と、第2領域において、サイドウォール下地膜9およびカバー膜11を除去し、サイドウォール膜10に覆われたサイドウォール下地膜9のみ残す工程とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソースドレイン部のシリサイド化およびゲート電極のフルシリサイド化を1回で行うとともに、CMP処理によるサイドウォールの後退を防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、SOI層3上にゲート絶縁膜4を介してゲート電極を形成し、ゲート電極両側のSOI層3上にエピタキシャル層9を形成する。ゲート電極を覆うCMPストッパ膜11を形成し、ゲート電極の側面においてCMPストッパ膜11上にサイドウォール12を形成する。エピタキシャル層9にソースドレイン部10,13を形成した後、これらの構造上にアモルファスシリコンからなる層間膜を形成し、CMPストッパ膜11表面に達するまで、CMP処理により層間膜を除去する。ポリシリコン膜の上部をエッチングした後、ゲート電極の全部と、ソースドレイン部10,13の上部とを同時にシリサイド化し、フルシリサイドゲート電極17を得る。

(もっと読む)

半導体装置及びその作製方法

【課題】セルフヒーティングによる誤動作を低減し、より安定した動作を確保することができる信頼性の高い半導体装置を提供する。

【解決手段】半導体素子が有する半導体膜と基板の間に、冷媒を流すための空洞を有する。該空洞は、凹部を有する絶縁膜を半導体膜と基板の間に設けることで形成される。そして該絶縁膜は、空洞内へ冷媒を導入するための開口部と、空洞内から冷媒を排出するための開口部とを少なくとも有する。一方の開口部から導入された冷媒は、空洞内を流れ、他方の開口部から排出される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグを用いずに異なるトランジスタのゲート電極とドレイン領域とを電気的に接続することを特徴とする。

【解決手段】トレンチ型の素子分離絶縁膜12によって素子分離された複数の素子領域13と、各素子領域上に形成されると共に各素子領域に隣接する素子分離絶縁膜12上まで延長して形成され、多結晶シリコンからなる側壁膜17を有するゲート電極14と、各素子領域内に形成されたトランジスタのドレイン領域18と、素子分離絶縁膜12上に位置するゲート電極14の上部及び側壁膜17上並びに素子分離絶縁膜12に隣接する異なるトランジスタのドレイン領域18上に渡って連続して形成された金属シリサイド膜20と、金属シリサイド膜20上を含む全面上に形成された層間絶縁膜21を具備している。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

半導体装置およびその製造方法

【課題】ハロー領域により短チャネル効果を抑制し、且つ接合リーク電流の発生や接合容量の増加を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、Si基板と、前記Si基板上にゲート絶縁膜を介して形成されたゲート電極と、前記Si基板の前記ゲート電極の下方に形成されたチャネル領域と、前記チャネル領域を挟んで形成されたソース・ドレイン領域と、前記チャネル領域を挟んで形成され、導電型不純物を含まない第1のエピタキシャル成長結晶からなるエピタキシャル層と、前記チャネル領域と前記エピタキシャル層の間に形成され、導電型不純物を含む第2のエピタキシャル成長結晶からなる、前記ソース・ドレイン領域と異なる導電型のハロー領域と、を有する。

(もっと読む)

半導体装置

【課題】円柱型構造のトランジスタの特性を向上させる。

【解決手段】導電層の形成された基板において前記導電層上に形成された柱状半導体と、前記柱状半導体の周囲に形成された絶縁層と、前記絶縁層の周囲に形成された一つのトランジスタのゲート電極を有しており、ゲート電極は、仕事関数の異なる少なくとも2層以上の導電膜の積層構造により構成されていることを特徴とする半導体装置を提供することにより、上記課題を解決する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】DRAMのメモリセルを微細化して高集積化するとともに高速動作可能な半導体集積回路技術を提供する。

【解決手段】半導体装置の製造方法は、まず、ゲート電極7の上面に窒化シリコン膜8を形成し、その側面に窒化シリコンからなる第1サイドウォールスペーサ14および酸化シリコンからなる第2サイドウォールスペーサ15を形成する。次に、DRAMのメモリセル領域の選択MISFETQsにおいては接続孔19,21が第1サイドウォールスペーサ14に対して自己整合で開口され、導電体20およびビット線BLの接続部が形成される。また、DRAMのメモリセル領域以外のNチャネルMISFETQn1,Qn2およびPチャネルMISFETQp1においては、高濃度N形半導体領域16,16bおよび高濃度P形半導体領域17が第2サイドウォールスペーサ15に対して自己整合に形成される。

(もっと読む)

発振回路およびそれを備えた半導体装置

【課題】電源電圧の変動等に対する発振周波数の変化を抑制し、より安定な周波数を出力する発振回路を提供する。

【解決手段】第1の端子と第2の端子との間に接続された定電流回路と、電源電圧端子間の電位差によって周波数が変化する電圧制御発振回路と、nチャネル型トランジスタと、定電流回路によりゲートソース間電圧が一定となるpチャネル型トランジスタと、容量と、を有し、pチャネル型トランジスタのソースは第1の端子に、ドレインはnチャネル型トランジスタのドレインおよびゲートに接続され、nチャネル型トランジスタのソースは第2の端子に、ゲートは容量を介して第2の端子に接続される発振回路により、安定な周波数を出力する。

(もっと読む)

1 - 20 / 29

[ Back to top ]